芯片設(shè)計過程是一項復(fù)雜的多步驟工作,涉及從初始系統(tǒng)規(guī)格到制造的各個階段。每一步對于實現(xiàn)生產(chǎn)完全可用芯片的目標(biāo)都至關(guān)重要。

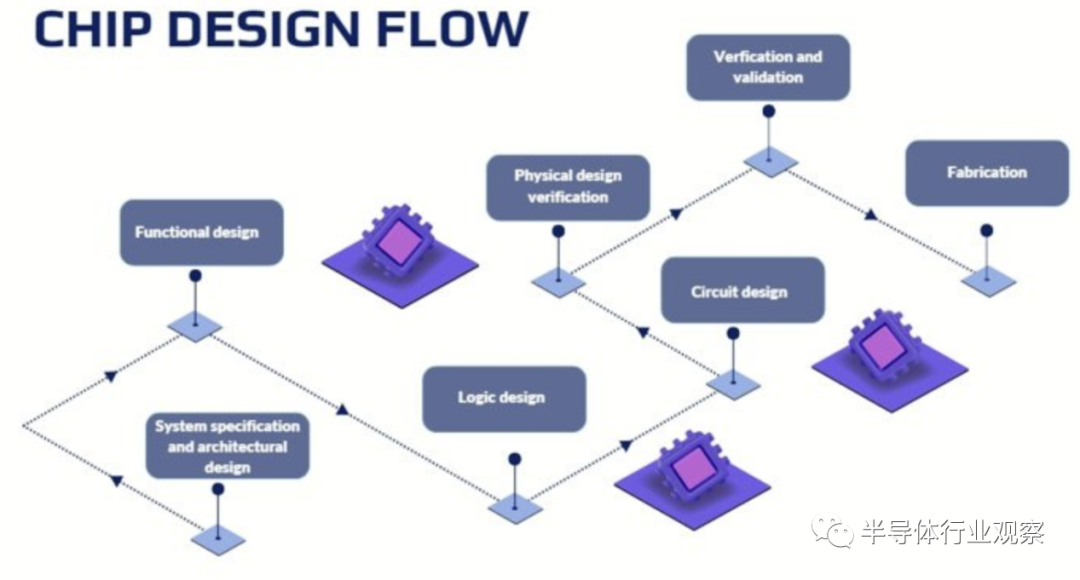

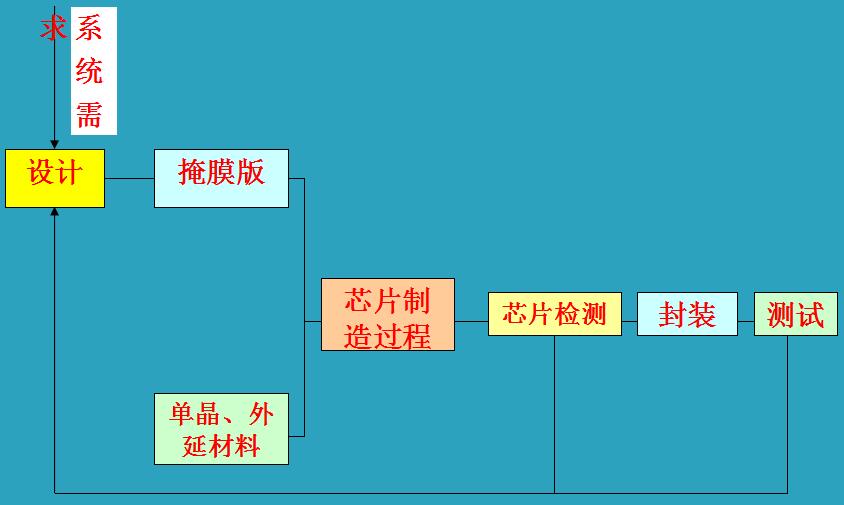

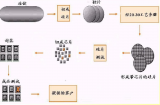

本文概述了芯片設(shè)計流程、不同階段以及它們對創(chuàng)建有效芯片的貢獻(xiàn)。這些階段包括系統(tǒng)規(guī)范、架構(gòu)設(shè)計、功能設(shè)計、邏輯設(shè)計、電路設(shè)計、物理設(shè)計驗證和制造。

任何新開發(fā)的第一步都涉及確定要設(shè)計的設(shè)備/產(chǎn)品的類型,例如集成電路 (IC)、ASIC、FPGA、SoC 等。

例如,如果目標(biāo)是為電信或網(wǎng)絡(luò)設(shè)備等高速應(yīng)用創(chuàng)建體積小但功能強(qiáng)大的產(chǎn)品,那么最好的選擇可能是專用集成電路 (ASIC)。

如果目標(biāo)是設(shè)計更靈活的東西,能夠以最小的開銷執(zhí)行多項任務(wù),那么 FPGA 可能是更好的選擇。一旦選擇了設(shè)備類型,就可以定義規(guī)格。

芯片設(shè)計理念

芯片是經(jīng)過編程以執(zhí)行特定功能的小型電子器件。這些器件用于各種應(yīng)用,包括計算機(jī)和手機(jī)。

VLSI 技術(shù)使設(shè)計人員能夠?qū)?shù)百萬甚至數(shù)十億個晶體管集成到單個芯片上,從而徹底改變了電子行業(yè)。

這導(dǎo)致了功能強(qiáng)大的處理器、存儲設(shè)備和其他先進(jìn)電子系統(tǒng)的發(fā)展。

芯片是根據(jù)其應(yīng)用要求使用不同類型的技術(shù)設(shè)計的。讓我們看看整個芯片設(shè)計過程的流程。

一、系統(tǒng)規(guī)范和架構(gòu)設(shè)計

芯片設(shè)計流程的第一步是定義芯片的要求和規(guī)格。這包括定義您的產(chǎn)品將做什么、如何使用以及您需要滿足哪些性能指標(biāo)。一旦定義了這些要求,就可以將它們用作設(shè)計架構(gòu)和布局的輸入。

確定要求后,芯片設(shè)計的下一步是創(chuàng)建滿足這些要求的架構(gòu),同時將成本和功耗保持在最低水平,以及其他考慮因素。

在芯片設(shè)計的初始階段,設(shè)計人員對架構(gòu)做出關(guān)鍵決策,例如在 RISC(精簡指令集計算機(jī))或 CISC(復(fù)雜指令集計算機(jī))之間進(jìn)行選擇,確定所需的 ALU(算術(shù)邏輯單元)數(shù)量,決定pipeline的結(jié)構(gòu)和數(shù)量、緩存大小的選擇以及其他因素。這些選擇構(gòu)成了其余設(shè)計過程的基礎(chǔ),因此設(shè)計人員仔細(xì)評估每個方面并考慮它將如何影響芯片的整體效率和性能至關(guān)重要。

這些決定是基于芯片的預(yù)期用途和定義的要求,最終目標(biāo)是創(chuàng)建高效且有效的設(shè)計,同時最大限度地降低功耗和成本。完成架構(gòu)設(shè)計階段后,設(shè)計人員創(chuàng)建微架構(gòu)規(guī)范 (MAS:Micro-Architectural Specification),這是對芯片架構(gòu)的書面描述。該規(guī)范使設(shè)計人員能夠準(zhǔn)確預(yù)測設(shè)計的性能、功耗和裸片尺寸。

通過創(chuàng)建全面的 MAS,設(shè)計人員可以確保芯片滿足初始設(shè)計階段確定的要求和規(guī)范。全面的 MAS 對于避免后期過程中的錯誤以及確保芯片設(shè)計滿足所需的性能標(biāo)準(zhǔn)和時間表至關(guān)重要。這可能涉及在不同的處理器類型或 FPGA(現(xiàn)場可編程門陣列)之間進(jìn)行選擇。

二、功能設(shè)計

接下來是功能設(shè)計。它涉及定義芯片的功能和行為。這包括創(chuàng)建系統(tǒng)需求的高級描述以及設(shè)計滿足這些需求所需的算法和數(shù)據(jù)流。這個階段的目標(biāo)是創(chuàng)建一個功能規(guī)范,可以用作其余設(shè)計過程的藍(lán)圖。

三、邏輯設(shè)計

此步驟涉及創(chuàng)建實現(xiàn)功能設(shè)計階段定義的功能所需的數(shù)字邏輯電路。此階段包括使用硬件描述語言 (HDL) 創(chuàng)建邏輯設(shè)計并使用仿真驗證設(shè)計的正確性。

四、電路設(shè)計

這個階段涉及設(shè)計芯片的物理電路,包括晶體管、電阻、電容和其他元件的選擇。電路設(shè)計階段還涉及為芯片設(shè)計電源和時鐘分配網(wǎng)絡(luò)。

五、物理設(shè)計驗證

物理設(shè)計驗證是檢查芯片物理布局的過程。這涉及識別任何設(shè)計問題并確保正確制造芯片。在此步驟中,通過邏輯仿真器、邏輯分析儀等 EDA 軟件工具以及設(shè)計規(guī)則檢查 (DRC)、布局與原理圖 (LVS) 以及時序和功耗分析等各種技術(shù)驗證集成電路布局設(shè)計,以確保正確的電氣和邏輯功能以及可制造性。

六、驗證和確認(rèn)

完成芯片設(shè)計后,就該對其進(jìn)行測試了。這稱為驗證和確認(rèn) (V&V)。V&V 涉及使用各種仿真和模擬平臺測試芯片,以確保其滿足所有要求并正常運行。如果設(shè)計中有任何錯誤,它會在這個開發(fā)階段表現(xiàn)出來。驗證還有助于確定少數(shù)最初制造的原型的功能正確性。

最后是物理版圖設(shè)計的制作。芯片設(shè)計和驗證后,.GDS 文件被發(fā)送到代工廠進(jìn)行制造。

芯片設(shè)計流程的每個階段對于創(chuàng)建成功的功能性芯片都至關(guān)重要。通過了解每個階段的要求,芯片設(shè)計人員可以創(chuàng)建高效、可靠且具有成本效益的設(shè)計,以滿足各個工業(yè)領(lǐng)域客戶的需求。

芯片設(shè)計的未來

隨著技術(shù)的進(jìn)步,芯片設(shè)計的未來是令人興奮和快速發(fā)展的。下一代芯片組通過提供更高的性能、更低的功耗和更多的功能來實現(xiàn)新時代的解決方案。這些進(jìn)步推動了許多行業(yè)的創(chuàng)新。支持新時代解決方案的下一代芯片組的一個例子是人工智能 (AI) 和機(jī)器學(xué)習(xí) (ML)應(yīng)用程序。

AI 和 ML 需要強(qiáng)大的計算能力,這可以通過先進(jìn)的芯片組實現(xiàn)。這些技術(shù)用于創(chuàng)建自動駕駛汽車、個性化醫(yī)療保健解決方案和先進(jìn)的機(jī)器人技術(shù)等。

下一代芯片組產(chǎn)生重大影響的另一個領(lǐng)域是物聯(lián)網(wǎng) (IoT) 領(lǐng)域。連接設(shè)備的激增需要功能強(qiáng)大、節(jié)能且具有成本效益的芯片組來實現(xiàn)跨各種設(shè)備的通信和數(shù)據(jù)處理。下一代芯片組也在推動 5G 網(wǎng)絡(luò)的進(jìn)步,5G 網(wǎng)絡(luò)有望提供高速、低延遲的連接,并在虛擬現(xiàn)實、增強(qiáng)現(xiàn)實和遠(yuǎn)程手術(shù)等領(lǐng)域開啟新的可能性。

芯片設(shè)計的未來一片光明,下一代芯片組將為許多行業(yè)提供更多創(chuàng)新解決方案。隨著技術(shù)的發(fā)展,我們可以期待芯片設(shè)計及其支持的解決方案出現(xiàn)更多激動人心的發(fā)展。

綜上所述,芯片設(shè)計過程復(fù)雜,包含多個步驟和階段,對行業(yè)影響重大。目前,有多種類型的芯片在使用。隨著新技術(shù)的不斷涌現(xiàn),我們總會有機(jī)會改進(jìn)我們構(gòu)建這些芯片組的方式。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19400瀏覽量

230736 -

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

26578 -

RISC

+關(guān)注

關(guān)注

6文章

465瀏覽量

83809 -

MAS

+關(guān)注

關(guān)注

0文章

16瀏覽量

10701 -

vlsi技術(shù)

+關(guān)注

關(guān)注

0文章

3瀏覽量

1572

原文標(biāo)題:芯片設(shè)計流程概要

文章出處:【微信號:moorexuetang,微信公眾號:摩爾學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

芯片設(shè)計流程概要

芯片設(shè)計流程概要

評論