存儲器是集成電路領(lǐng)城的通用器件,其市場用量巨大,從類型上分為 ROM、EPROM、E2PROM、SRAM、 DRAM、FLASH 等。半導(dǎo)體存儲器具有極其復(fù)雜的高密度的結(jié)構(gòu)和高精密時(shí)序的功能。存儲器測試技術(shù)的演變是由故障模型的變化決定的,一旦確定了存儲器設(shè)計(jì)、制造技術(shù)的故障模型集合,就可以開發(fā)適當(dāng)?shù)臏y試模式與策略。

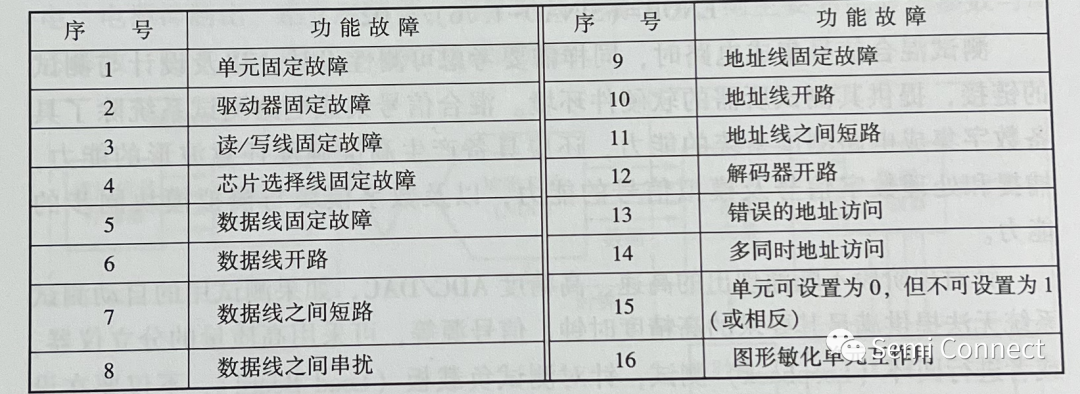

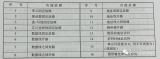

存儲器的故障可分為永久性故障和暫時(shí)性故障。表中列出了可能發(fā)生的存儲器功能故障。

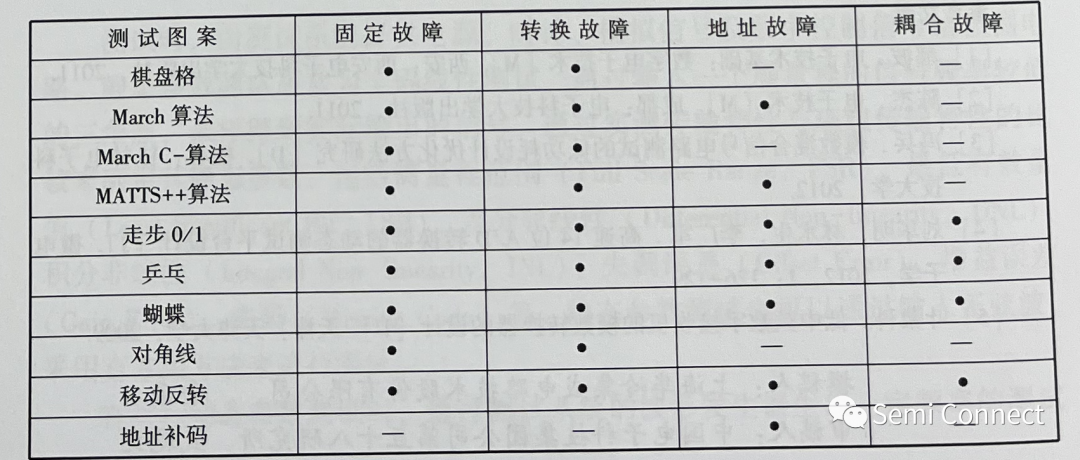

上表中列出的 16種故障可以歸并為4 類,即固定故障、轉(zhuǎn)換故障、地址故障和男合故障。存儲器測試主要采用一定的測試圖案來檢測相應(yīng)的故障,下表為目前行業(yè)內(nèi)主要采用的存儲器測試圖案與故障模型對應(yīng)關(guān)系表。

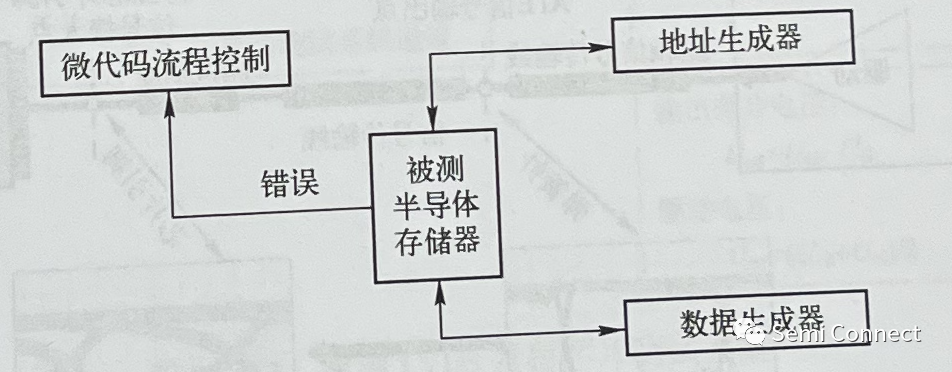

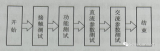

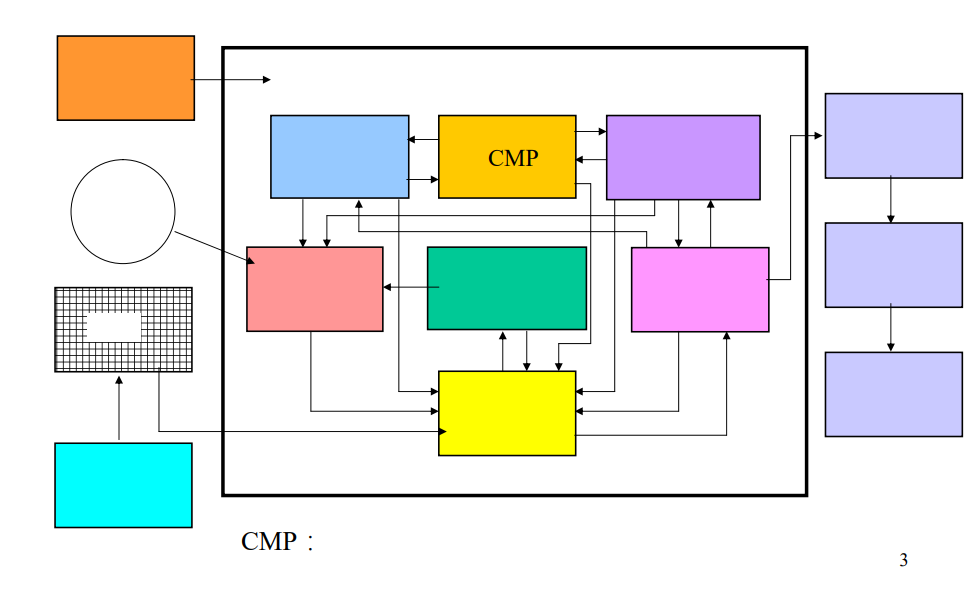

單獨(dú)的半導(dǎo)體存儲器可以利用存儲器專用測試設(shè)備進(jìn)行測試,該設(shè)備通常包含硬件算法圖形生成器 ( Algorithmnic Pattern Generator, APG),具有算術(shù)邏輯單元 (Arithmetic Logic Unit, AIU),可以實(shí)時(shí)處理地址的運(yùn)算,并且根據(jù)算法實(shí)時(shí)生成相應(yīng)測試圖案。圖所示為半導(dǎo)體存儲器專用測試設(shè)備基本架構(gòu)。

由于嵌人式存儲器不易直接測試,目的主要采用內(nèi)建自測試(BIST)解決方案。存儲器 BIST 結(jié)構(gòu)為存儲器提供激勵(lì)、數(shù)據(jù)壓縮比較能力,通常內(nèi)建冗余分析(Built-In Redundancy Analysis, BIRA)模塊或內(nèi)建自修復(fù) (Built-In Self-Repair, BISR)模塊,可以將測試結(jié)果存儲到芯片上,并具備冗余修復(fù)功能。

由于半導(dǎo)體存儲器容量越來越大,測試時(shí)間越來越長,導(dǎo)致測試成本居高不下。除BIST 內(nèi)部全速測試方案外,日前片外測試主要采用的是并行測試方案。據(jù)國際半導(dǎo)體技術(shù)路線圖組織公布,近年米 DRAM、Flash 產(chǎn)業(yè)化測試中已實(shí)現(xiàn)超過 256 個(gè)工位的并行測試。

審核編輯 :李倩

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27687瀏覽量

221418 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164179 -

生成器

+關(guān)注

關(guān)注

7文章

319瀏覽量

21080

原文標(biāo)題:存儲器集成電路測試,記憶體積體電路測試,Memory IC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

集成電路測試儀有什么類別?

TI推出微型單晶片電源管理積體電路(PMIC)系列

大容量存儲器集成電路測試

集成電路測試技術(shù)與應(yīng)用

集成電路測試儀器有哪些_集成電路測試儀組成結(jié)構(gòu)介紹

集成電路測試流程分析

集成電路IC的EMC測試標(biāo)準(zhǔn)

存儲器集成電路測試

存儲器集成電路測試,記憶體積體電路測試,Memory IC Test

存儲器集成電路測試,記憶體積體電路測試,Memory IC Test

評論