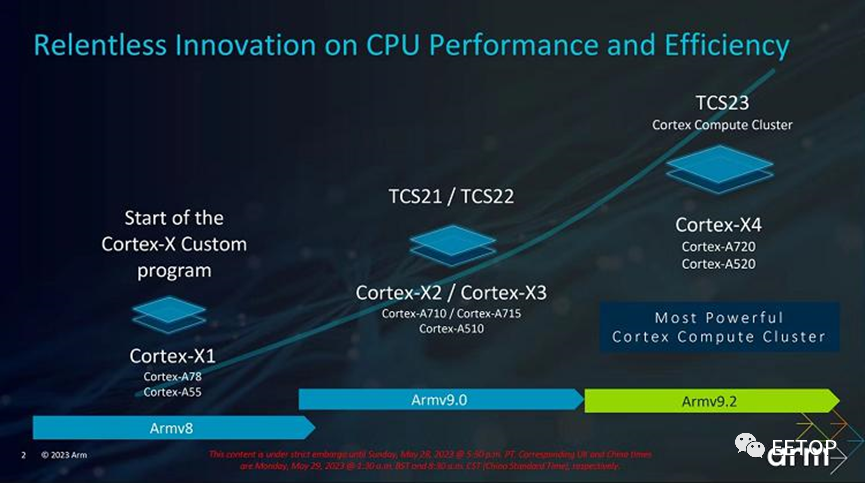

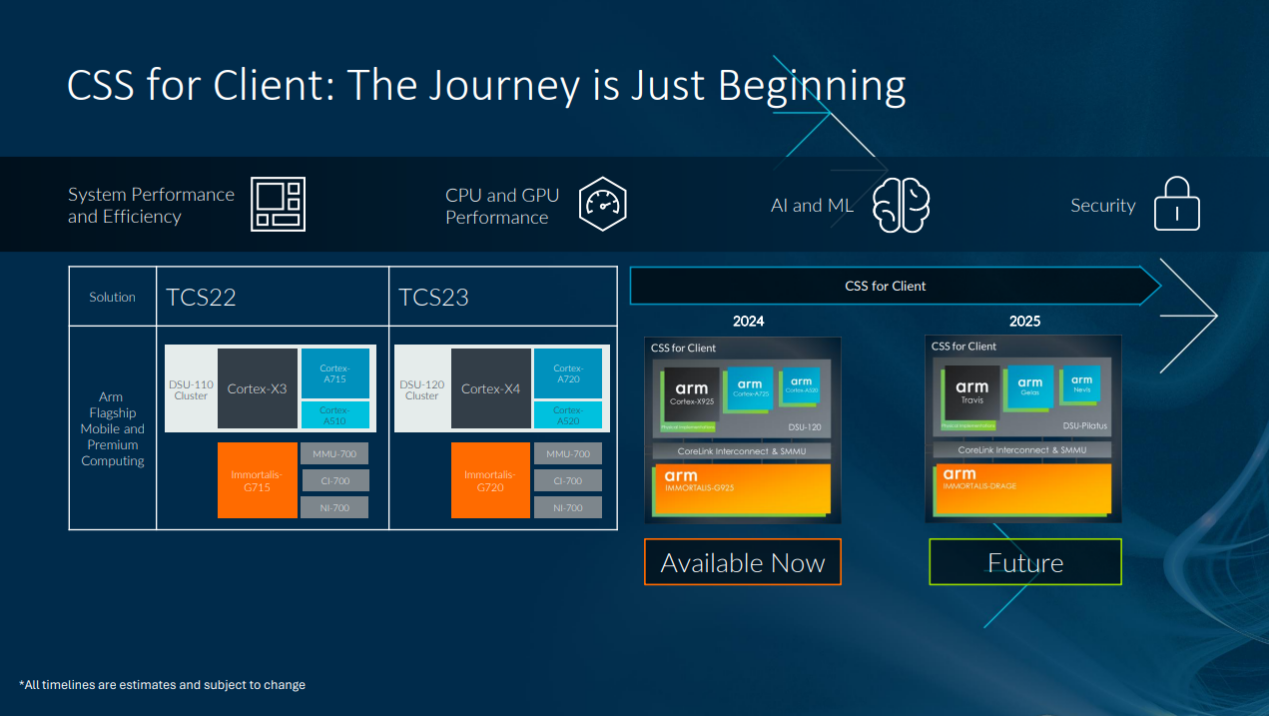

今天,ARM發布了新一代的移動處理器內核,包括Cortex-X4、Cortex-A720、Cortex-A520,預計將很快用于驍龍8 Gen 3以及天璣9300等處理器。值得一提的是,新的核心基于Arm v9.2架構,并且只支持64位指令集,不再支持32位移動應用。

Arm Cortex-X4,這是該公司的下一代旗艦性能核心,也是迄今為止設計的最高性能Arm核心。

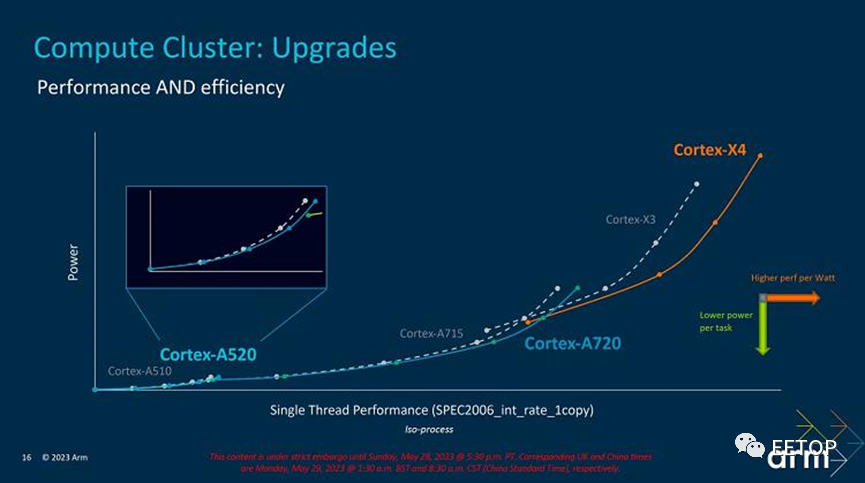

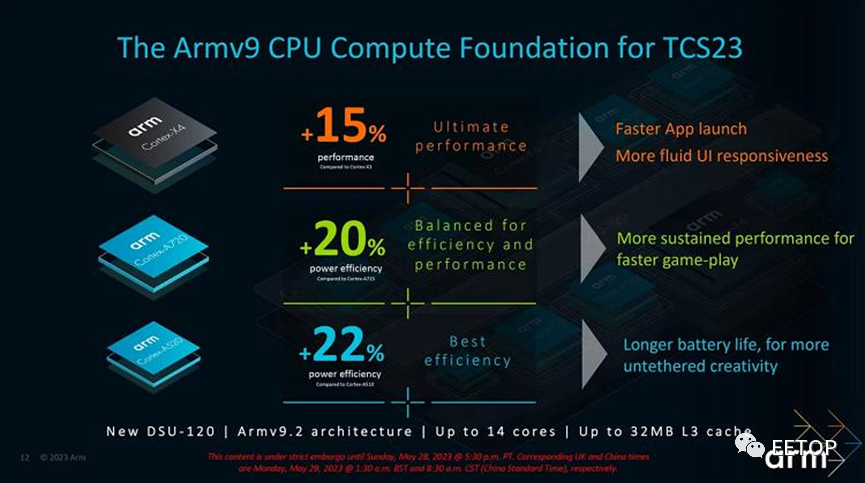

據了解,新發布的 Cortex-X4 超大核相比 Cortex-X3 在性能上提升了 15% 左右,但是在能耗方面有比較大的改善,宣稱在相同頻率下可以降低 40% 的功耗。而 A720 作為 A715 性能核心的升級迭代版本,效率提升了 20%。Cortex-A520 相比上代的 Cortex-A510 效率提升 22%。

網上此前已經爆出驍龍 8 Gen 3 采用的是 1+5+2 的叢集結構,其中 "1" 指的是 Cortex-X4 超大核,而 "5" 猜測是 Cortex-A720 性能核心,而 "3" 則是 Cortex-A520 的能效核心,安兔兔跑分更是達到了 160 萬分,相比驍龍 8 Gen 2 提升明顯。而天璣 9300 處理器預計同樣會采用 ARM 發布的新移動處理器內核,性能表現令人期待。

Arm表示,Cortex-X4的前端已經發生了一些重大變化。指令獲取傳遞已經被完全重新設計了。與Cortex-A715一樣,Cortex-X似乎也緊隨其后,也完全放棄了宏操作緩沖區。相反,Cortex-X4拓寬了流水線,支持多達10條指令。指令緩存也得到了相應的增強。帶寬增加到每周期10條指令。

新的分支預測器的準確性也得到了提高,在實際工作負載中觀察到的停滯現象明顯減少。隨著指令高速緩存和宏操作高速緩存的變化,分支預測錯誤的懲罰被統一起來,并減少到10個周期。

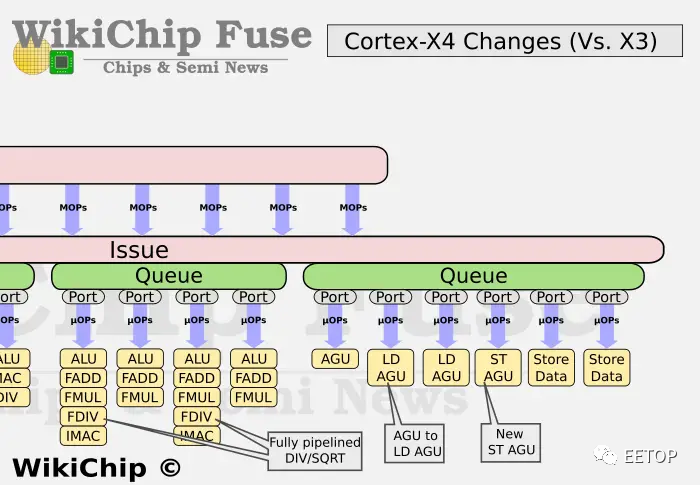

后端部分也得到了增強。在執行單元的整數方面,Arm將之前幾代的MUL單元更新為完整的MAC單元。這意味著X4現在有2個整數MAC單元。還增加了第三個分支單元。最后,還添加了兩個額外的整數ALU,總共有8個——其中6個位于專用流水線上。

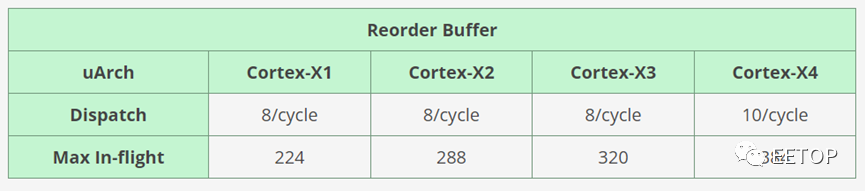

Cortex-X4的亂序緩沖區從Cortex-X3的320增加了20%,達到了384個。事實上,Arm每一代都會將ROB增加10%至30%左右。從一個角度來看,Cortex-X4的ROB現在比英特爾的Sunny Cove核心更大,后者只有352個條目,盡管遠遠不及令人驚嘆的Golden Cove的512個條目ROB。

在浮點數方面,Arm對除法器/平方根單元進行了完全流水線化。管道和單元本身保持不變。

在內存子系統方面,Arm重新平衡了流水線。以前,Cortex-X3具有兩個通用的地址生成單元(AGU)和一個專用的加載AGU,而現在的Cortex-X4只有一個通用AGU,同時配備了兩個加載AGU和一個存儲AGU。

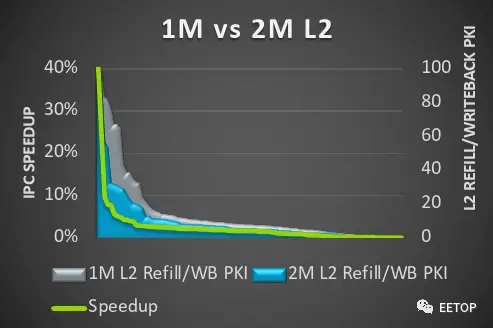

Cortex-X4上的私有L2緩存也得到了擴大。系統集成商現在可以選擇集成高達2 MiB的L2緩存,這將使L2緩存與上一代相比翻倍。如果需要的話,在更受限制的環境下,系統設計師可以選擇使用較小的緩存大小。Arm表示,較大緩存不會增加延遲。這個選項可以在具有大內存占用的應用程序中實現更高的性能,因為它可以更頻繁地引用靠近核心的內存。

總的來說,Cortex-X4在ISO頻率和L3(盡管具有較大的L2緩存)方面提供了約13%的IPC改進。

審核編輯 :李倩

-

ARM

+關注

關注

134文章

9164瀏覽量

368625 -

移動處理器

+關注

關注

0文章

133瀏覽量

22916 -

驍龍

+關注

關注

2文章

1017瀏覽量

36897

原文標題:Arm發布Cortex X4,功耗可降低40%!

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CY8C40xx系列32 位 PSOC? Arm? Cortex? 微控制器Cypress

如何降低AFE4400的功耗?

MAX32675C超低功耗Arm? Cortex?-M4F MCU

基于TI AM62x的Debian系統正式發布,豐富的軟件生態,讓您的應用開發更便利!

Arm Cortex-X925為用戶實際需求提供強勁性能

實際項目開發中為何選擇ARM? Cortex?-M4 內核的HK32MCU?

Arm Cortex-X925 樹立全新性能標桿,實現人工智能、游戲和多任務處理的先進功能

國產!全志科技T507-H工業核心板( 4核ARM Cortex-A5)規格書

從AI手機到AI PC,Arm拿什么打造AI盛宴?

ARM發布旗艦手機芯片:性能提升、AI性能增強、節能減耗

天璣9300旗艦芯:全大核CPU架構,性能與能效的提升

業界首款基于Arm Cortex-M85處理器的MCU

Arm發布Cortex X4,功耗可降低40%!

Arm發布Cortex X4,功耗可降低40%!

評論