“大數據”、“物聯網”、“移動”、“網絡”和“存儲”應用是下一代高性能系統的關鍵驅動力。為了滿足新興應用的帶寬要求,需要增加通道寬度或速度。增加車道寬度并不具有成本效益,因此提高速度是最好的可行選擇。與 PCIe 4.0 的 16GT/s 相比,PCIe 8.3 將每通道吞吐量翻了一番,達到 0GT/s,在不增加通道寬度的情況下提供了更高的性能。

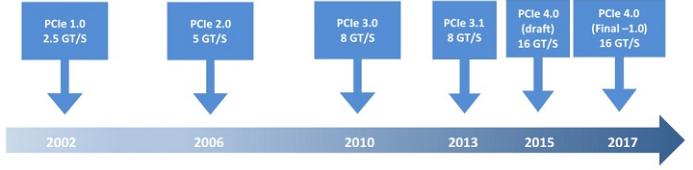

PCIe 4.0 架構向后兼容前幾代 PCIe。為前幾代設計的設備仍然可以在新技術下正常運行。下圖顯示了 PCIe 規范的演變。

PCIe 4.0 規范有多個草案版本,在每個草案版本中添加了增量功能并修改了現有功能。一些早期的ECN,如re-timer,DVSEC,PASID-ATS也被添加/應用于PCIe 4.0規范。以下列表總結了 PCIe 4.0 新添加/更改的功能:-

速度更改為 16GT/s

4.0 的均衡更新(8 GT/s 至 16 GT/s)

TSx 操作系統更改

16 GT/秒 EIEOS

SKP 操作系統更改 (CTRL SKP)

輪詢。合規性更新

10 位標簽

數據鏈路功能交換

流量控制擴展

接收邊距

重定時器

配置空間寄存器更新

PCIe 5.0 到來

PCIe 5.0 規范將進一步將速度提高到 32 GT/s。該委員會分享說,許多 PCIe 4.0 功能將在 PCIe 5.0 中重復使用,只需稍作更改以納入速度變化。以下是 PCIe 5.0 中預期功能的列表:

第 5 代信令速率為 32 GT/s

重用128b/130b編碼(類似于8 GT/s和16 GT/s)

均衡更改

32 GT/秒 EIEOS

審核編輯:郭婷

-

物聯網

+關注

關注

2912文章

44912瀏覽量

375938 -

PCIe

+關注

關注

15文章

1258瀏覽量

83006 -

大數據

+關注

關注

64文章

8908瀏覽量

137654

發布評論請先 登錄

相關推薦

PCIe 3.0/4.0的鏈路均衡的工作原理

PCIe 4.0 SSD尚未起飛,就要迎戰速度翻倍的5.0

十銓推出一款采用石墨烯散熱的PCIe 4.0 SSD

金士頓首款PCIe 4.0 SSD亮相 采用M.2轉接PCIe方案

簡單回顧關于PCIe的歷史和變革,了解PCIe4.0帶來的時代意義和價值

實測數據分析 PCIe 4.0固態硬盤性能如何

PCIe 4.0固態硬盤和PCIe 3.0區別大嗎

PCIe5.0還未普及,PCIe4.0固態硬盤仍是SSD巔峰

PCIe 6.0入門之什么是 PCIe 6.0

PCIe 4.0:新功能快速入門

PCIe 4.0:新功能快速入門

評論