芯片制造和測試數(shù)據(jù)分析在半導體行業(yè)的重要性

設(shè)計、制造和測試集成電路 (IC) 的過程復雜、廣泛且昂貴,尤其是當 IC 設(shè)計本身變得更大、更復雜時。

芯片制造和測試過程產(chǎn)生的數(shù)據(jù)量是巨大的,壓倒性的,以至于變得毫無用處,除非有一種有效的方法來收集和分析它。與其他數(shù)據(jù)密集型流程一樣,需要適當?shù)拇髷?shù)據(jù)分析工具來幫助產(chǎn)品工程師收集數(shù)據(jù)、對齊數(shù)據(jù)、排序數(shù)據(jù)、理解數(shù)據(jù),并提供有意義且可操作的見解,以確定問題的根本原因并提出解決方案的糾正措施。

及時訪問芯片數(shù)據(jù)對于管理半導體行業(yè)的關(guān)鍵成功因素至關(guān)重要:產(chǎn)品質(zhì)量和良率、運營效率和上市時間。請繼續(xù)閱讀,了解工程師正在利用的數(shù)據(jù)類型、市場上當前工具的局限性以及支持半導體行業(yè)的全新 Synopsys 數(shù)據(jù)分析解決方案。

芯片制造和測試數(shù)據(jù)的海嘯

在標準的制造過程中,芯片要經(jīng)過嚴格的制造和測試階段。該過程的每個階段都有可能挖掘有價值的信息,這些信息可以防止任何受損的芯片經(jīng)歷整個過程。及早發(fā)現(xiàn)問題不僅可以在制造和測試過程中節(jié)省資金,還有助于防止將有缺陷的產(chǎn)品運送給客戶,并可能導致使用過程中的災(zāi)難性故障。

制造測試的第一階段之一,晶圓驗收測試(WAT),發(fā)生在晶圓在代工廠生產(chǎn)晶圓之后,然后進行沖擊測試。在凸塊測試階段,焊球(凸塊)在代工廠連接到芯片 I/O 焊盤上。接下來是晶圓分類(WS),組裝(ASSY),最終測試(FT)和系統(tǒng)級測試(SLT)。

WS階段是通常由外包半導體組裝和測試(OSAT)供應(yīng)商完成的測試,OSAT供應(yīng)商是一家第三方公司,負責在測試儀上將無晶圓廠公司(芯片開發(fā)商)提供的參數(shù)測試應(yīng)用于晶圓。在此階段,可能會運行數(shù)千個測試,具體取決于測試的復雜程度。然后將晶圓切成單獨的芯片,并在ASSY階段放入封裝中。FT 和 SLT 可以包含許多在 WS 期間執(zhí)行的相同測試,但通常也包含其他測試。

從歷史上看,WAT、WS 和 FT 是無晶圓廠公司積極尋求分析的最常見數(shù)據(jù)源,主要是因為這些是數(shù)據(jù)分析解決方案關(guān)注或知道如何處理的數(shù)據(jù)源。今天仍然有些正確。然而,BUMP、ASSY和SLT數(shù)據(jù)對于了解芯片的完整歷史非常重要,并且在發(fā)現(xiàn)以前因不分析這些數(shù)據(jù)而掩蓋的問題時可能是無價的。一個好的數(shù)據(jù)分析解決方案應(yīng)該能夠收集和分析來自每個主要測試階段的所有數(shù)據(jù)。

一個簡單的經(jīng)驗法則是,在制造過程中,芯片測試失敗的后期,由于在早期測試階段浪費了測試人員的時間,現(xiàn)在浪費了昂貴的包裝,最終導致無法銷售這些失敗芯片的收入損失,因此成本就越高。因此,盡早識別有缺陷的芯片對于開發(fā)芯片的公司的財務(wù)狀況至關(guān)重要。這只能通過訪問和查看所有數(shù)據(jù)來實現(xiàn)。

芯片數(shù)據(jù)管理和可追溯性需求

當問題在任何這些測試階段出現(xiàn)時,至關(guān)重要的是工程師能夠追溯根本原因,以確定問題是否特定于某個晶圓或在特定時間段內(nèi)制造的每個晶圓。

追溯以查看制造過程早期階段是否存在可以預測后期階段(例如ASSY,F(xiàn)T或SLT)遇到的故障的測試參數(shù)或晶圓廠工藝條件的過程稱為向后饋送數(shù)據(jù)。為了正確執(zhí)行這種可追溯性,該工具需要能夠與每個芯片上運行的每次測試相關(guān)聯(lián)。這要求芯片包含嵌入式芯片 ID (ECID)。

對齊數(shù)據(jù)也很重要。這是跟蹤每個芯片來自哪個晶圓以及該晶圓來自哪個批次的過程;通常,一個批次有25個晶圓。最后,當以不同的單位(考慮伏特與毫伏)進行測試時,需要在分析之前對數(shù)據(jù)進行歸一化。

工程師花費 80% 的時間進行數(shù)據(jù)管理(例如,搜索、對齊、規(guī)范化和過濾數(shù)據(jù)集),而只有 10% 到 20% 的數(shù)據(jù)被使用過。需要有一種更有效和更有成效的方式。

推出下一代芯片分析解決方案:SiliconDash

為了顯著減少準備大量可用數(shù)據(jù)的時間(更不用說分析和得出有意義的結(jié)論),工程師需要大數(shù)據(jù)工具來幫助他們。這就是SiliconDash的用武之地。

SiliconDash 是一款適用于無晶圓廠公司、IDM、OSAT 和代工廠的大批量半導體芯片數(shù)據(jù)分析解決方案。它為高管、經(jīng)理、產(chǎn)品工程師、測試工程師、質(zhì)量工程師、維護工程師、設(shè)備工程師、良率工程師和測試操作員提供全面的、端到端的、實時的 IC 和多芯片模塊 (MCM) 產(chǎn)品的制造和測試操作控制。

SiliconDash可用于改善產(chǎn)量管理,質(zhì)量管理和吞吐量管理。用戶會看到包含該工具找到的自動結(jié)果的標準儀表板。用戶還可以輕松創(chuàng)建自己的自定義儀表板,例如公司紅綠燈儀表板、供應(yīng)商儀表板、設(shè)備儀表板、技術(shù)儀表板等,這些儀表板映射到他們自己的產(chǎn)量和質(zhì)量標準。

此外,對整個制造鏈的所有傳入數(shù)據(jù)提供近乎實時的系統(tǒng)化和全自動數(shù)據(jù)準備和分析,這些數(shù)據(jù)來自地理上分散的制造和測試操作中的大容量數(shù)據(jù)流。

這一切都與數(shù)據(jù)洞察和糾正措施有關(guān)

SiliconDash使用強大的算法來近乎實時地分析芯片數(shù)據(jù)。這些分析可以在稱為“見解”的儀表板和報告中找到,這些儀表板和報告是自動生成的,并立即開箱即用。

這些見解是完全自動化的,不需要用戶設(shè)置、配置或培訓 - 這是行業(yè)首創(chuàng)。它們突出顯示了關(guān)鍵的興趣點,使您能夠在幾分鐘內(nèi)快速分析、分類和確定問題的根本原因。

假設(shè) OSAT 測試樓層上的探針卡有問題。SiliconDash將識別此問題,并自動生成一封電子郵件發(fā)送給產(chǎn)品線上的特定工程師,指定該特定探針卡所在的特定測試儀,并導致產(chǎn)量低下。這允許工程師調(diào)查并停止該測試儀(如有必要),或者在繼續(xù)制造測試過程時暫時禁用該探針卡。或者,如果SiliconDash已被授予對制造執(zhí)行系統(tǒng)(MES)的訪問權(quán)限,它可以自動關(guān)閉關(guān)鍵應(yīng)用的測試儀,直到問題得到解決。

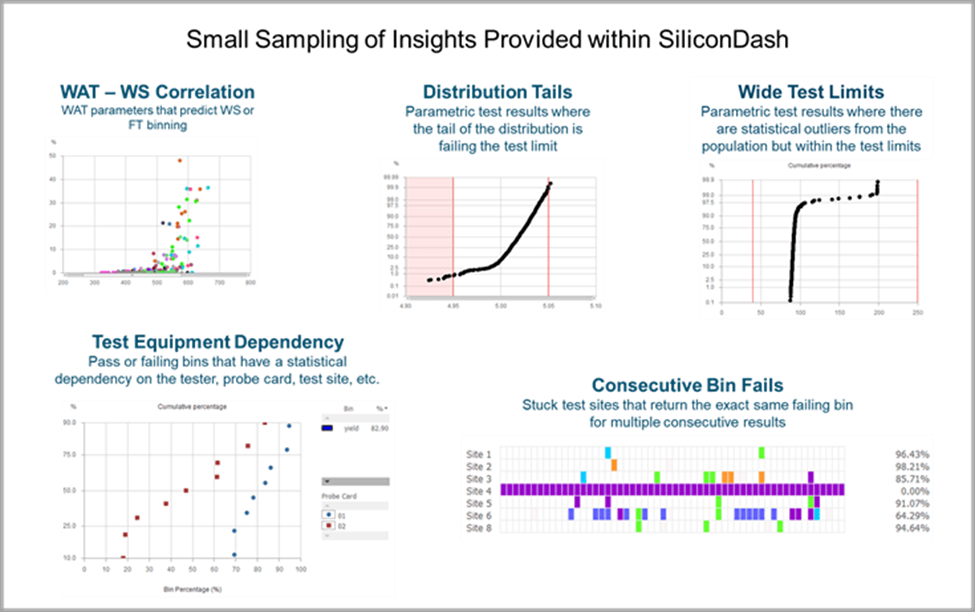

SiliconDash提供40多種開箱即用的見解;下圖顯示了五個比較受歡迎的見解。例如,分布尾部圖顯示有多少模具未達到測試下限并影響整體良率。用戶可以進行實時仿真,只需單擊并向左拖動測試下限即可確定可以獲得多少產(chǎn)量。

如前所述,WAT-WS 相關(guān)性圖表使用相關(guān)性模擬 SiliconDash 中可追溯性的強大功能,允許工程師檢測可以預測下游問題的上游參數(shù),例如芯片在 FT 中失效。通過在 WAT 或 WS 測試階段及早發(fā)現(xiàn)這些問題,可以節(jié)省大量成本并提高生產(chǎn)率。生產(chǎn)力不僅在于快速縮短工程調(diào)試時間以找到問題的根源,還在于隨著問題的快速識別和解決,產(chǎn)品的整體生產(chǎn)爬坡時間得以改善。

Synopsys的客戶Marvell Technology, Inc.最近在其制造測試過程中實施了SiliconDash,并在第一季度擁有超過100名用戶。Marvell體驗到了以下好處:

最終,最終用戶在評估市場上的不同工具時,應(yīng)考慮數(shù)據(jù)分析解決方案在識別和解決問題方面的速度和精確程度。SiliconDash是市場上唯一一款無需工程師干預即可對發(fā)現(xiàn)的關(guān)鍵興趣點和問題提供全面洞察的解決方案:無需對數(shù)據(jù)集進行特殊排序、查詢或手動操作。最后,從所有不同的制造測試階段立即接收和分析測試數(shù)據(jù)的能力,以及交叉分析和關(guān)聯(lián)數(shù)據(jù)以將糾正措施反饋到制造鏈中的能力也是關(guān)鍵。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

456文章

51155瀏覽量

426319 -

半導體

+關(guān)注

關(guān)注

334文章

27687瀏覽量

221529 -

晶圓

+關(guān)注

關(guān)注

52文章

4973瀏覽量

128220

發(fā)布評論請先 登錄

相關(guān)推薦

芯片制造和測試數(shù)據(jù)分析在半導體行業(yè)的重要性

芯片制造和測試數(shù)據(jù)分析在半導體行業(yè)的重要性

評論