今天給大俠帶來基于FPGA的數字視頻信號處理器設計,由于篇幅較長,分三篇。 今天帶來第一篇,上篇,視頻信號概述和視頻信號處理的框架。 話不多說,上貨。

導讀

圖像是用各種觀測系統以不同形式和手段觀測客觀世界而獲得的,可以直接或間接作用于人眼進而產生視知覺的實體。

隨著電子技術和計算機技術的飛速發展,數字圖像技術近年來得到極大的重視和長足的發展,并在科學研究、工業生產、醫療衛生、通信等方面得到廣泛的應用。

視頻信號由一系列連續的圖像組成。 對視頻信號的處理已經成為數字圖像處理領域中重要的一部分。 例如機器人模式識別的過程就是一個視頻信號處理的過程,電視制導導彈識別目標就是充分利用視頻信號處理技術不斷判斷目標是否和預先設定目標圖像一致。 本篇將講解如何用 FPGA 技術實現基本的視頻信號處理。 本篇的例子可以作為各位大俠進行視頻信號處理時的一個參考,也可以在這個基礎上根據需要進行擴展。

第一篇內容摘要:本篇會介紹視頻信號概述,包括視頻信號處理的基本過程、數字圖像處理技術概念、數字視頻信號的格式; 視頻信號處理的框架,包括視頻信號轉換模塊、視頻數據計算模塊以及通信模塊等相關內容。

一、視頻信號概述

在講解數字視頻信號處理器以前,需要了解視頻信號的組成。 攝像頭輸出的視頻信號滿足電視信號的制式,一般攝像頭、攝像機都提供 PAL 制的視頻信號。

目前,世界上實際應用的電視信號制式主要有 NTSC 制、PAL 制和 SECAM 制 3 種。 世界上大多數國家采用 PAL 制,我國也采用 PAL 制。 美國、日本等國家采用 NTSC 制。 俄羅斯、法國、埃及等少數國家采用 SECAM 制。

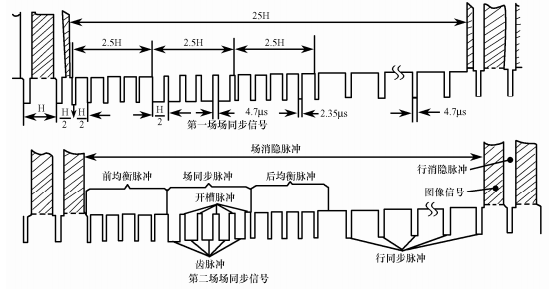

PAL 電視制式規定,場掃描頻率為 50Hz,每幀圖像的掃描行數為 625 行。 PAL 制電視信號如圖 1 所示。

圖 1 PAL 制電視信號

電視信號由“圖像信號”和確保掃描同步的“復合同步信號”以及消除掃描逆程回掃線的“復合消隱信號”等輔助信號構成。 有關電視信號的原理請自行查閱相關資料,這里不詳細解釋。

1.1 視頻信號處理的基本過程

視頻信號的處理過程就是拍攝視頻信號的逆過程。 攝像頭輸出的是標準 PAL 制電視信號。 攝像頭通過光電轉換實現圖像到視頻信號的轉換,也就是掃描的過程。 攝像頭每掃描完一行圖像,加入一個行同步脈沖,每掃描完一場圖像加入一個場同步信號。 同時為了保證掃描逆程光柵不顯示,應加入和同步信號同周期的消隱信號。

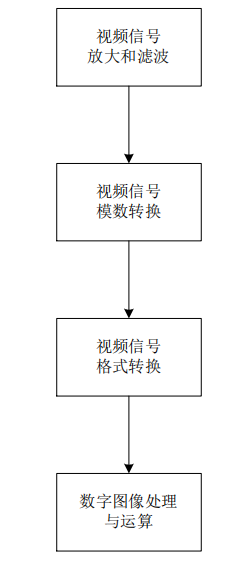

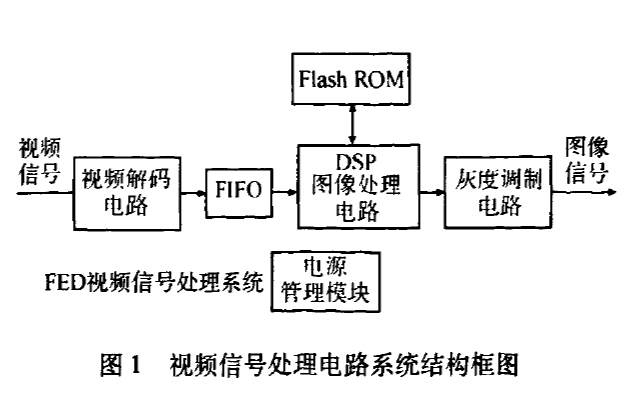

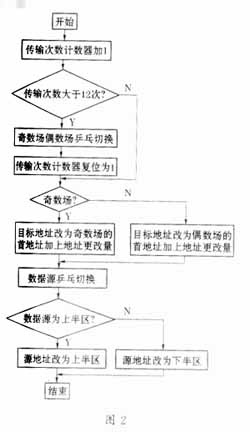

對視頻信號進行處理,需要先進行 A/D 轉換、行/場同步信號的分離等步驟,然后采用專用的視頻信號處理器對視頻信號進行轉換,最后用FPGA 處理數字圖像信號并得到需要的結果。 視頻信號處理流程如圖 2 所示。

圖 2 視頻信號處理基本流程

1.2 數字圖像處理技術概念

如圖 2 所示的流程中,視頻信號的放大、模數轉換和格式轉換由專用的視頻處理芯片完成,FPGA 需要完成對視頻信號轉化后的數字圖像進行處理和運算。 在進行具體的開發前先介紹一下相關的概念。

1)像素

一幅平面圖像可以看成是由許許多多的小單元組成,在圖像處理系統中,這些組成畫面的細小單元稱為像素。 像素越小,單位面積上的像素數目就越多,由其構成的圖像就越清晰。

一幅黑白或者灰度平面圖像,表征它的特征參量是亮度。 這就是說,組成畫面的每個像素,不但有各自確定的幾何位置,而且它們各自還呈現著不同的亮度。 又由于電視系統傳送的是活動圖像,因而每個在確定位置上的像素其亮度又隨時間不斷地變化著,也就是說像素的亮度又是時間的函數。 像素亮度既是空間(二維)的函數,同時又是時間的函數。

2)一幀圖像

電視系統中把構成一幅圖像的各像素傳送一遍稱為進行了一個幀處理,或稱為傳送了一幀,每幀圖像由許多像素組成。 因此組成一幅完整圖像也叫做一幀圖像。

3)一場圖像

PAL 制電視圖像是隔行掃描的,即一幀圖像分兩次掃描,第一次掃描奇數行的圖像,第二次掃描偶數行的圖像。 每次掃描獲得的圖像稱為一場圖像,分為奇數場和偶數場。

4)圖像的串行傳輸

根據人的視覺惰性,可把組成一幀圖像的各個像素的亮度按一定順序一個一個地轉換成相應的電信號并依次傳送出去,接收端再按同樣順序將各個電信號在對應位置上轉變成具有相應亮度的像素,這就是圖像的串行傳輸。

這種串行傳輸具有兩個特點:

? 要求傳送速度快。 只有傳送迅速,傳送時間小于視覺暫留時間,重現圖像才會給人以連續無跳動的感覺。

? 傳送要準確。 每個像素一定要在輪到它傳送時才被轉換、傳送,并被接收方接收。 而且收、發雙方每個像素被轉換、還原的幾何位置要一一對應。 即收發雙方應同步工作,同步在電視系統中是十分重要的。

5)掃描

將組成一幀圖像的像素,按順序轉換成電信號的過程(或逆過程)稱為掃描。 掃描的過程和我們讀書時視線從左到右、自上而下依次進行的過程類似。 從左至右的掃描稱為行掃描,自上而下的掃描稱為幀或者場掃描。 電視系統中,掃描多是由電子槍進行的,通常稱其為電子掃描。 通過電子掃描與光電轉換,就可以把反映一幅圖像亮度的空間與時間的函數轉換為只隨時間變化的單值函數(電信號),從而實現平面圖像的順序傳送。

1.3 數字視頻信號的格式

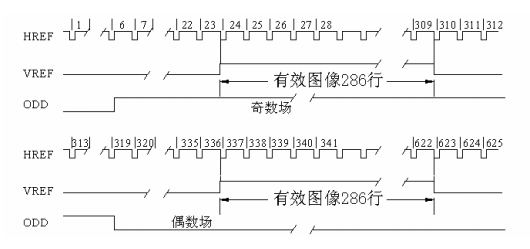

PAL 制電視信號轉化為數字視頻信號后的具體格式如圖 3 所示,一般數據格式符合 ITU656 YUV 42 標準(在后面的將結合數字視頻處理器對數字視頻格式詳細介紹)。

圖 3 一幀圖像采集的時序關系

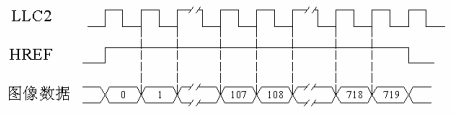

一幀圖像含有 625 行數據,其中有效圖像數據 572 行,其他為場消隱信號; 每行圖像數據包含 720 個像素。 因此,PAL 制電視信號的分辨率為 720×572。 PAL 制電視信號每秒掃描 25幀圖像,每幀包括奇、偶兩場圖像。 一幀圖像分為奇數場和偶數場,每場各有 286 行有效圖像。 垂直參考電壓信號 VREF 的高電平表示有效圖像信號,偶數場和奇數場各 286 行。 ODD 信號高電平表示為奇數場,低電平表示偶數場。 行參考電壓信號 HREF 信號表示一行有效的圖像數據。 一行圖像數據又包括 720 個像素的數據,每行圖像數據如圖 4 所示。

圖 4 一行圖像數據

二、視頻信號處理的框架

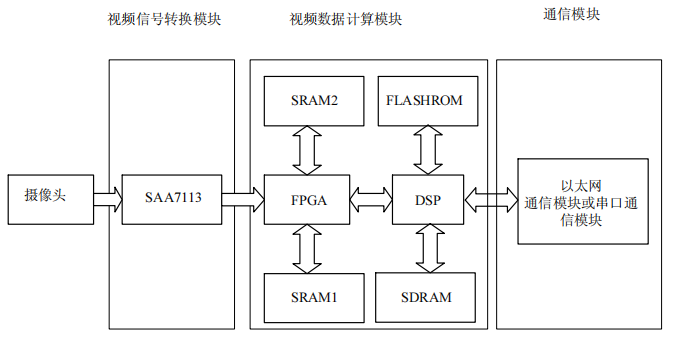

如圖 5 所示的是一般工程項目中視頻信號處理的框架,由 3 個模塊組成:

? 視頻信號轉換模塊

由視頻信號處理器完成視頻信號從模擬信號到數字信號的轉換、圖像信號與其他的分離、視頻信號的格式轉換等,最終提供后端可以處理的數字視頻數據。

? 視頻數據計算模塊

首先接收來自前一個模塊的數字視頻數據,然后完成對數字視頻數據的計算。 一般數據接收由 FPGA 完成,根據需要可以選擇專用芯片,如 DSP(Digital SignalProcessor,數字信號處理器)完成計算,也可以選擇 FPGA。

? 通信模塊

實現與外界的數據交換。

圖 5 視頻信號處理框架

雖然視頻信號處理的需求多種多樣,但數據處理的流程都遵循數據采集、格式轉換、數據接收、數據計算、數據通信的步驟。

2.1 視頻信號轉換模塊

視頻信號轉換模塊由視頻信號處理器及其輔助電路組成。 這個模塊的設計要點是選擇視頻信號處理器。 電視信號構成極為復雜,其中除了包含圖像信號之外,還包含行同步信號、行消隱信號、場同步信號、場消隱信號以及槽脈沖信號、前均衡脈沖、后均衡脈沖等。 因而,對電視信號進行 A/D 轉換的電路也非常復雜,Philips 公司將這些非常復雜的電視 A/D 轉換電路集成到了一塊芯片內,生產出功能強大的視頻輸入處理芯片 SAA7113(后面簡稱 SAA7113)。

SAA7113 采用 CMOS 工藝,通過簡潔的 I2C 總線與采樣控制器連接可方便地構成圖像采集系統。 SAA7113 芯片中的場同步信號、行同步信號、像素時鐘信號 LLC2 以及其他狀態信號都可直接由管腳引出,省去了時鐘同步電路的設計,而且可靠性更高。 系統內部采用鎖相環技術,不但有高的可靠性,并簡化了設計復雜度。 在 SAA7113 中有控制字可以直接控制行同步有效時間,省略了行延遲電路。 因此,采用 SAA7113 可為電視信號的數字化應用提供極大的方便。

2.2 視頻數據計算模塊

在視頻信號處理過程中為保證實時性,首先要求實時圖像處理系統具有處理大數據量的能力; 其次對系統的體積大小、功能、穩定性等也有嚴格的要求。 實時圖像處理算法中經常要用到對圖像的求和、求差運算、二維梯度運算、圖像分割、邊緣探測等不同層次、不同種類的運算。 有的運算結構比較簡單,但是數據量大,計算速度要求高; 有些運算對速度要求并不高,但計算方式和結構比較復雜,難以用純硬件方式實現。 因此,實時圖像處理系統是要求運算速度高、運算種類多的綜合性信息處理系統。

隨著大規模可編程器件的發展,采用 DSP+ASIC(Application Specific IntegratedCircuit,特定用途集成電路)結構的信號處理系統顯示出了其優越性,逐步得到重視。與通用集成電路相比,ASIC 芯片具有體積小、重量輕、功耗低、可靠性高等優點,而且在大批量應用時更可降低成本。現場可編程門陣列(FPGA)是在專用 ASIC 的基礎上發展起來的,它克服了專用 ASIC 不夠靈活的缺點。與其他中小規模集成電路相比,其優點主要在于它的靈活性很強,即其內部具體的邏輯功能可以根據需要配置,對電路的修改和維護很方便。

目前,FPGA的容量已經超過了百萬門級,FPGA 已成為系統設計的重要選擇方案之一。圖像處理系統中,底層的圖像預處理的數據量很大,要求處理速度快,但運算結構相對比較簡單,適用于 FPGA 通過硬件實現,這樣能同時兼顧速度及靈活性。高層運算的特點是所處理的數據量較底層少,但算法結構復雜,適宜采用運算速度高、尋址方式靈活、通信能力強的DSP 芯片來實現。

DSP+FPGA 結構最大的特點是結構靈活,有較強的通用性,適于模塊化設計,從而能夠提高運算、處理的效率;同時開發周期短,易于維護和擴展,適于實時圖像處理;對不同算法有較強的適應能力。

上面的討論為各位大俠提供視頻數據計算的方案。由于本篇主要介紹 FPGA 技術,這里將結合FPGA 介紹如何進行視頻數據計算。

2.3 通信模塊

通信模塊用于提供當前系統與外部進行數據交換的通道,可以有以太網、RS-232、RS-422、RS-485、現場總線、USB 等多種方式。

本篇到此結束,下一篇帶來基于FPGA的數字視頻信號處理器設計(中),介紹視頻信號處理的電路,包括中央控制器 FPGA、電視信號轉換模塊電路、圖像緩存部分電路;還會介紹視頻處理程序的具體實現,包括主體程序的實現、視頻圖像數據采集程序的實現以及SRAM 的讀寫控制等相關內容。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19395瀏覽量

230673 -

FPGA

+關注

關注

1630文章

21783瀏覽量

605023 -

計算機

+關注

關注

19文章

7529瀏覽量

88409 -

攝像頭

+關注

關注

60文章

4860瀏覽量

96066 -

視頻信號

+關注

關注

2文章

102瀏覽量

23961

原文標題:基于FPGA的數字視頻信號處理器設計

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何用FPGA技術實現基本的視頻信號處理

FPGA應用視頻信號處理的基本過程是怎樣的

FPGA數字視頻信號的格式

FPGA視頻信號處理的框架是怎樣的

一種基于DSP與FPGA實現場發射平板顯示器視頻信號處理系統的方案

數字視頻信號及其測試

采用FPD-Link III技術實現數字視頻信號遠傳設計

如何使用DSP和FPGA實現場發射平板顯示器視頻信號處理系統的方案說明

基于AIT2139全數字視頻信號處理器實現視頻轉換器的應用方案

基于FPGA的數字視頻信號處理器設計

基于FPGA的數字視頻信號處理器設計

評論