這期繼續分享NMOS在ESD防護中的妙用。上期講到改變GGNMOS中反偏結的擊穿電壓可以實現對Trigger Voltage的改變。而眾多改變反偏結擊穿電壓的方法無論是改變摻雜濃度還是改變拓撲結構,其本質都是通過改變反偏結空間電荷區的電場分布來改變Trigger Voltage。

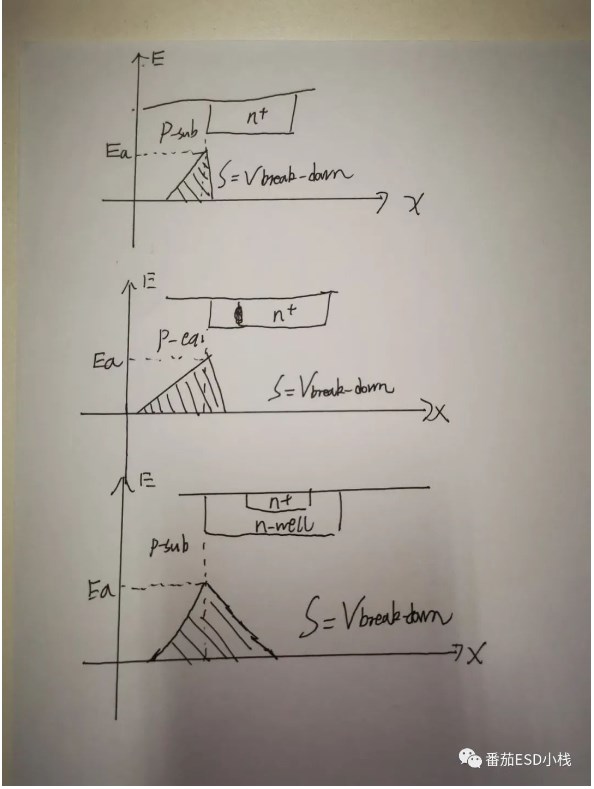

圖一。摻雜濃度對電場分布與擊穿電壓影響示意圖。

摻雜濃度越低,空間電荷區越大,電場分布越廣,擊穿電壓也就越大。同時通過調整器件的拓撲結構也能實現對Trigger Voltage的調控。

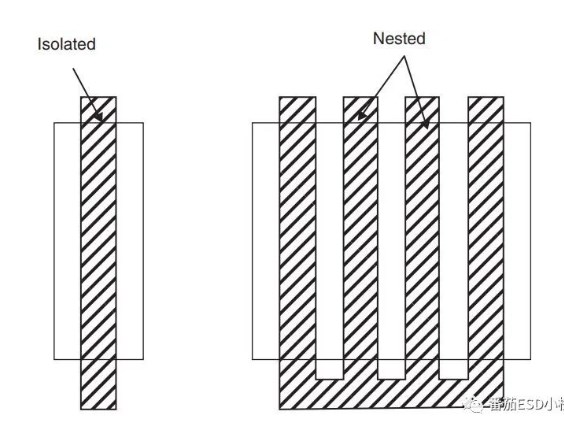

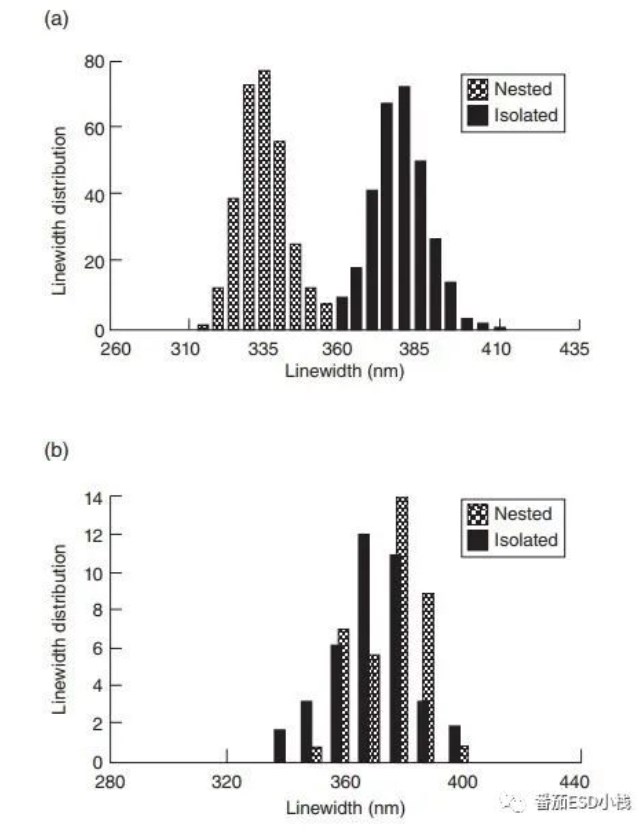

同樣線寬下多指結構能分散電場分布,提高擊穿電壓。

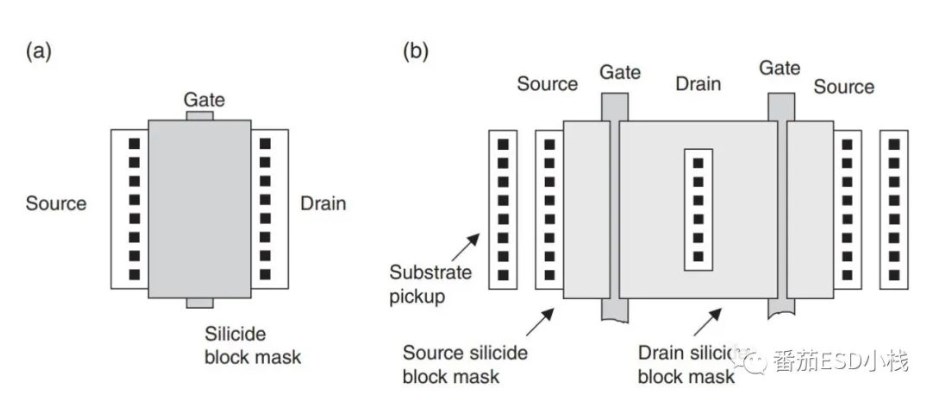

圖二。多指結構與單指示意圖。(圖片源于《ESD circuits and Device》.Voldman)

圖三。叉指電流分布。(圖片源于《ESD circuits and Device》.Voldman)

目前主流的ESD設計都采用叉指結構。無論是GGNMOS還是GCNMOS。

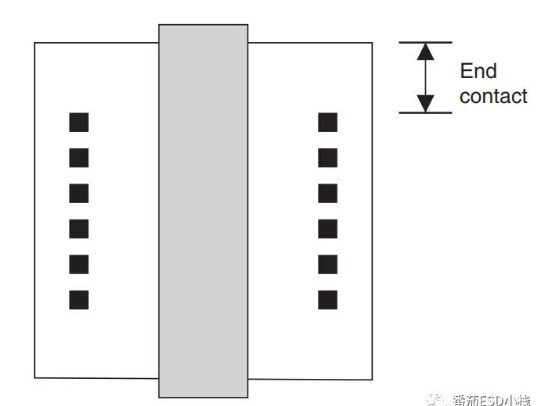

圖四。尾端接觸孔。(圖片源于《ESD circuits and Device》.Voldman)

Voldman指出不同接觸孔的電流分布是有區別的,兩端的接觸孔電流密度更大,調整兩端接觸孔的距離也能改變擊穿電壓。

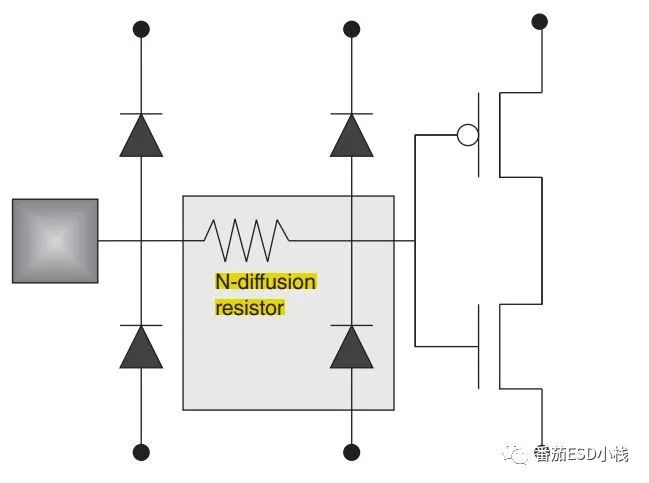

圖五.Silicide示意圖。(圖片源于《ESD circuits and Device》.Voldman)

Silicide在保護器件的同時,也能提高器件的擊穿電壓。

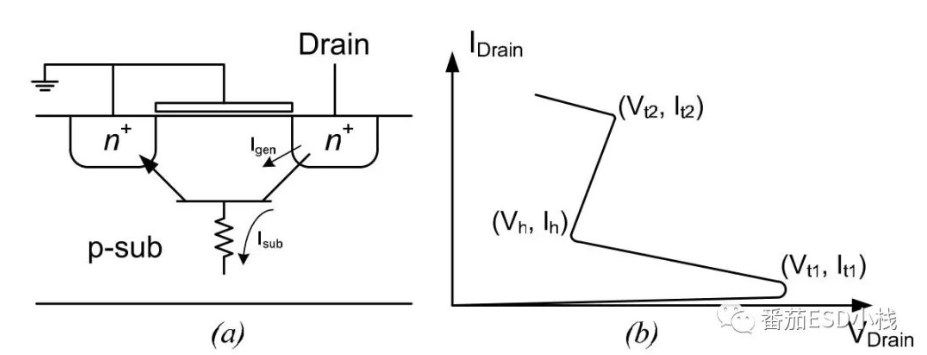

Holding Voltage調制

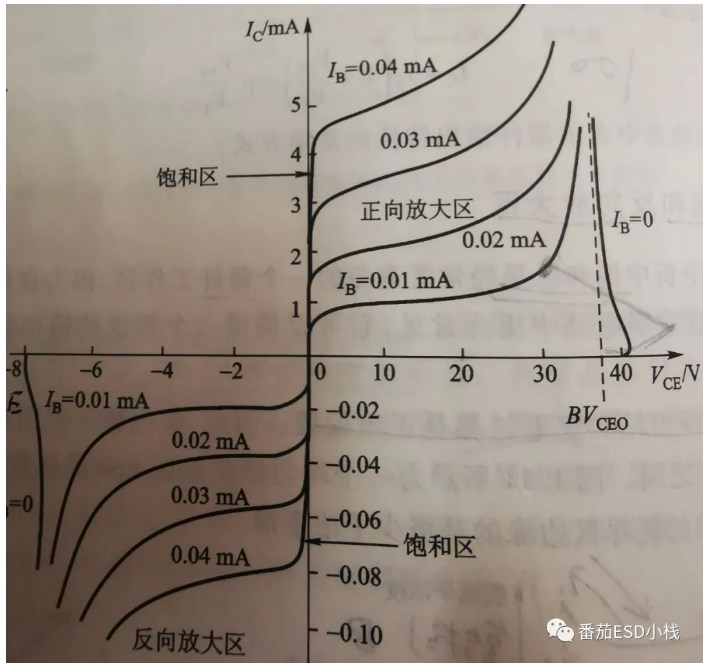

GGNMOS作為Snap-back型器件,針對其Holding Voltage的調制也是業界焦點。根據上一篇對GGNMOS機理的分析,可以得出若想改變Holding Voltage便需要改變寄生三極管中雪崩擊穿載流子與漂移載流子的比例。漂移載流子累積越慢,其Holding Voltage越低。常規三極管在擊穿后也存在極其微弱的Snap-Back,如圖所示,因為常規BJT的基區很薄,摻雜濃度也不高,所以擊穿后,漂移載流子很快能占據上風。

圖六。常規BJT的I-V特性曲線。(圖片源于《模擬集成電路的分析與設計》.GRAY)

已知原理后可以通過調整源漏間距,改變寄生BJT基區濃度等手段改變Holding Voltage。

業界一般很少對結構參數進行微調,因為微調帶來的改變疊加工藝偏差會帶來很多意想不到的結果,所以更多的需要設計人員對結構與機理進行理解。而Trigger Voltage和Holding Voltage的選取也有很多的講究,這會單獨做一期Design Window的分享。

GGNMOS最關鍵的參數就是Trigger Voltage和Holding Voltage,至于第二次熱擊穿, 更多的受制于工藝。工藝線寬越大,二次擊穿越大。

-

三極管

+關注

關注

143文章

3622瀏覽量

122246 -

ESD

+關注

關注

49文章

2062瀏覽量

173237 -

BJT

+關注

關注

0文章

237瀏覽量

18226 -

NMOS管

+關注

關注

2文章

121瀏覽量

5510

發布評論請先 登錄

相關推薦

淺談ESD防護設計—NMOS的妙用(二)

淺談ESD防護設計—NMOS的妙用(二)

評論