在具有電阻、電感和電容的電路里,對(duì)電路中的電流所起的阻礙作用叫做阻抗。

阻抗匹配是指信號(hào)源或者傳輸線(xiàn)跟負(fù)載之間達(dá)到一種適合的搭配。阻抗匹配主要有兩點(diǎn)作用,調(diào)整負(fù)載功率和抑制信號(hào)反射。

相對(duì)于阻抗變化的關(guān)系(其中一個(gè)參數(shù)變化,假設(shè)其余條件不變),影響阻抗因素如下:

阻抗線(xiàn)寬與阻抗成反比,線(xiàn)寬越細(xì),阻抗越大,線(xiàn)寬越粗,阻抗越低。

介質(zhì)厚度與阻抗成正比,介質(zhì)越厚,阻抗越大,介質(zhì)越薄,阻抗越低。

介電常數(shù)與阻抗成反比,介電常數(shù)越高,阻抗越小,介電常數(shù)越低,阻抗越大。

防焊厚度與阻抗成反比,在一定厚度范圍內(nèi),防焊厚度越厚,阻抗越低,防焊厚度越薄,阻抗越大。

銅箔厚度與阻抗成反比,銅厚越厚,阻抗越低,銅厚越薄,阻抗越大。

間距與阻抗成正比,間距越大,阻抗越大,其余影響因素則與特性阻抗相同。

阻抗線(xiàn)距導(dǎo)體的間距與阻抗成正比,間距越大,阻抗越大,其它影響因素則與特性阻抗相同。

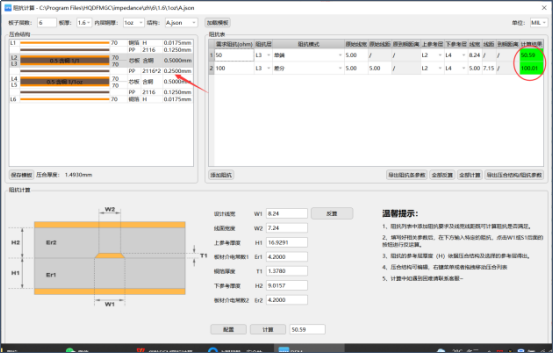

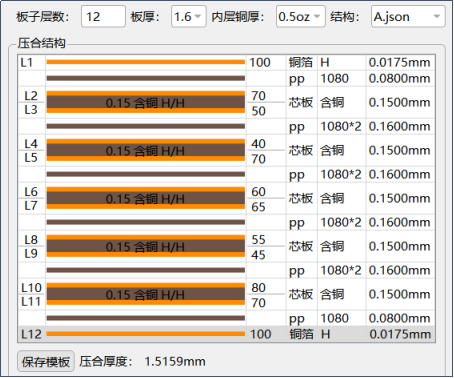

這里推薦一款免費(fèi)的國(guó)產(chǎn)工具:華秋DFM軟件,它可以自動(dòng)生成疊層圖,也可以手動(dòng)填寫(xiě)層數(shù)、板厚、銅厚,用疊層圖的介質(zhì)厚度匹配阻抗。

如需調(diào)整疊層結(jié)構(gòu),軟件里面有自帶板材、半固化片及銅箔的庫(kù),可根據(jù)需要自行選擇。在疊層結(jié)構(gòu)需要更改的參數(shù)位置,點(diǎn)擊右鍵添加、替換或刪除。彈出的窗口是軟件自帶的物料庫(kù),芯板、光板、PP、銅箔可供選擇。

疊層結(jié)構(gòu)的參數(shù)要保證正確性,半固化片、板材及銅厚參數(shù)不可出錯(cuò),若板材及半固化片厚度用錯(cuò),即便是總板厚能夠達(dá)到,疊層結(jié)構(gòu)不對(duì)稱(chēng)生產(chǎn)的成品板子,也會(huì)導(dǎo)致板翹無(wú)法使用,計(jì)算阻抗時(shí),介質(zhì)厚度如果跟實(shí)際生產(chǎn)有差異,會(huì)導(dǎo)致阻抗值偏大或者偏小,超出要求的公差。

疊層結(jié)構(gòu)的銅厚一定選擇準(zhǔn)確,如果銅厚錯(cuò)誤,會(huì)導(dǎo)致差分阻抗相差20ohm左右,單端阻抗相差10ohm左右,因此而達(dá)不到實(shí)際設(shè)計(jì)要求的阻抗值。例如:要求銅厚1oz,制作疊層是0.5oz,生產(chǎn)按照疊層生產(chǎn)板子,會(huì)導(dǎo)致成品銅厚不夠,線(xiàn)寬載流不夠,導(dǎo)致產(chǎn)品燒板報(bào)廢。

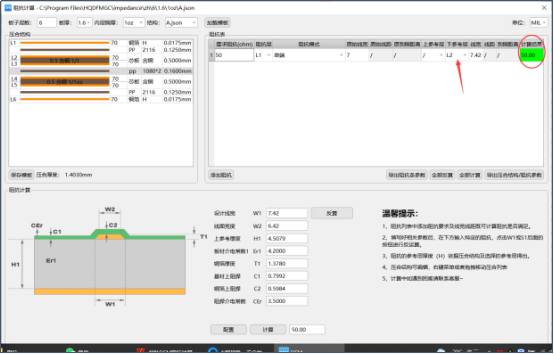

計(jì)算阻抗時(shí),模板不能選錯(cuò),需要根據(jù)實(shí)際設(shè)計(jì)選擇模板,比如單端共面阻抗,直接使用單端模板,阻抗會(huì)相差10ohm左右,導(dǎo)致阻抗超公差,如果是隔層參考的,沒(méi)有使用隔層參考的模板,阻抗會(huì)相差幾十個(gè)ohm,導(dǎo)致板子直接報(bào)廢。

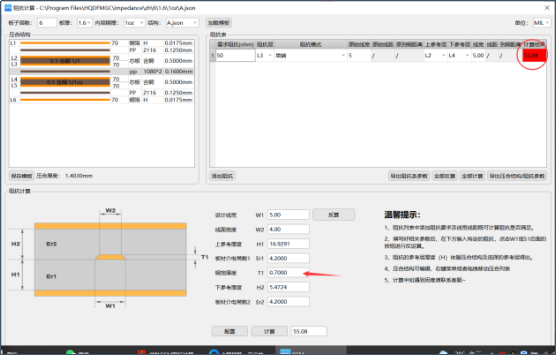

以下基于華秋的工藝制造說(shuō)明:

H1:半固化片的介質(zhì)厚度,要填寫(xiě)殘銅留膠后的介質(zhì)厚度。

Erl:華秋的板材常規(guī)是4.2,如果是特殊板材要填寫(xiě)板材的介電常數(shù)。

W2:線(xiàn)面寬度在線(xiàn)底寬度W1-0.5mil。

T1:內(nèi)層H/Hoz,銅厚按0.6mil計(jì)算,內(nèi)層1/1oz,銅厚按1.2mil計(jì)算,外層成品銅厚1/1oz,銅厚按1.4mil計(jì)算,外層成品銅厚2/2oz,銅厚按2.4mil計(jì)算。

C1:基材上的阻焊厚度0.8mil。

C2:銅面上的阻焊厚度0.5mil。

C3:差分阻抗線(xiàn)之間的阻焊厚度0.8mil。

CEr:阻焊的介電常數(shù)3.5mil。

殘銅率默認(rèn)是70%,如默認(rèn)的參數(shù)需要調(diào)整,可以在參數(shù)配置里面填寫(xiě)修改,保存即可。

1、接收客戶(hù)文件后,進(jìn)行文件預(yù)審。檢查客戶(hù)文件里面的阻抗線(xiàn)對(duì)應(yīng)的阻抗控制要求參數(shù)是否一致,如發(fā)現(xiàn)不一致的阻抗異常,需要提出異常給客戶(hù)確認(rèn),比如第一層阻抗控制要求6/6/6mil的差分阻抗線(xiàn),然而在Gerber文件第一層找不到對(duì)應(yīng)的阻抗線(xiàn),對(duì)于此異常需要與客戶(hù)確認(rèn),并提出建議:①是否忽略阻抗控制要求;②阻抗線(xiàn)跟控制要求是否有偏差,并說(shuō)明實(shí)際的gerber的阻抗線(xiàn)。

2、核對(duì)gerber文件里面的疊層結(jié)構(gòu),檢查板厚、銅厚、半固化片的參數(shù)是否能夠?qū)?yīng)華秋DFM里面的物料庫(kù)。如疊層結(jié)構(gòu)的芯板厚度在DFM里面找不到,則需要與客戶(hù)確認(rèn),建議更改板厚調(diào)整疊層結(jié)構(gòu)。

3、預(yù)審阻抗線(xiàn)對(duì)應(yīng)的控制要求是否滿(mǎn)足,例如:同層的阻抗線(xiàn)控制要求一樣,介質(zhì)厚度一樣,線(xiàn)寬不一樣,導(dǎo)致兩組阻抗線(xiàn)只能控制一組,此時(shí)需要客戶(hù)確認(rèn),阻抗同層、同介質(zhì)厚度的阻抗下是否能夠統(tǒng)一。

1、首先需要按照客戶(hù)提高的阻抗控制要求,去挑選板內(nèi)對(duì)應(yīng)的阻抗線(xiàn),挑選阻抗線(xiàn)時(shí)需注意,寧可多選卻不可漏選阻抗線(xiàn)。

2、把挑選的阻抗線(xiàn)移到另外一層,待阻抗計(jì)算完畢,按照計(jì)算的結(jié)果調(diào)整阻抗線(xiàn),阻抗線(xiàn)按照生產(chǎn)制成能力補(bǔ)償后,再移回板內(nèi)正常制作出生產(chǎn)所需的工具菲林。

1、按照客戶(hù)要求的疊層厚度及所用的物料參數(shù)制作疊層圖,計(jì)算阻抗線(xiàn)時(shí),華秋DFM自動(dòng)讀取疊層圖里面的參數(shù),使用疊層圖里面的介質(zhì)厚度,計(jì)算線(xiàn)寬線(xiàn)距所需要的介質(zhì)厚度。

2、疊層圖的參數(shù)一定要正確,結(jié)構(gòu)要對(duì)稱(chēng),如果參數(shù)錯(cuò)誤,會(huì)導(dǎo)致阻抗偏差很大,疊層不對(duì)稱(chēng)會(huì)導(dǎo)致無(wú)法生產(chǎn)。

3、輸入每層的銅面積,華秋DFM可以自動(dòng)計(jì)算無(wú)銅區(qū)域的填膠量,精確計(jì)算阻抗及成品板厚的總厚度。

線(xiàn)寬線(xiàn)距計(jì)算阻抗值

選擇阻抗層,找到阻抗對(duì)應(yīng)的模板,再輸入原始線(xiàn)寬線(xiàn)距,如參考層特別,如隔層參考,需要手動(dòng)選擇參考層,參數(shù)輸入完畢后,點(diǎn)擊全部計(jì)算,計(jì)算結(jié)果為綠色則計(jì)算正確,為紅色則需要調(diào)整線(xiàn)寬線(xiàn)距或者介質(zhì)厚度。右上角可以更改單位,mil/mm,左下角則可以添加多組阻抗。

保存阻抗計(jì)算圖,阻抗計(jì)算合格后,“點(diǎn)擊”導(dǎo)出壓合結(jié)構(gòu)/阻抗參數(shù),把計(jì)算的壓合結(jié)構(gòu)圖及阻抗計(jì)算合格參數(shù)保存為PDF檔,方便以后查詢(xún)阻抗計(jì)算的結(jié)果。

阻抗計(jì)算這么多知識(shí)點(diǎn),肯定很多工程師會(huì)覺(jué)得難學(xué)的同時(shí)也記不全吧?所以,強(qiáng)烈推薦使用華秋DFM軟件,可以一鍵計(jì)算阻抗,超簡(jiǎn)單實(shí)用,并且還是免費(fèi)的哦!

在沒(méi)有華秋DFM軟件前,工程師們都是用Polar SI9000計(jì)算阻抗,但它不能制作疊層圖,需要先畫(huà)好后,再按照介質(zhì)厚度模擬阻抗,非常的不方便。

但是,用了華秋DFM軟件后,計(jì)算阻抗只需幾個(gè)步驟,輸入相關(guān)參數(shù),就能得到想要的結(jié)果,直接提升幾倍的工作效率!

華秋DFM下載地址(在電腦瀏覽器打開(kāi)):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_fsylt.zip

上方鏈接下載還可享多層板首單立減50元

每月1次4層板免費(fèi)打樣

并領(lǐng)取多張無(wú)門(mén)檻“元器件+打板+貼片”優(yōu)惠券

原文標(biāo)題:?【經(jīng)驗(yàn)分享】阻抗計(jì)算,真的沒(méi)有那么難!

文章出處:【微信公眾號(hào):電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:?【經(jīng)驗(yàn)分享】阻抗計(jì)算,真的沒(méi)有那么難!

文章出處:【微信號(hào):gh_9b9470648b3c,微信公眾號(hào):電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

輸入阻抗。但ADS8863手冊(cè)中沒(méi)有相應(yīng)的input impedance參數(shù)和曲線(xiàn)。請(qǐng)問(wèn)應(yīng)該如何估算其值?

應(yīng)如何綜合考慮ADC輸入端的抗混疊RC濾波電路和ADC內(nèi)部等效輸入電路(fig47)的阻抗?

謝謝!

發(fā)表于 12-19 07:02

圖看一下: 比如這個(gè)仿真圖中,輸入失調(diào)電流是0.4nA和0.6nA,那么當(dāng)輸入源阻抗是10MΩ時(shí),得到的輸入偏置電壓是-4.20mV和-5.96mV,然后同相輸入端和反相輸入端的凈輸入電壓差值就是1.96mV,因?yàn)?b class='flag-5'>沒(méi)有加增益電阻

![的頭像]() 發(fā)表于

發(fā)表于 12-18 11:45

?215次閱讀

根據(jù)官網(wǎng)給的手冊(cè)畫(huà)好了pcb連線(xiàn)的時(shí)候,發(fā)現(xiàn)USB有些需要差分信號(hào)線(xiàn),但是官網(wǎng)數(shù)據(jù)手冊(cè)上只是寫(xiě)了必須設(shè)計(jì)阻抗在90歐姆左右,并不是很了解怎么計(jì)算,希望大佬給點(diǎn)提示,線(xiàn)寬和線(xiàn)距還有線(xiàn)的長(zhǎng)度有哪些要求,謝謝!!!

發(fā)表于 12-16 06:05

ad,cadense 阻抗匹配計(jì)算和差分走線(xiàn)設(shè)置

發(fā)表于 10-17 16:59

?2次下載

數(shù)據(jù)手冊(cè)中電感10uH,電容680NF是4歐姆阻抗,有沒(méi)有一個(gè)大概的阻抗計(jì)算公式的?那么輸出端電感10uH,電容1uF,這樣的參數(shù)

發(fā)表于 10-15 06:33

LMV552, LMV551最近發(fā)現(xiàn)有些運(yùn)放datasheet里沒(méi)有提到輸入阻抗這一項(xiàng),比如LMV552,不知這些運(yùn)放的輸入阻抗該怎么計(jì)算?

發(fā)表于 09-18 07:23

THS4521數(shù)據(jù)手冊(cè)的26頁(yè)figure63的電路圖中,與信號(hào)源阻抗匹配時(shí),怎么計(jì)算全差分運(yùn)放的輸入阻抗啊??

發(fā)表于 09-05 07:45

阻抗匹配后反相比例放大器的輸入阻抗是怎么計(jì)算?謝謝!

發(fā)表于 08-28 08:26

如何計(jì)算同相比例放大電路的輸入阻抗呢?以圖中的電路為例,為啥是那個(gè)公式呢?

發(fā)表于 08-27 06:32

引言 在電子電路中,電容和電感是兩種常見(jiàn)的元件,它們?cè)陔娐分衅鹬匾淖饔谩k娙菘梢源鎯?chǔ)電荷,電感可以存儲(chǔ)磁能。當(dāng)電容和電感并聯(lián)時(shí),它們的阻抗特性會(huì)發(fā)生變化,這就需要我們對(duì)并聯(lián)阻抗進(jìn)行計(jì)算

![的頭像]() 發(fā)表于

發(fā)表于 07-17 14:41

?5625次閱讀

計(jì)算等多個(gè)領(lǐng)域。即使目前你還不了解它的應(yīng)用,你應(yīng)該也聽(tīng)過(guò)虛擬機(jī)的大名。那么虛擬機(jī)到底是什么?虛擬機(jī)真的那么好用嗎?讓我們一起揭開(kāi)虛擬機(jī)的神秘面紗,走進(jìn)這個(gè)充滿(mǎn)無(wú)限可

![的頭像]() 發(fā)表于

發(fā)表于 07-06 08:05

?463次閱讀

在電子學(xué)和電路理論中,阻抗是一個(gè)核心的概念,它描述了電路對(duì)電流的阻礙作用。在電路分析和設(shè)計(jì)中,我們經(jīng)常遇到輸入阻抗和輸出阻抗這兩個(gè)概念。它們分別代表了電路在輸入端和輸出端對(duì)外部電路的阻礙作用。本文將詳細(xì)探討輸入

![的頭像]() 發(fā)表于

發(fā)表于 05-28 14:33

?3631次閱讀

上次我們講到,PCIe阻抗控制到底是85ohm還是100ohm好,今天我們就從無(wú)源仿真的角度來(lái)解決系統(tǒng)阻抗搭配的問(wèn)題吧。

![的頭像]() 發(fā)表于

發(fā)表于 04-22 17:15

?759次閱讀

電子發(fā)燒友網(wǎng)站提供《PCB設(shè)計(jì)中會(huì)遇到的八種阻抗計(jì)算模型.docx》資料免費(fèi)下載

發(fā)表于 03-07 14:20

?1次下載

使用目標(biāo)阻抗去衡量仿真得到的PDN阻抗是否達(dá)標(biāo),并不是一個(gè)科學(xué)的做法。但很多時(shí)候選擇的IC可能并沒(méi)有提供各個(gè)頻段所需的PDN阻抗值,甚至翻完整個(gè)Datasheet都

![的頭像]() 發(fā)表于

發(fā)表于 01-25 09:52

?4411次閱讀

?【經(jīng)驗(yàn)分享】阻抗計(jì)算,真的沒(méi)有那么難!

?【經(jīng)驗(yàn)分享】阻抗計(jì)算,真的沒(méi)有那么難!

評(píng)論