本文內容翻譯自一篇Qorvo的應用筆記,雖然標題是針對GaN偏置電路設計的一些基本準則,但實際上對GaAs也是適用的。基于化合物半導體做射頻功放的同學應該都是有概念的,正好這篇文章做了總結,就隨手分享共同學習一下。

一、上電/下電順序

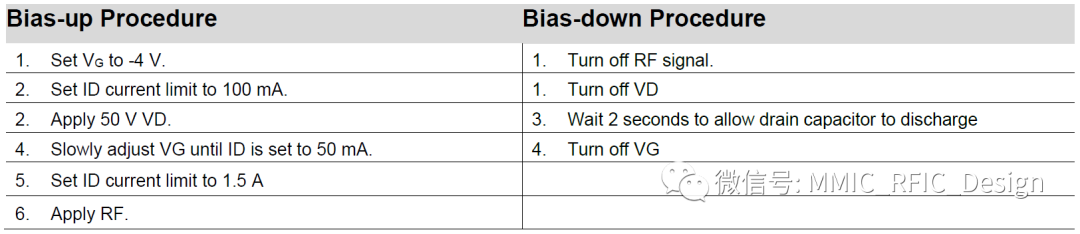

基本上GaN大功率射頻功放管都是耗盡型的,即零柵壓時管子是完全導通狀態,需要給柵極加負壓才能工作在適當的偏置電流,否則大電流必然造成器件燒毀。因此必須通過硬件或者軟件措施嚴格控制柵壓和漏壓的上電和下電順序:

上電順序:

1、設置柵壓VG到-關斷電壓(具體值視晶體管要求而定);

2、將漏極電流ID限制為靜態電流目標值IDQ的兩倍左右;

3、漏極電壓VD上電;

4、緩慢調整柵極電壓VG使漏極電流ID達到靜態電流目標值IDQ;

5、將漏極電流ID限制為比大信號工作電流稍大的值;

6、輸入射頻激勵信號。

下電順序:

1、關閉射頻輸入信號;

2、關閉漏極電源VD;

3、等兩秒以確保漏極的儲能電容已完全泄放;

4、關閉柵極電源VG。

二、設置偏置電流

用戶都是通過調整柵源電壓VGS來調節靜態工作電流IDQ的,但由于GaN晶體管的柵壓閾值波動較大,這就意味著每一只晶體管的柵壓都需要調整才能達到相同的靜態偏置電流;反之,如果施加固定柵壓,將會導致不同晶體管的靜態電流IDQ差異非常大,甚至可能完全沒有電流或者很大的電流。過小或過大的電流都會影響放大器的性能,甚至損壞晶體管。

通常靜態電流的選取都是參考器件手冊,但用戶可以以在參數允許的范圍內進行微調,以獲得期望的增益、效率、線性度、穩定性等。

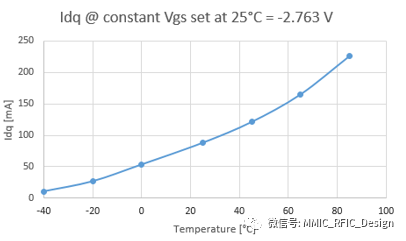

溫度會影響晶體管的閾值電壓,如果使用固定柵壓偏置則會導致電流隨溫度波動,如下圖所示:

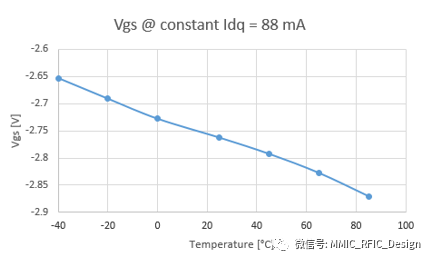

反之如果想偏置電流固定,不隨溫度變化,則應柵壓應該隨溫度調節,如下圖所示:

三、偏置旁路網絡設計

為確保器件安全穩定工作,防止意外損壞,偏置網絡的設計中有幾個方面需要注意。給射頻器件饋電的偏置網絡必須可靠去耦,旁路電容不僅可以濾除電源的噪聲和紋波,同時還充當器件的電荷源,它也降低了電源引線寄生電感的影響。偏置網絡會與器件相互作用,從而影響器件的性能和穩定性,因此有時候設計人員還需要通過給旁路電容串聯電阻來降低其Q值。

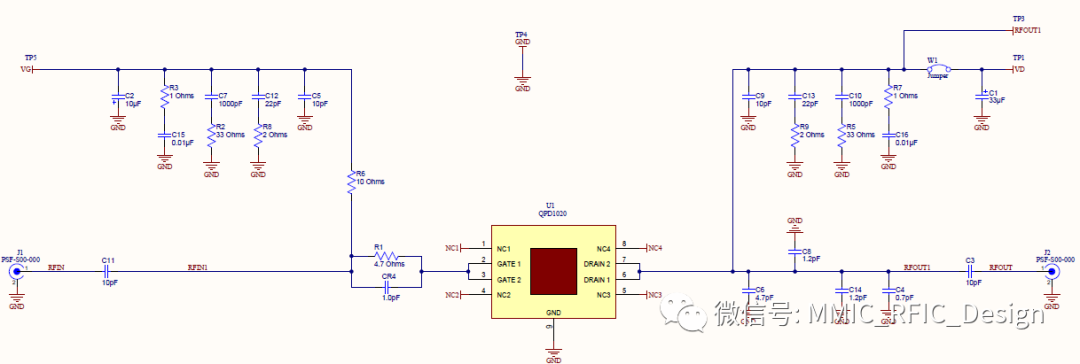

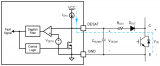

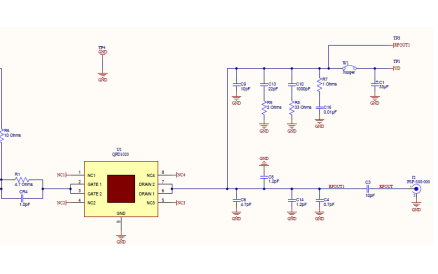

所有的GaN FET分立功放管的柵極都需要串聯一個最小5~10Ω的電阻來確保電路的穩定性,但串聯電阻一定會對射頻性能有不良影響,因此在保證穩定性的前提下串聯電阻要盡量小。一個典型的功放偏置電路(QPD1020 2.7-3.1GHz)如圖所示,GaN MMIC通常都把柵極串聯電阻集成在片內了,因此外部就不再需要串聯電阻了。

四、柵極偏置電流設計

電源和偏置電路設計需要與器件的柵極電流兼容,需要既能給柵極提供也能從柵極吸入電流(即電流可正可負)。柵極漏電流的方向是從器件的柵極流出到偏置電路。在較高功率下,由于柵極寄生二極管對射頻驅動信號的整流作用,電流會從偏置電路流進器件柵極。柵極漏電流的大小跟器件的尺寸正相關,大功率的管子漏電流比小功率管子更大。僅測試少量器件的漏電流來指導柵極偏置電路是不具有代表性的,應該參考器件手冊或者咨詢生產商的應用工程師。

如果偏置電路與GaN器件柵極之間有較大的等效電阻,柵極的漏電流就會在電阻上形成較大壓降,從而影響柵極偏置電壓。當電阻壓降很大時,柵壓上升導致漏極電流ID顯著上升甚至燒毀器件。通常柵極電流在mA量級,假設一個管子的柵極電流是-1mA,串聯1kΩ電阻就會產生1V的壓降,即柵壓比期望值偏高+1V。因此柵極的串聯電阻既不能太大(壓降)也不能太小(影響射頻性能和穩定性)。對于有源偏置電路,還應該考察其自身的穩定性。

正向的柵極電流,通常在高驅動功率時出現,也許要在設計中加以考慮。有源偏置電路必須要提供足夠的正向電流有效值,旁路電容可用于在脈沖或調制應用的峰值驅動條件下提供正向電流來源。輸入功率越大柵極電流越大,正向偏置電流的最壞情況發生在低溫下,因此最低工作溫度下、最大輸入功率下的最大柵極電流容量應該在有源偏置電路設計中進行考慮。

審核編輯:湯梓紅

-

電路設計

+關注

關注

6691文章

2503瀏覽量

207815 -

晶體管

+關注

關注

77文章

9907瀏覽量

140143 -

偏置電路

+關注

關注

10文章

99瀏覽量

31055 -

GaN

+關注

關注

19文章

2135瀏覽量

75731 -

漏極電壓

+關注

關注

0文章

8瀏覽量

7663

原文標題:應用筆記——GaN偏置電路設計準則

文章出處:【微信號:芯片設計之路,微信公眾號:芯片設計之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論