今天是 74LS76雙JK觸發器,主要是以下幾個方面:

1、74LS76 是什么芯片?

2、74LS76 雙JK 觸發器 引腳排列

3、74LS76雙JK觸發器工作原理

4、74LS76 雙JK觸發器 規格參數

5、74LS76雙JK觸發器特性

6、74LS76雙JK觸發器等效替代

7、74LS76雙JK觸發器應用電路

一、74LS76 是什么芯片?

74LS76 帶有獨立的 JK 時鐘脈沖、直接清除輸入和直接設置的雙JK觸發器。觸發器的開發方式是,當時鐘設置為高電平時,將接收數據使能輸入。

74LS76 IC 中的 JK 觸發器還具有預設和清除功能,允許 IC 繞過時鐘和輸入并提供不同的輸出。74LS76 是基于 TTL 的,可以與任何基于 TTL 的設備或任何微控制器一起操作。IC 有多種封裝形式,使 IC 可以根據要求使用任何硬件。如有必要,可以使用多個 IC 制作更多 IC。

74LS76 的實際應用是在位的存儲中,盡管它對其他應用也很有價值。幾個特性使 Jk 觸發器成為最常見的類型之一。它們包括以下內容:

時鐘輸入屬性

預設輸入引腳的存在

同樣值得注意的是,JK 觸發器可以通過施加時鐘脈沖信號來改變它們的狀態。請注意,此時鐘信號可以是上升沿或下降沿。此外,74LS76 能夠忽略無效輸出。

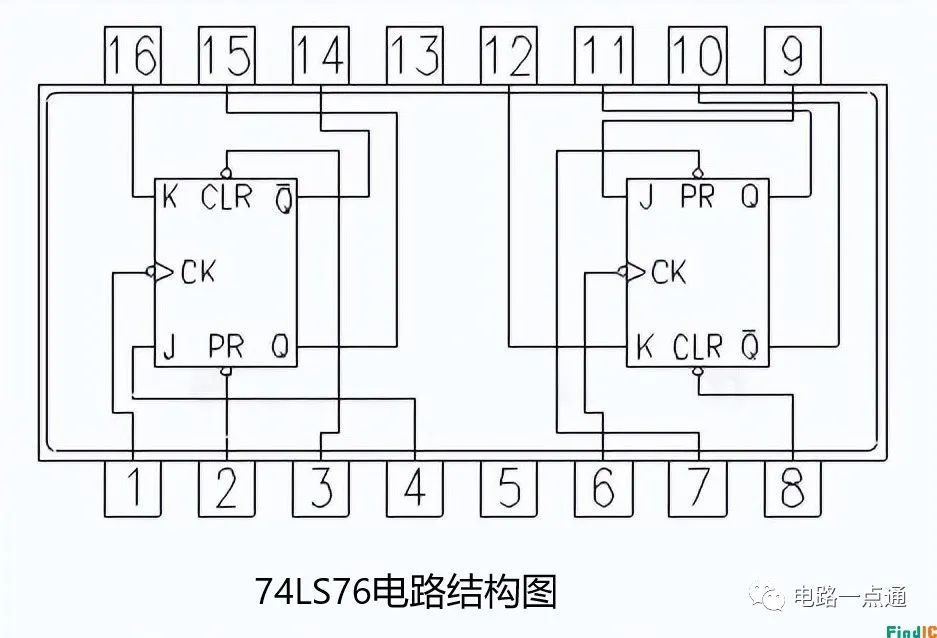

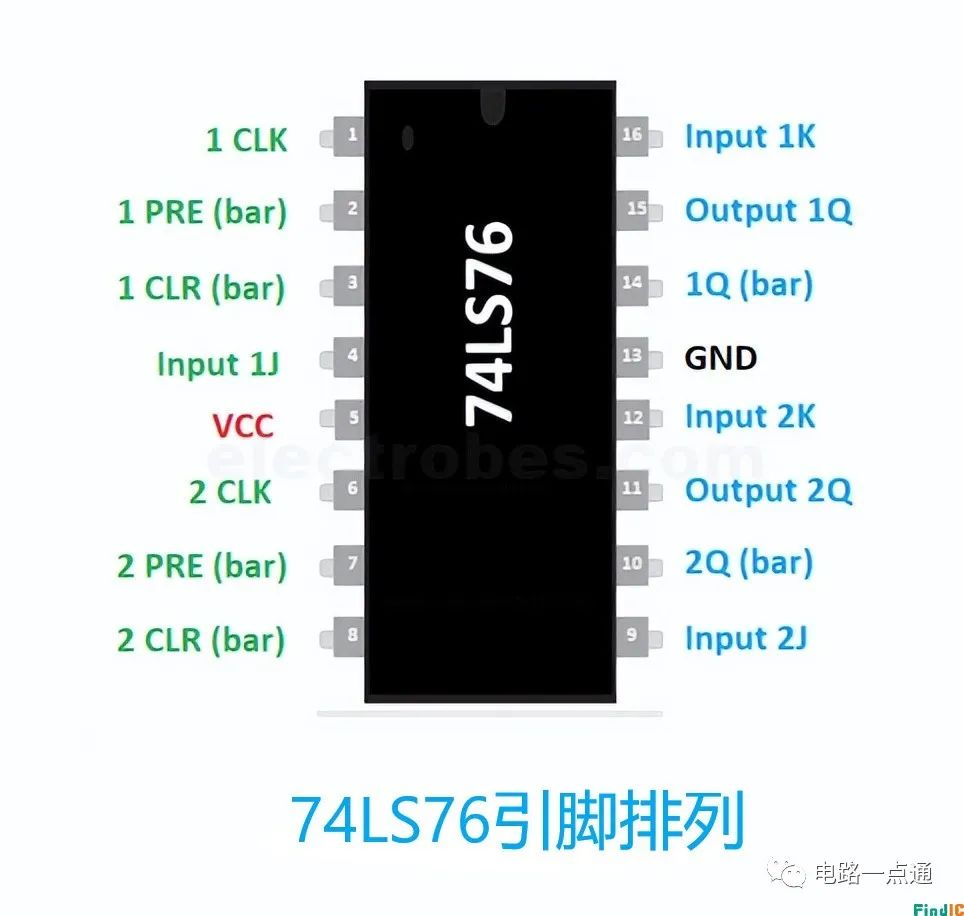

二、74LS76 雙JK觸發器引腳排列

74LS76 雙JK觸發器引腳排列

74LS76 雙JK觸發器引腳排列

74LS76 雙JK觸發器引腳說明

74LS76 雙JK觸發器引腳說明

三、74LS76 雙JK觸發器工作原理

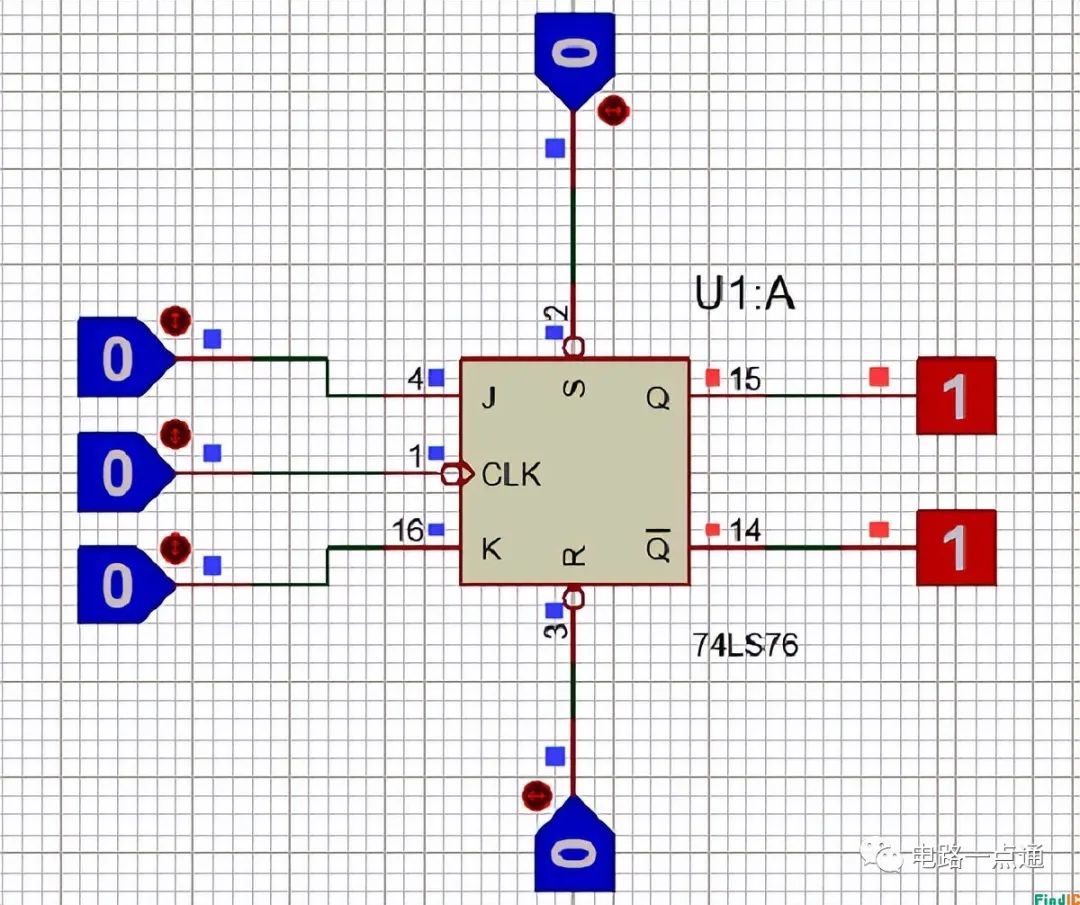

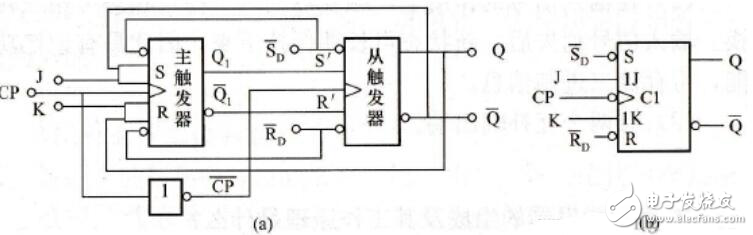

正如前面說的,我們在該 IC 中有兩個 JK 觸發器,該 IC 通常由 +5V 供電。輸入 (J, K) 引腳和輸出 (Q, Q bar) 引腳的最小和最大輸入和輸出電壓在上述規格中進行了討論。JK觸發器的工作原理如下圖所示 。

74LS76 雙JK觸發器工作原理圖 預設和清除是異步低電平有效輸入。當預設和清除設置為低時,它們會覆蓋時鐘和 JK 輸入,強制輸出達到穩態電平。 74LS76 有 5 個輸入引腳和兩個輸出引腳。輸出將取決于幾乎每個輸入引腳。當 IC 在復位引腳處于低電平狀態時,輸出引腳將為低電平,在反相輸出時,狀態將為高電平。 現在另一個輸入引腳知道為預設。當預設將處于高電平狀態時,輸出引腳將為高電平,而在反相輸出時,狀態將為低電平。要使用 IC,我們需要將它們保持在低電平,如果兩個引腳上的高電平狀態,輸出和反相輸出都會給出高電平狀態。復位引腳和清除將在不同輸入處具有這些狀態。

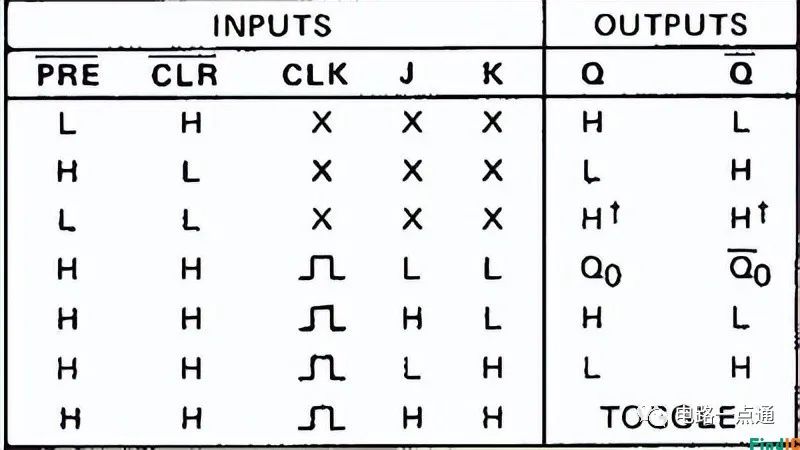

74LS76 雙JK觸發器工作原理 當 clear = 1 和 preset = 1 時,輸出將根據 J 和 K 輸入在 HIGH 到 LOW 時鐘脈沖上變化。當 J 和 K 兩個輸入都為低電平時,輸出不會有任何變化。輸出將取決于先前的狀態。在 J = 1 和 K = 1 的情況下,輸出將在每個時鐘脈沖處保持翻轉。 其他狀態將根據下面的真值表。

74LS76 雙JK觸發器工作原理 上面兩張表解釋了 JK FF 的一般工作,這個真值表描述了 74LS76 的功能,具有清晰和預設的特征。

74LS76 雙JK觸發器工作原理

四、74LS76 雙 JK觸發器 規則參數

雙 JK 觸發器封裝 IC

工作電壓:2V 至 6V

最小高電平輸入電壓:2 V

最大低電平輸入電壓:0.8 V

最小高電平輸出電壓:3.5 V

最大低電平輸出電壓:0.25V

工作溫度 -55 至 -125°C

提供 14 引腳 PDIP、GDIP、PDSO 封裝

五、74LS76 雙JK觸發器特性

首先,它是一個雙 JK 觸發器,但在 1 個 IC 內。

具有 J、K 時鐘、置位和清零輸入的兩個獨立觸發器。

7476A 具有多個帶有 14 引腳 PDIP、GDIP 和 PDSO 的封裝。

功能清除和預設是 74LS76 的兩個基本屬性。

IC 是TTL輸出形式的代名詞。因此,它與微控制器和 TTL 設備兼容。

你可以將 IC 74LS76 作為單個觸發器操作,而不會中斷其他觸發器的工作。

標準 TTL 開關電壓。

六、74LS76JK觸發器等效替代

等效于 74LS76:74LS73、MC74HC73A、SN7476 替代品 JK 觸發器:74LS107、4027B

七、74LS76 雙JK觸發器應用電路

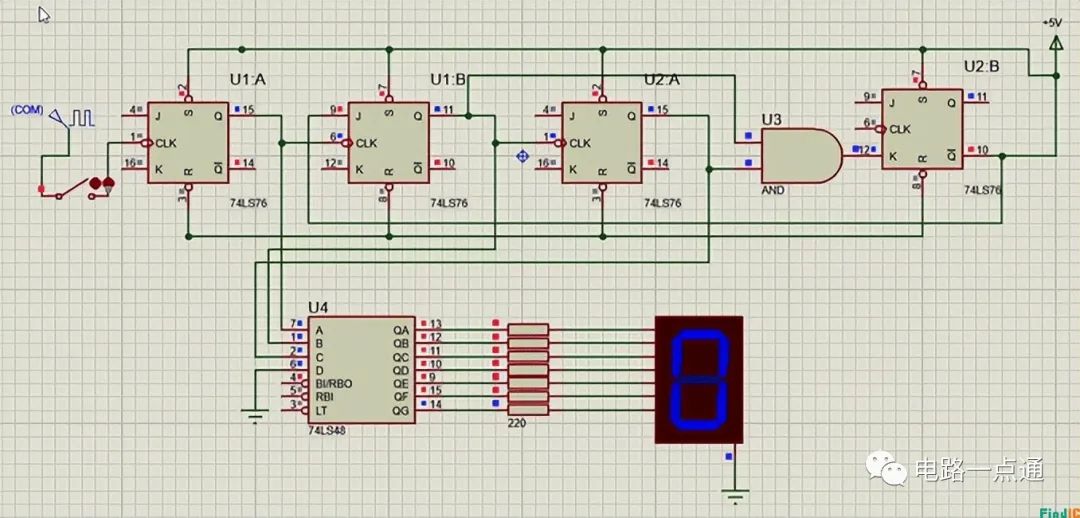

1、74LS76 的 0-9 計數器示例

在此示例中,我們將使用 JK 觸發器構建一個 3 位計數器,然后我們將通過將其轉換為 7 段上的十進制來顯示該值。要設計一個三位計數器,我們需要一個額外的組件,即與門,然后我們將使用四個 JK 觸發器。在設計完位計數器后,我們將使用 IC74LS76 將二進制數據轉換為共陰極7 段。時鐘脈沖將產生輸出,IC 將顯示 7 段數據。這是圖像。

74LS76 的 0-9 計數器示例 在三位數據中,我們可以存儲 000 到 111 的數據,即 8 個值,并且 7 段以十進制顯示從 0 到 7 的值。JK 觸發器存儲每個值并在每個時鐘脈沖上生成新值。74LS48 用作 BCD 到 7 段解碼器,我們可以在時鐘脈沖改變之前的任何時間接收到這個值。在微處理器和控制器中,時鐘引腳由手動信號控制以替換數據,直到數據保持存儲,這個過程使觸發器最適合在多個設備中臨時存儲數據。

2、其他應用

它用于將電荷存儲在 RAMS 中。

74LS76 也使用了一個鎖存器。

IC可用于設計計數器。

審核編輯:湯梓紅

-

IC

+關注

關注

36文章

6019瀏覽量

177004 -

應用電路

+關注

關注

9文章

430瀏覽量

49766 -

TTL

+關注

關注

7文章

509瀏覽量

70744 -

引腳

+關注

關注

16文章

1314瀏覽量

51378 -

觸發器

+關注

關注

14文章

2024瀏覽量

61507

原文標題:雙JK觸發器工作原理+應用電路詳解

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JK觸發器基本教程,講的超詳細!!

施密特觸發器電路及工作原理詳解_施密特觸發器特點_施密特觸發器的作用

雙JK觸發器的工作原理和應用電路詳解

雙JK觸發器的工作原理和應用電路詳解

評論