二十年前,英特爾開創(chuàng)了PCIe(PCI Express)技術(shù),但存儲成本不斷增加、數(shù)據(jù)爆炸式增長、計算和帶寬開始失衡,PCIe逐漸乏力。2019年,英特爾又提出一種開放性互聯(lián)協(xié)議——Compute Express Link(CXL),能夠讓CPU與GPU、FPGA或其他加速器之間實現(xiàn)高速高效的互聯(lián),從而滿足高性能異構(gòu)計算的要求。

在異構(gòu)計算大行其道的當(dāng)下,CXL標(biāo)準(zhǔn)被提出之后,迅速成為服務(wù)器市場熱捧的發(fā)展趨勢之一。

為什么需要新型互連?

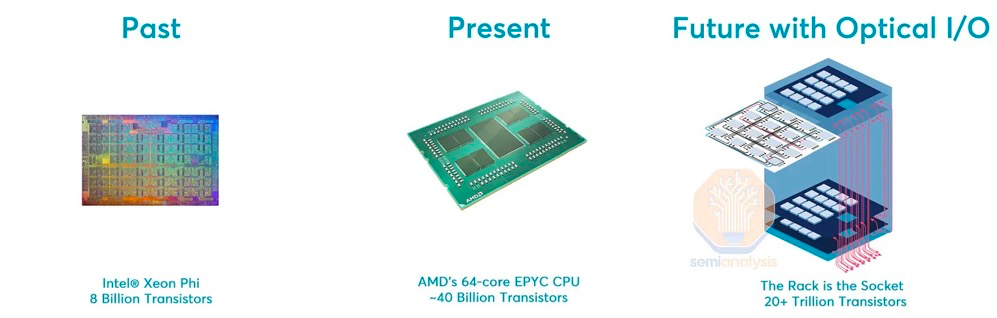

數(shù)據(jù)的爆炸式增長促使計算行業(yè)開始突破性的架構(gòu)轉(zhuǎn)變,從根本上改變數(shù)據(jù)中心的性能、效率和成本。為了繼續(xù)提高性能,服務(wù)器正越來越多地轉(zhuǎn)向異構(gòu)計算架構(gòu)。在特定任務(wù)中,專用ASIC可以使用更少的晶體管提供超過10倍的性能。

服務(wù)器內(nèi)的芯片連接通常是用 PCIe 完成的,該標(biāo)準(zhǔn)最大的缺點是缺乏高速緩存一致性和內(nèi)存一致性。從性能和軟件的角度來看,使用 PCIe,不同設(shè)備之間通信的開銷相對較高。此外,連接多臺服務(wù)器通常意味著使用以太網(wǎng)或InfiniBand,這些通信方法存在著相同的問題,具有高延遲和低帶寬。

2010 年代中期,CCIX協(xié)議成為了潛在的行業(yè)標(biāo)準(zhǔn),得到了AMD、Xilinx、華為、Arm 和 Ampere Computing 的支持,但它缺乏足夠的行業(yè)支持,并未發(fā)展起來。

2018 年,IBM 和 Nvidia 帶來了解決PCIe與NVLink缺陷的解決方案,應(yīng)用在當(dāng)時世界上最快的超級計算機Summit上。AMD在Frontier超級計算機中也有類似的專有解決方案,名為Infinity Fabric。但可以預(yù)想到,沒有任何的行業(yè)生態(tài)系統(tǒng)可以圍繞這些專有協(xié)議而發(fā)展。

之后,英特爾制定了自己的標(biāo)準(zhǔn),并于 2019 年將其專有規(guī)范作為CXL1.0 捐贈給了新成立的 CXL 聯(lián)盟。該標(biāo)準(zhǔn)得到了半導(dǎo)體行業(yè)大多數(shù)買家的支持。

基于業(yè)界大多數(shù)參與者的支持,CXL 使向異構(gòu)計算的過渡成為可能。

CXL 簡介:什么是 Compute Express Link?

CXL是一種開放式行業(yè)標(biāo)準(zhǔn)互連,可在主機處理器與加速器、內(nèi)存緩沖區(qū)和智能 I/O 設(shè)備等設(shè)備之間提供高帶寬、低延遲連接,從而滿足高性能異構(gòu)計算的要求,并且其維護CPU內(nèi)存空間和連接設(shè)備內(nèi)存之間的一致性。CXL優(yōu)勢主要體現(xiàn)在極高兼容性和內(nèi)存一致性兩方面上。

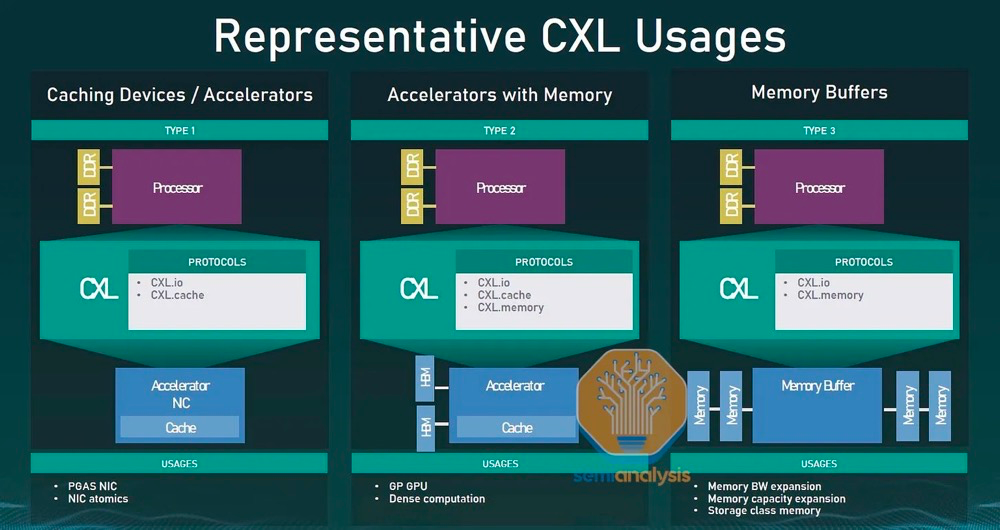

CXL 聯(lián)盟已經(jīng)確定了將采用新互連的三類主要設(shè)備:

#

類型 1 設(shè)備

智能網(wǎng)卡等加速器通常缺少本地內(nèi)存。通過 CXL,這些設(shè)備可以與主機處理器的 DDR 內(nèi)存進行通信。

#

類型 2 設(shè)備

GPU、ASIC 和 FPGA 都配備了 DDR 或 HBM 內(nèi)存,并且可以使用 CXL 使主機處理器的內(nèi)存在本地可供加速器使用,并使加速器的內(nèi)存在本地可供 CPU 使用。它們還位于同一個緩存一致域中,有助于提升異構(gòu)工作負載。

#

類型 3 設(shè)備

可以通過 CXL 連接內(nèi)存設(shè)備,為主機處理器提供額外的帶寬和容量。內(nèi)存的類型獨立于主機的主內(nèi)存。

CXL 協(xié)議和標(biāo)準(zhǔn)

CXL 標(biāo)準(zhǔn)通過三種協(xié)議支持各種用例:CXL.io、CXL.cache 和 CXL.memory。

#

CXL.io

該協(xié)議在功能上等同于 PCIe 協(xié)議,利用了 PCIe 的廣泛行業(yè)采用和熟悉度。作為基礎(chǔ)通信協(xié)議,CXL.io 用途廣泛。

#

CXL.cache

該協(xié)議專為更具體的應(yīng)用程序而設(shè)計,使加速器能夠有效地訪問和緩存主機內(nèi)存以優(yōu)化性能。

#

CXL.memory

該協(xié)議使主機(例如處理器)能夠使用load/store命令訪問設(shè)備附加的內(nèi)存。

這三個協(xié)議共同促進了計算設(shè)備(例如 CPU 主機和 AI 加速器)之間內(nèi)存資源的一致共享。從本質(zhì)上講,通過共享內(nèi)存實現(xiàn)通信簡化了編程。用于設(shè)備和主機互連的協(xié)議如下:

類型 1 設(shè)備:CXL.io + CXL.cache

類型 2 設(shè)備:CXL.io + CXL.cache + CXL.memory

類型 3 設(shè)備:CXL.io + CXL.memory

| 代表的CXL用例

CXL 的特點和優(yōu)勢

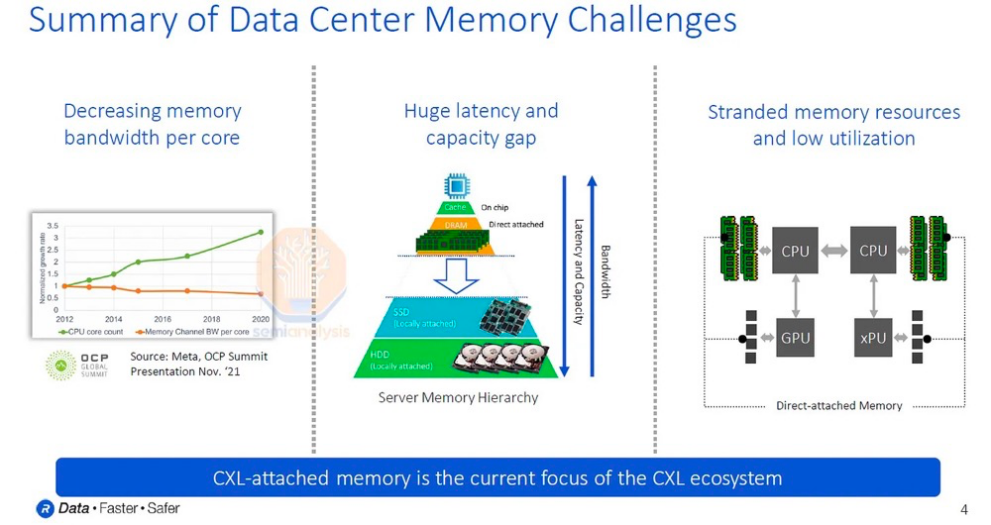

前面我們主要討論的是異構(gòu)計算,CXL 還可以有效解決內(nèi)存墻和IO墻的瓶頸。

數(shù)據(jù)中心存在著嚴重的內(nèi)存問題。自 2012 年以來,核心數(shù)量迅速增長,但每個核心的內(nèi)存帶寬和容量并沒有相應(yīng)增加,內(nèi)存帶寬反而有所下降,并且這種趨勢還在持續(xù)。此外,直連 DRAM 和 SSD 之間在延遲和成本方面存在巨大差距。

最后還有一個致命的問題,昂貴的內(nèi)存資源往往利用率很低。對于資本密集型行業(yè)來說,低利用率是一個重大問題,而數(shù)據(jù)中心業(yè)務(wù)是世界上資本密集程度最高的行業(yè)之一。

微軟表示,服務(wù)器總成本的 50% 來自 DRAM,成本巨大。盡管如此,還有高達25% 的 DRAM 內(nèi)存被閑置了!簡單來說,微軟 Azure 的服務(wù)器總成本中有 12.5% 是閑置的。

想象一下,如果這個內(nèi)存可以駐留在連接的網(wǎng)絡(luò)上并跨多個 CPU 和服務(wù)器動態(tài)分配給 VM。內(nèi)存帶寬可以根據(jù)工作負載的需求增加或減少,這將大大提高利用率。

總的來說,CXL 的內(nèi)存緩存一致性允許在 CPU 和加速器之間共享內(nèi)存資源。CXL 還支持部署新的內(nèi)存層,可以彌合主內(nèi)存和 SSD 存儲之間的延遲差距。這些新的內(nèi)存層將增加帶寬、容量、提高效率并降低TCO (總擁有成本)。此外,CXL 內(nèi)存擴展功能可在當(dāng)今服務(wù)器中的直連 DIMM 插槽之上實現(xiàn)額外的容量和帶寬。

通過 CXL 連接設(shè)備可以向 CPU 主機處理器添加更多內(nèi)存。當(dāng)與持久內(nèi)存配對時,低延遲 CXL 鏈路允許 CPU 主機將此額外內(nèi)存與 DRAM 內(nèi)存結(jié)合使用。大容量工作負載的性能取決于大內(nèi)存容量,例如 AI。而這些是大多數(shù)企業(yè)和數(shù)據(jù)中心運營商正在投資的工作負載類型,因此,CXL 的優(yōu)勢顯而易見。

CXL與 PCIe:這兩者有什么關(guān)系?

CXL 建立在PCIe的物理和電氣接口之上,通過協(xié)議建立了一致性、簡化了軟件堆棧,并保持與現(xiàn)有標(biāo)準(zhǔn)的兼容性。具體來說,CXL 利用 PCIe 5 特性,允許備用協(xié)議使用物理 PCIe 層。

CXL引入了Flex Bus端口,可以靈活的根據(jù)鏈路層協(xié)商決定是采用PCIe協(xié)議還是CXL協(xié)議。CXL具有較高的兼容性,更容易被現(xiàn)有支持PCIe端口的處理器(絕大部分的通用CPU、GPU 和 FPGA)所接納,因此,英特爾將CXL視為在PCIe物理層之上運行的一種可選協(xié)議,并且英特爾還計劃在第六代PCIe標(biāo)準(zhǔn)上大力推進CXL的采用。

當(dāng)支持 CXL 的加速器插入 x16 插槽時,設(shè)備以默認的PCIe 1.0傳輸速率(2.5 GT/s)與主機處理器端口協(xié)商。只有雙方都支持 CXL,CXL 交易協(xié)議才會被激活。否則,它們將作為 PCIe 設(shè)備運行。

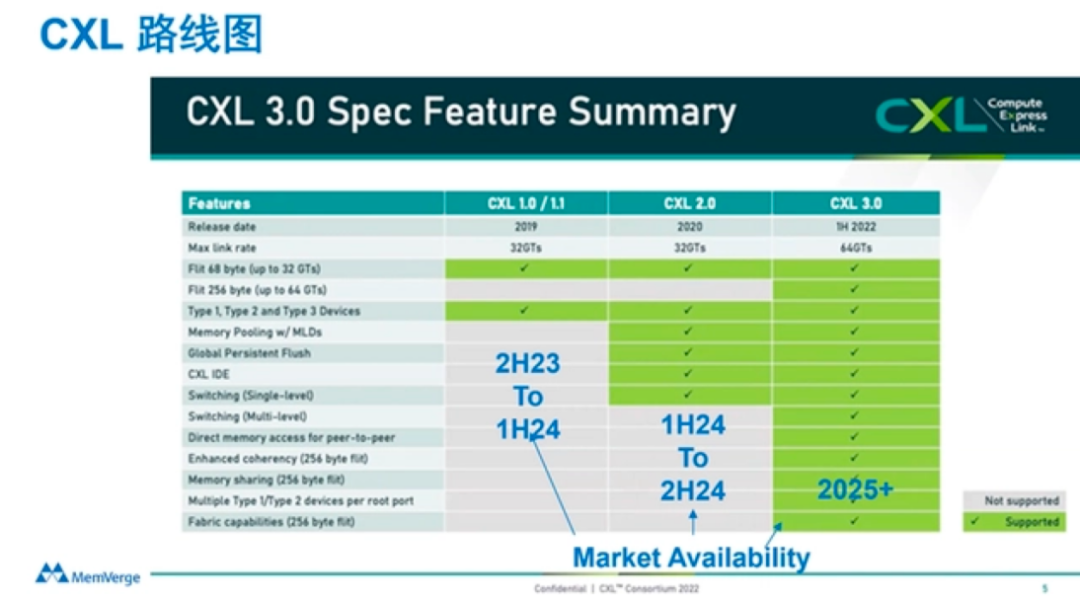

CXL 1.1 和 2.0 使用 PCIe 5.0 物理層,允許通過 16 通道鏈路在每個方向上以 32 GT/s 或高達 64 GB/s 的速度傳輸數(shù)據(jù)。

CXL 3.0 使用 PCIe 6.0 物理層將數(shù)據(jù)傳輸擴展到 64 GT/s,支持通過 x16 鏈路進行高達 128 GB/s 的雙向通信。

CXL 2.0 和 3.0 有什么新功能?

作為一項新興技術(shù),CXL發(fā)展非常迅速,過去幾年時間CXL已經(jīng)發(fā)布了1.0/1.1、2.0、3.0三個不同的版本,并且有著非常清晰的技術(shù)發(fā)展路線圖。

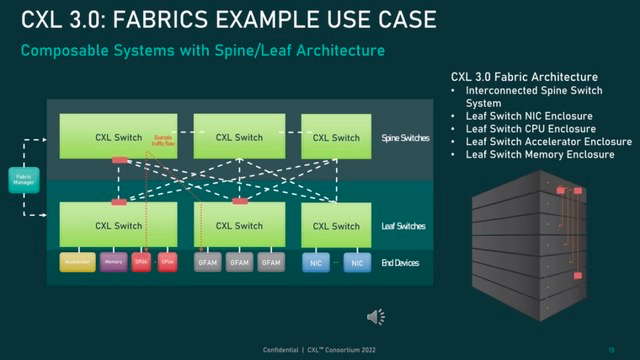

CXL 3.0是2022年8月份發(fā)布的新標(biāo)準(zhǔn),在許多方面都進行了較大的革新。CXL3.0建立在PCI-Express 6.0之上(CXL1.0/1.1和2.0版本建立在PCIe5.0之上),其帶寬提升了兩倍,并且其將一些復(fù)雜的標(biāo)準(zhǔn)設(shè)計簡單化,確保了易用性。

內(nèi)存池

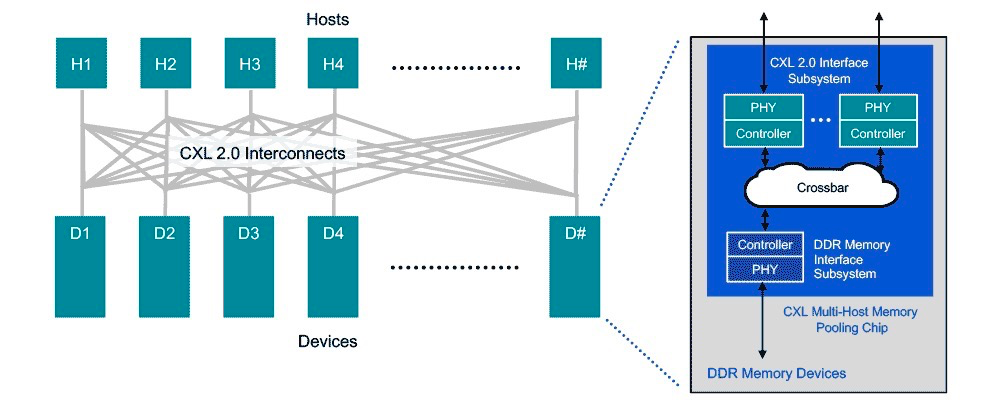

CXL 2.0 支持切換以啟用內(nèi)存池。使用 CXL 2.0 交換機,主機可以訪問池中的一個或多個設(shè)備。主機必須支持 CXL 2.0 才能利用此功能,但內(nèi)存設(shè)備可以是支持 CXL 1.0、1.1 和 2.0 的硬件的組合。在 1.0/1.1 中,設(shè)備被限制為一次只能由一臺主機訪問的單個邏輯設(shè)備。然而,一個 2.0 級別的設(shè)備可以被劃分為多個邏輯設(shè)備,允許多達 16 臺主機同時訪問內(nèi)存的不同部分。

例如,主機 1 (H1) 可以使用設(shè)備 1 (D1) 中一半的內(nèi)存和設(shè)備 2 (D2) 中四分之一的內(nèi)存,以將其工作負載的內(nèi)存需求與內(nèi)存池中的可用容量完美匹配。設(shè)備 D1 和 D2 中的剩余容量可由一臺或多臺其他主機使用,最多可達 16 臺。設(shè)備 D3 和 D4 分別啟用了 CXL 1.0 和 1.1,一次只能由一臺主機使用。

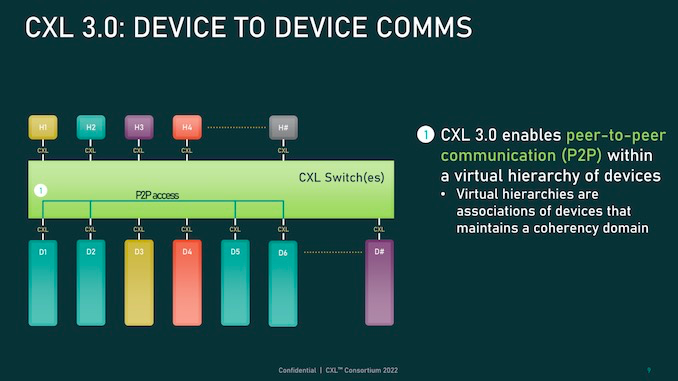

| 直連的CXL內(nèi)存池

CXL 3.0 引入了點對點的直接內(nèi)存訪問和對內(nèi)存池的增強,其中多個主機可以在CXL 3.0設(shè)備上一致地共享內(nèi)存空間。這些特性支持新的使用模型并提高數(shù)據(jù)中心架構(gòu)的靈活性。

Switching

通過轉(zhuǎn)向 CXL 2.0 直連架構(gòu),數(shù)據(jù)中心可以獲得主內(nèi)存擴展的性能優(yōu)勢,以及池內(nèi)存的效率和TCO 優(yōu)勢。假設(shè)所有主機和設(shè)備都支持 CXL 2.0,那么“switching”將通過 CXL 內(nèi)存池芯片中的交叉開關(guān)集成到內(nèi)存設(shè)備中,這樣可以保持較低的延遲。通過低延遲直接連接,附加的內(nèi)存設(shè)備可以使用 DDR DRAM 來擴展主機主內(nèi)存。

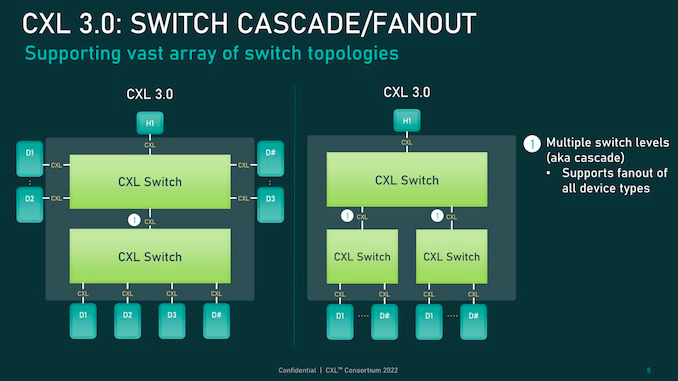

CXL 3.0 引入了多級交換,允許單個交換機駐留在主機和設(shè)備之間,并允許多級交換機實現(xiàn)多層級交換,對網(wǎng)絡(luò)拓撲種類和復(fù)雜性有更好的支持。即便只有兩層交換機,CXL 3.0也能夠?qū)崿F(xiàn)非樹狀拓撲,比如環(huán)形、網(wǎng)狀或者其他結(jié)構(gòu),對節(jié)點中的主機或設(shè)備沒有任何限制。

按需內(nèi)存

與拼車類似,CXL 2.0 和 3.0 在“按需”的基礎(chǔ)上為主機分配內(nèi)存,從而提供更高的內(nèi)存利用率和效率。該架構(gòu)提供了為工作負載配置服務(wù)器主內(nèi)存的選項,能夠在需要時訪問內(nèi)存池以處理高容量工作負載。

CXL 內(nèi)存池模型可以支持向服務(wù)器分解和可組合性的轉(zhuǎn)變。在此范例中,可以按需組合離散的計算、內(nèi)存和存儲單元,以有效地滿足任何工作負載的需求。

完整性和數(shù)據(jù)加密 (IDE)

分解或分離服務(wù)器架構(gòu)的組件增加了攻擊面,這也是為什么 CXL 包含了安全設(shè)計方法。具體來說,所有三個 CXL 協(xié)議都通過完整性和數(shù)據(jù)加密 (IDE) 來保護,IDE 提供機密性、完整性和重放保護。IDE 在 CXL 主機和設(shè)備芯片中實例化的硬件級安全協(xié)議引擎中實現(xiàn),以滿足 CXL 的高速數(shù)據(jù)速率要求,而不會增加額外的延遲。需要注意的是,CXL 芯片和系統(tǒng)本身需要防止篡改和網(wǎng)絡(luò)攻擊的保護措施。

信令擴展到 64 GT/s

CXL 3.0 對標(biāo)準(zhǔn)的數(shù)據(jù)速率進行了階梯式的提高。如前所述,CXL 1.1 和 2.0 在其物理層使用 PCIe 5.0 電氣:32 GT/s 的 NRZ 信號。使用 PAM4 信號將 CXL 3.0 數(shù)據(jù)速率提高到 64 GT/s。

CXL標(biāo)準(zhǔn)誕生并不久,據(jù)透露,支持 CXL 的英特爾、AMD 的新一代 CPU 正在部署中,預(yù)計將在今年下半年增加。這意味著 CXL 部署將在年底開始,并在 2024 年擴大規(guī)模。總的來說,CXL協(xié)議的出現(xiàn)解決了CPU和設(shè)備之間的數(shù)據(jù)傳輸問題,提高了應(yīng)用程序的性能、降低延遲、提供更高的數(shù)據(jù)傳輸速率。隨著不斷發(fā)展和普及,CXL協(xié)議的將成為數(shù)據(jù)中心和高性能計算領(lǐng)域的一個重要趨勢。

審核編輯 :李倩

-

加速器

+關(guān)注

關(guān)注

2文章

806瀏覽量

38025 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9295瀏覽量

85896 -

架構(gòu)

+關(guān)注

關(guān)注

1文章

519瀏覽量

25520

原文標(biāo)題:CXL 深入探討:可組合服務(wù)器架構(gòu)和異構(gòu)計算的未來

文章出處:【微信號:SDNLAB,微信公眾號:SDNLAB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【一文看懂】什么是異構(gòu)計算?

異構(gòu)計算的前世今生

【產(chǎn)品活動】阿里云GPU云服務(wù)器年付5折!阿里云異構(gòu)計算助推行業(yè)發(fā)展!

異構(gòu)計算在人工智能什么作用?

什么是異構(gòu)并行計算

異構(gòu)計算的前世今生

異構(gòu)計算場景下構(gòu)建可信執(zhí)行環(huán)境

MAX17007A, MAX17008 可組合的、雙通道、Q

通用可組合的RFID搜索協(xié)議

通用可組合的群簽名協(xié)議

基于FPGA的異構(gòu)計算是趨勢

異構(gòu)計算的兩大派別 為什么需要異構(gòu)計算?

異構(gòu)計算:架構(gòu)與技術(shù)

深入探討異構(gòu)計算和CXL標(biāo)準(zhǔn)的版本

打造異構(gòu)計算新標(biāo)桿!國數(shù)集聯(lián)發(fā)布首款CXL混合資源池參考設(shè)計

CXL深入探討:可組合服務(wù)器架構(gòu)和異構(gòu)計算的未來

CXL深入探討:可組合服務(wù)器架構(gòu)和異構(gòu)計算的未來

評論