11 分支走線對信號反射的影響

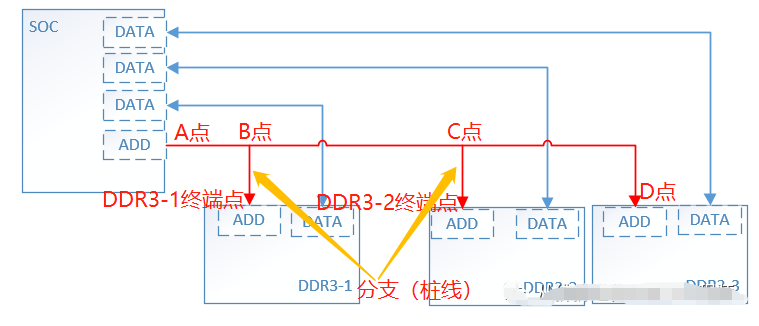

有些設(shè)計(jì)中可能是三個或者更多芯片在同一個信號鏈路上,按照flyby拓?fù)浣Y(jié)構(gòu)布局。如下圖是一顆SOC和3顆DDR3的PCB布局設(shè)計(jì)。因?yàn)槿wDDR3的ADD是共用一組來自SOC的信號線,因此只有ADD信號線有分支一說,黃色箭頭所示即為分支,也稱為樁線。除了PCB板上的走線,芯片封裝中的走線也是樁線的組成部分。這些分支是影響信號反射波形的因素之一。DATA線是SOC和DDR點(diǎn)對點(diǎn)傳輸?shù)模瑳]有分支。(注:此處僅僅是舉例,現(xiàn)實(shí)設(shè)計(jì)中,通常SOC的一組DDR端口驅(qū)動2顆DDR3芯片,SOC的另一組DDR端口驅(qū)動另外1顆或者2顆DDR3芯片)。

信號從SOC端(A點(diǎn))輸出后,當(dāng)傳輸?shù)降谝粋€分支時(B點(diǎn)),遇到的阻抗是兩端傳輸線的并聯(lián)阻抗,即在此分支遇到的阻抗會下降,因此在此阻抗變化點(diǎn),會有負(fù)反射發(fā)生,有負(fù)反射波形返回SOC。同時另一部分的信號將沿著兩個分支繼續(xù)傳播(一個向DDR3-2方向傳播下去,另一個向DDR3-1方向傳輸)。當(dāng)信號到達(dá)DDR3-1終端時,可能會有反射發(fā)生,從DDR3-1終端反射回分支點(diǎn)(B點(diǎn)),再從A點(diǎn)反射回DDR3-1終端,即在DDR3-1的這一段分支上來回反射。類似的情況也會在分支C點(diǎn)、D點(diǎn)發(fā)生。因此A點(diǎn)、B點(diǎn)、C點(diǎn)、D點(diǎn)、DDR3-1終端點(diǎn)、DDR3-2終端點(diǎn)的波形,是這些分支的反射波形的組合。它們的計(jì)算是極其復(fù)雜的,通過仿真電路得到仿真波形是比較高效的辦法。

針對分支走線對信號的影響,做仿真如下:

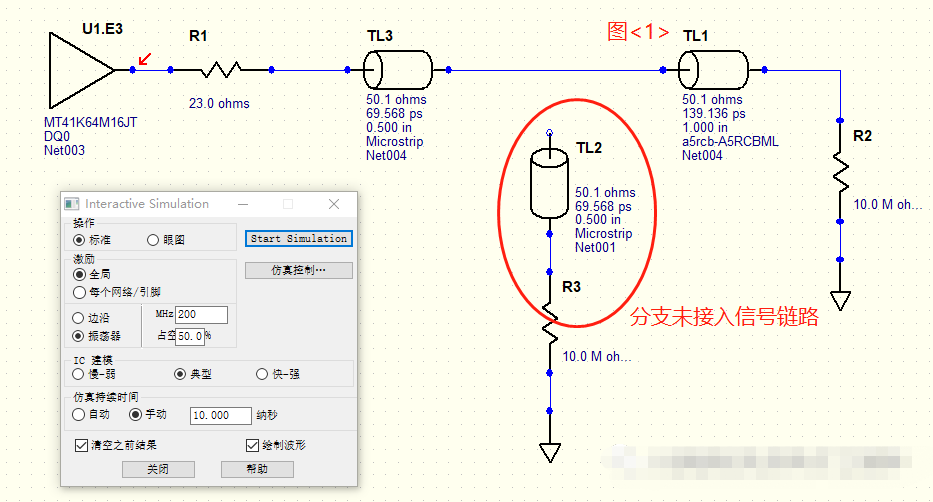

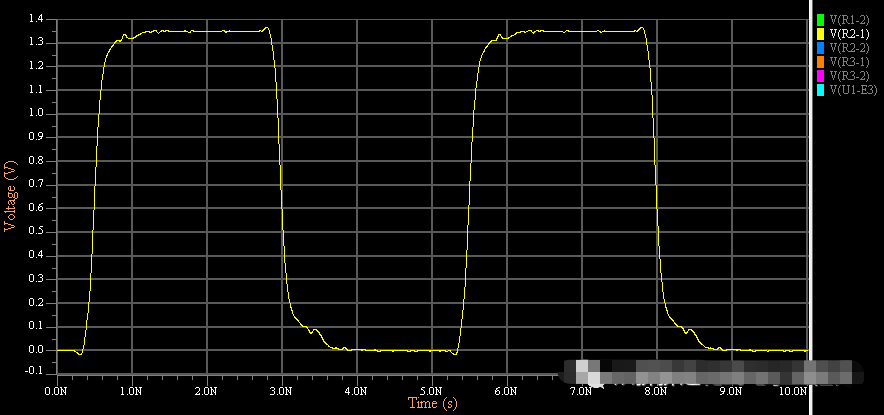

(一)沒有分支時的仿真

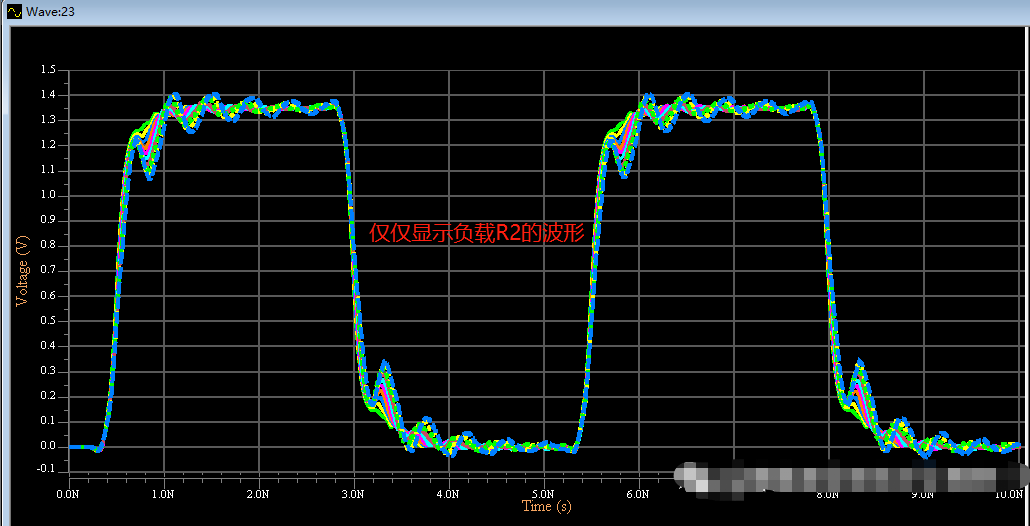

仿真結(jié)果如下:負(fù)載端R2的波形看起來還不錯,沒有反射振鈴,過沖和下沖也很小。

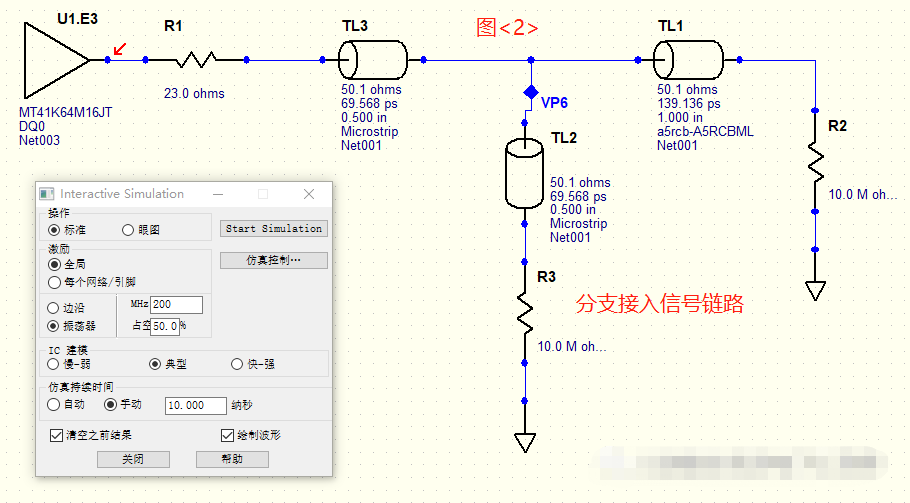

(二)有分支走線存在時的仿真

仿真電路如下:分支TL2和R3已經(jīng)接入信號路徑。

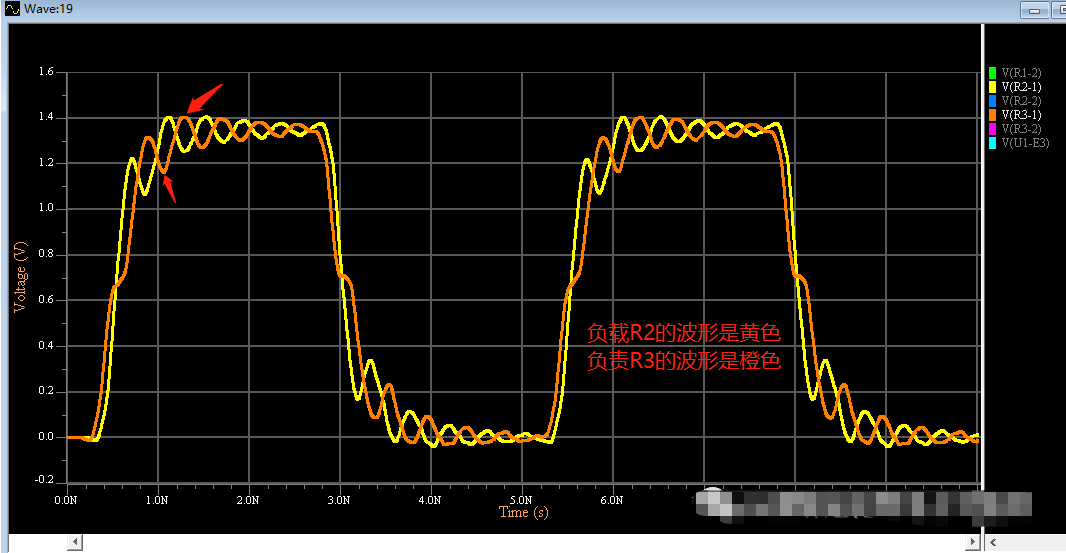

如下是有分支存在時的波形。可以看到負(fù)載R2和負(fù)載R3上的波形非常的差。明顯的多次振鈴,幅度也超過信號電壓幅度的±5%。

針對這種設(shè)計(jì),怎么修改才能是信號滿足負(fù)載端的需求呢?

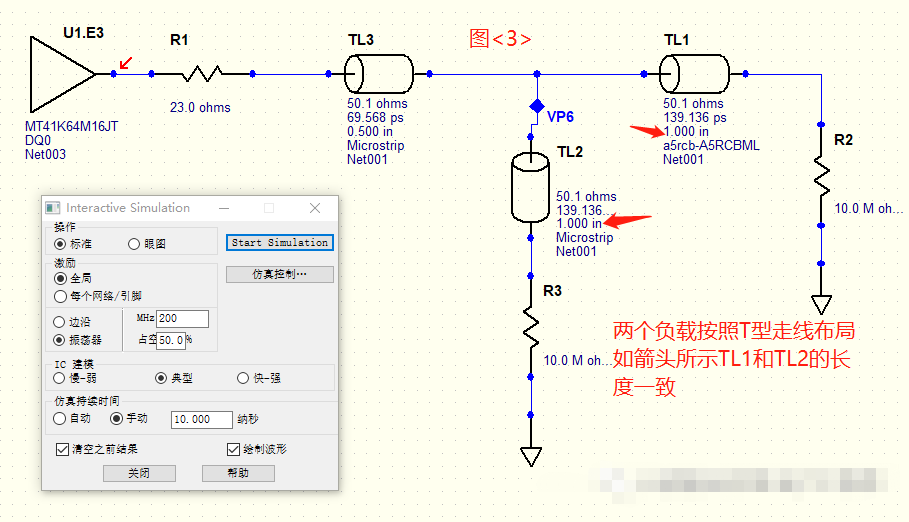

(三)如果仿真電路只有2個負(fù)載,可以考慮T型拓?fù)?/p>

在上圖<2>中,TL1長度為1in,TL2長度為0.5in。即負(fù)載R3距離源端近,負(fù)載R2距離源端遠(yuǎn)。因?yàn)橹挥袃蓚€負(fù)載,可以修改設(shè)計(jì)如下圖<3>所示,TL1=TL2=1in,即兩負(fù)載距離源端一樣,按照T型結(jié)構(gòu)布局和走線。

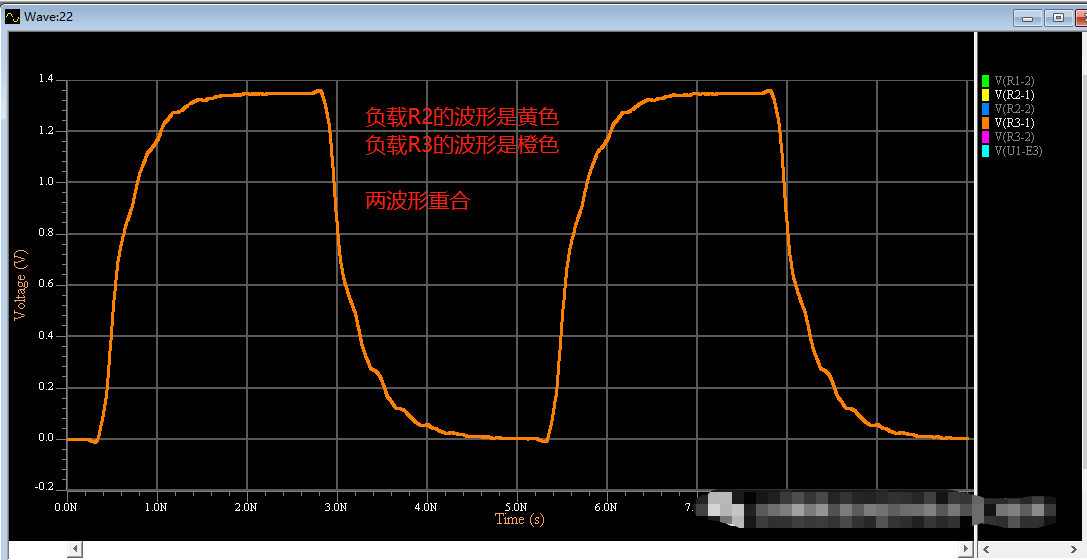

仿真結(jié)果如下:兩負(fù)載的波形完全重合,也沒有過沖、振鈴之類的失真。

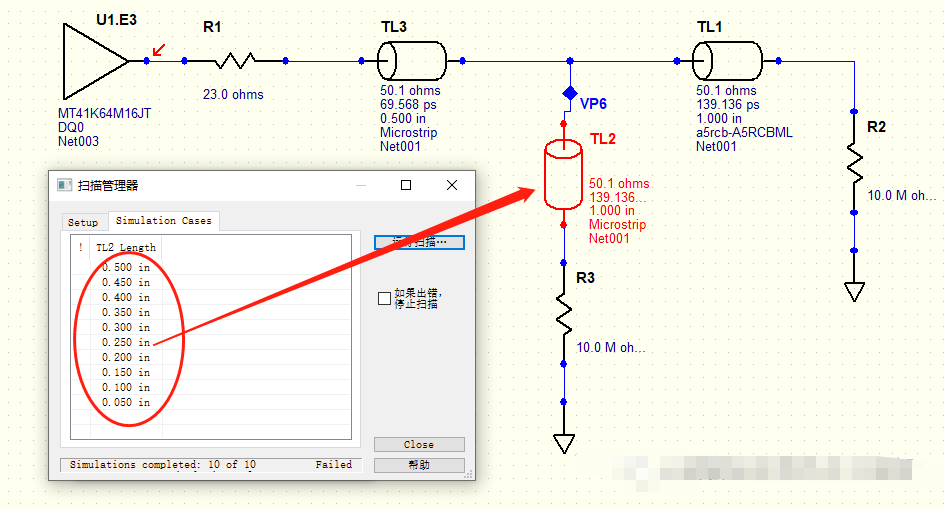

(四)如果多于2個負(fù)載的拓?fù)浣Y(jié)構(gòu),盡量縮短TL2等的距離

如下圖,針對TL2的不同長度做信號仿真。

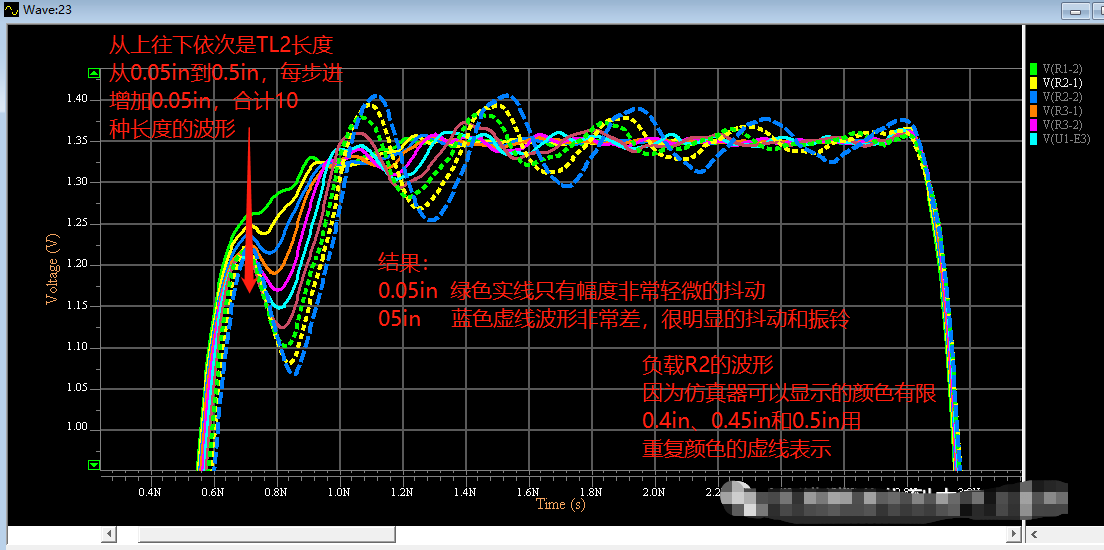

如下是TL2在不同長度下的負(fù)載R2的波形

局部放大后,可以看到。TL2=0.05in的是綠色實(shí)線波形,只有幅度很輕微的抖動。最嚴(yán)重的是TL2=0.5in藍(lán)色虛線波形,抖動和振鈴非常明顯。其他波形隨著TL2長度的縮短,質(zhì)量越來越好。

結(jié)論:多負(fù)載設(shè)計(jì)時,如果是兩個負(fù)載,考慮按照T型拓?fù)湓O(shè)計(jì)。如果大于兩個負(fù)載,按照Flyby拓?fù)浣Y(jié)構(gòu)設(shè)計(jì)時,每個分支的走線都盡量短。在PCB出圖前,最好結(jié)合實(shí)際PCB疊層參數(shù)、PCB走線參數(shù)進(jìn)行仿真,調(diào)整到比較優(yōu)化的階段。

-

芯片

+關(guān)注

關(guān)注

456文章

51155瀏覽量

426325 -

pcb

+關(guān)注

關(guān)注

4324文章

23159瀏覽量

399336 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42357 -

信號完整性

+關(guān)注

關(guān)注

68文章

1416瀏覽量

95576 -

信號反射

+關(guān)注

關(guān)注

0文章

16瀏覽量

10492

發(fā)布評論請先 登錄

相關(guān)推薦

信號完整性(五):信號反射

信號完整性與電源完整性仿真分析

信號完整性簡介及protel信號完整性設(shè)計(jì)指南

信號完整性與電源完整性的仿真

信號完整性之反射(一)

信號完整性之反射(五)

信號完整性之反射(五)

評論