靜電放電(ESD)防護是電子系統設計者和制造商面臨的主要挑戰之一。 這些ESD事件可能在現場發生并導致系統故障,引起短時間系統中斷(軟故障),甚至引起系統芯片功能的物理損壞,從而導致硬故障。

當發生ESD事件時,外部的ESD保護器件應能保護整個系統。 這不僅包括系統芯片,還包括敏感無源組件。

典型ESD故障情況

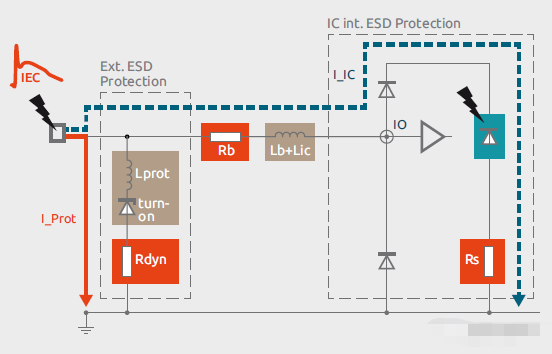

一個簡化的系統等效電路示例如下,用于說明典型ESD故障情況。 電路由外部ESD保護器件、信號PCB銅線寄生器件、芯片內部I/O ESD保護和電源及地間ESD保護組成。 系統動態和準靜態參數分別用棕色和橙色框標出。

列出兩種不同的失效情況如下。

第一種,非常敏感的柵極氧化層。

描述了在ESD脈沖侵入的前幾納秒內,MOSFET晶體管的敏感柵極氧化層被過電壓破壞的情況。 失效場景發生在非常敏感的柵極氧化層上。

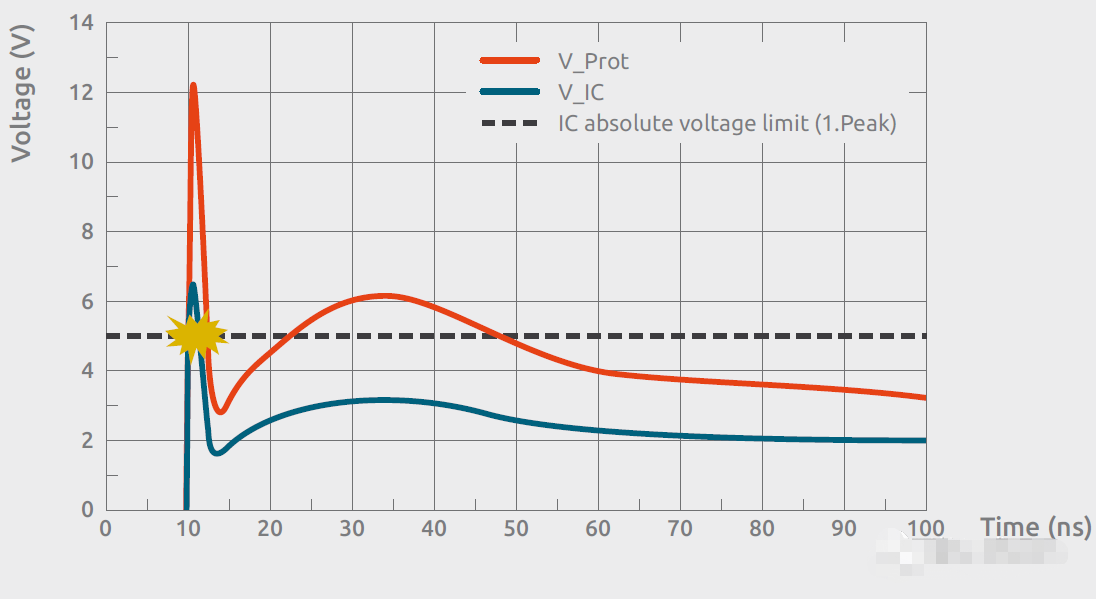

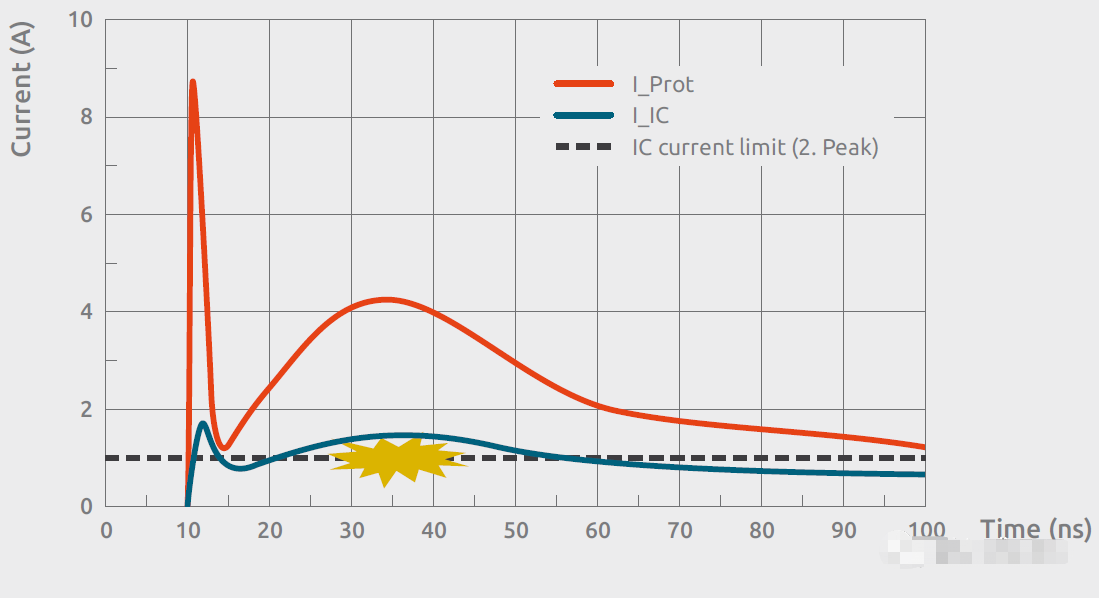

時域電壓評估見下圖:藍色曲線顯示了過電壓發生在IC內部I/O引腳,紅色曲線表示外部ESD保護器件的壓降,虛線黑色定義IC絕對電壓限值。

第二種,IC內部功耗。

系統會遭受由于流經IC內部ESD保護組件的大電流產生的高功耗而導致的熱損壞。

時域電流評估見下圖:藍色曲線為流過IC內部ESD保護器件的電流,紅色曲線為流過外部ESD保護器件的電流,黑線虛線為穩態狀態下IC電流限制值。

所以ESD保護器件應當非常快地導通,并且導通電阻(動態電阻)盡可能地低。 此外,其ESD保護器件寄生電感包括PCB銅線寄生電感應盡可能低。

系統高效ESD設計

系統高效ESD設計(SEED, system efficient ESD design)方法可用于支持工程師建模電子系統并仿真其ESD條件下的行為。 暫態系統分析可用于預測開發階段系統級ESD健壯性,并有助于最小化開發周期及降低成本。

有兩種方法建模系統中芯片模型。 一種是SPICE(Simulation program with integrated circuit emphasis)模型,是晶體管級別的電路描述,是描述物理元素的模型,它包含半導體器件內所有電路描述的詳細信息。 另外一種是行為(behavior)模型,避免了復雜物理工藝的描述,不包含芯片設計廠家專有數據。 此外,還需要增加分立器件,及描述PCB銅軌跡線特征的傳輸線模型等。 其中TLP(transmission line pulse)模型即是其中一種行為模型。

TLP(傳輸線脈沖)測試

TLP是一種相對較新的測量技術,用于表征完整接口或ESD保護組件的特性。

TLP是50 Ω受控阻抗環境中的短時矩形脈沖,可提高測試準確度和測量再現性。 TLP能夠表征具有短脈沖寬度和快上升時間的承壓電應力設備的性能特性。 低占空比可防止發熱。

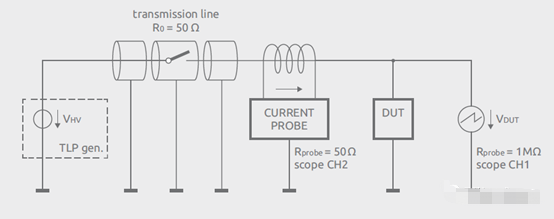

如下圖顯示的TLP測試環境所述:發生器以預先調節的電壓為50 Ω傳輸線充電。 開關閉合,能量應用于被測器件(DUT)。 進入被測器件的電流通過電流探針進行測量,而被測器件上的電壓則使用高速示波器進行監測。 脈沖長度、上升時間和下降時間可在發生器上更改。 施加標準脈沖的持續時間通常為100ns,上升時間和下降時間分別為10ns。 最小可設置轉換時間為300ps。

TLP測試以預定義的步寬從低脈沖電壓到更高電壓逐步開始執行。 如下圖中描繪的TLP測量電壓和電流跡線所示,電壓和電流采樣以20 ns時間窗取平均值。 這段時間窗在100 ns測試脈沖內的70 ns到90 ns間,通過這種基于時間窗的方法可消除噪聲的影響。 此外,時間窗的位置確保系統穩定,從而消除過沖等影響。 每個測量結果都成為TLP圖上的一個點,顯示TLP I-V特性,即構成TLP曲線。

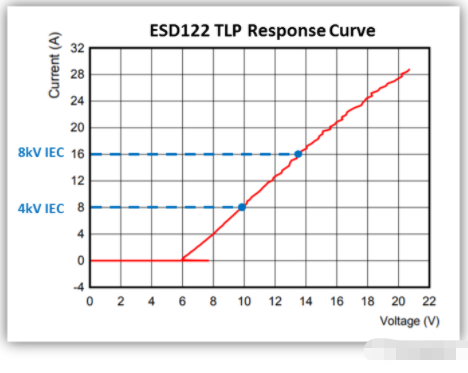

TLP曲線ΔV/ΔI的陡峭度即是動態電阻R 戴恩 ,在選擇ESD和浪涌保護器件時,這是一個重要的考慮參數。

TLP測試可對ESD保護器件及完整系統的接口引腳執行。 根據產生的TLP曲線,我們可以總結出哪個保護器件適合用來安全可靠地保護產品。

基本系統高效ESD設計

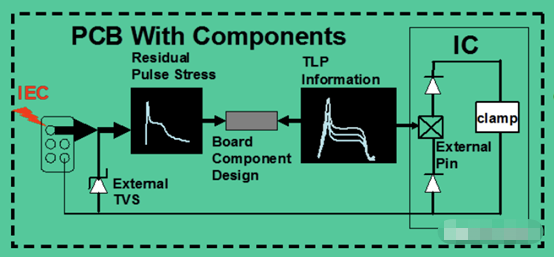

下圖顯示了基于TLP行為模型的基本系統高效ESD設計建模(仿真)。

擴展系統高效ESD設計

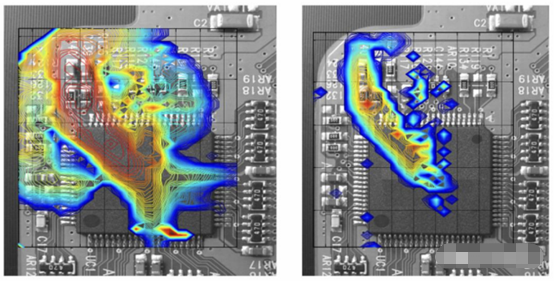

如果EM(Electro magnetic 電磁)掃描工具可以使用,則如下圖所示EMC設計方法擴展系統高效ESD設計。 其可以覆蓋由于低注入電流及電磁輻射等其它電磁問題造成的軟故障。

系統級與元件級ESD脈沖

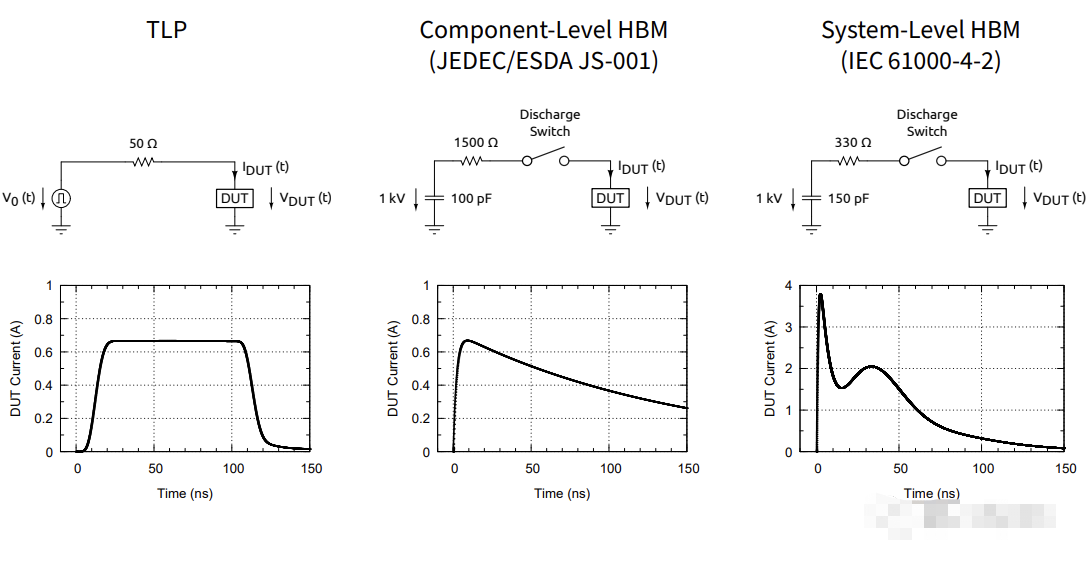

TLP(傳輸線脈沖),

器件級別人體放電模型component-level HBM (JEDEC/ESDA JS-001),

系統級別人體放電模型system-level HBM (IEC 61000-4-2),

電流脈沖波形圖示如下。

圖中顯示三種脈沖有著完全不同脈沖源阻抗,但是其電流脈沖(波形)有著相似的上升時間和持續時間。 所以TLP傳輸線脈沖行為模型很有用,因為它具有類似于系統級別人體放電模型IEC 61000-4-2 ESD沖擊的特征。 所以TLP不止用于表征器件完整接口特性,也用于表征ESD保護組件的特性。

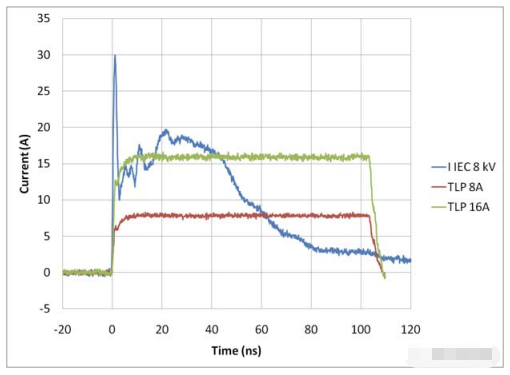

下圖把IEC 61000-4-2 8KV電流波形與TLP 8A及16A電流波形放在同一坐標圖中,則凸顯了TLP的上升時間及持續時間與系統級別人體放電模型的相似性。 實際上對應于芯片內部或外部ESD保護器件的作用時間及耗散能量。

因此,甚至有人在工程估算中將TLP電流與IEC ESD相關聯:

2kV IEC 沖擊 = 4A TLP。

4kV IEC 沖擊 = 8A TLP。

6kV IEC 沖擊 = 12A TLP。

8kV IEC 沖擊 = 16A TLP。

有了這些信息,可以從下圖器件ESD122 TLP響應曲線推斷,在8kV IEC 61000-4-2 ESD沖擊期間,器件ESD122將具有約13.5V的鉗位電壓。 換句話說,當8kV IEC沖擊發生時,您可以預期后續電路暴露在13.5V下約100ns。

ESD工程估算設計舉例

下面例子摘抄于TI網站技術博文。

需求:

選擇一個合適的ESD二極管來保護在19V傳輸線脈沖(TLP)下失效的USB2.0系統。

選擇過程:

USB 2.0差分信號的電壓范圍約為0至3.6V,因此您要確保器件的VRWM大于等于3.6V。

USB 2.0帶寬最高可達480Mbps,因此您需要選擇具有適當電容的器件來保持信號完整性。

您需要滿足IEC 61000-4-2 4級法規,因此ESD二極管必須額定至少支持8kV接觸放電和15kV氣隙放電。

16A TLP的ESD二極管的鉗位電壓必須小于19V,因為系統將在19V時失效。

解決方案:

器件TPD1E04U04是一個很好的解決方案,因為它滿足如下所有這些要求。

這是一個單向ESD二極管,其VRWM為3.6V。

它具有0.5pF的低電容。

它支持IEC 61000-4-2額定值16KV接觸和16kV氣隙放電。

在16A TLP脈沖下,鉗位電壓為9V。

盡管在許多器件規格書中沒能找到TLP失效電壓,但這個例子基本上給出了一些ESD防護器件選擇原理,特別是假設器件廠家給出這一數值情況下。 或是采用絕對最大電壓限制值作為設計輸入,盡管這樣會過設計。

許多器件僅包含器件級別HBM和CDM模型標準ESD額定電壓值,但這些數值僅僅能夠工程估算TLP失效電流,不能完全描述器件內部ESD防護特性。

總結

簡單介紹系統高效ESD設計。

-

ESD

+關注

關注

49文章

2045瀏覽量

173125 -

pcb

+關注

關注

4322文章

23126瀏覽量

398589 -

MOSFET

+關注

關注

147文章

7202瀏覽量

213629 -

保護器件

+關注

關注

1文章

312瀏覽量

13413 -

靜電放電

+關注

關注

3文章

288瀏覽量

44688

發布評論請先 登錄

相關推薦

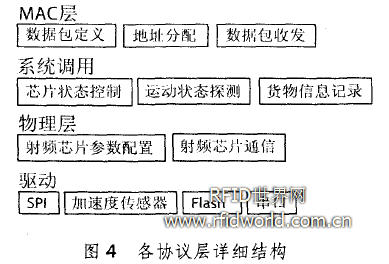

采用有源RFID的倉庫管理系統設計方案

USB 2.0高速端口的ESD保護設計方案

SERDES在數字系統中高效時鐘設計方案

靜電放電(ESD)最佳設計方案資料下載

系統高效ESD設計方案

系統高效ESD設計方案

評論