本應用筆記討論了EIA/TIA-644低壓差分信號(LVDS)標準在3G移動通信中的應用。LVDS具有低功耗和低輻射特性,非常適合WCDMA、EDGE和cdma2000?基站中的高速時鐘和信號分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中繼器和MAX9152交叉點開關。

介紹

3G移動通信,如WCDMA,EDGE和cdma2000,承諾使用手機和其他無線通信設備進行媒體豐富的高速互聯網接入。蜂窩基站將無線手機連接到有線網絡。為了給這些新應用提供帶寬,基站需要處理和分發成倍增加的數字數據。

在基站內部,數據在背板、電纜和電路板內高速移動。低壓差分信號(LVDS)是傳輸此數據的首選信號標準,同時最大限度地減少空間、噪聲和功耗。

本應用筆記討論了使用LVDS串行器、解串器、多端口中繼器、交叉點開關和電平轉換器的數據和時鐘分配應用。重點是與3G基站設計最相關的LVDS電路、架構和規格。

LVDS基站基礎知識

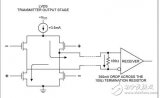

LVDS 是由 TIA/EIA-644 和 IEEE? 1596.3 標準定義的物理層數據接口標準。它專為高速、低功耗和低噪聲點對點通信而設計,通常采用100Ω的過平衡受控阻抗介質。與其他差分信號標準類似,由于磁場的消除,LVDS輻射的噪聲比單端信號少;它更不受噪聲的影響,因為它作為共模信號耦合到兩根導線上(即兩條線路上出現相同水平的噪聲)。此外,LVDS驅動器采用電流導引輸出配置(圖1),與其他差分信號標準中使用的電壓模式驅動器相比,可減少接地反彈并消除直通電流。減小的電壓擺幅(僅±350mV,而正參考發射極耦合邏輯PECL為±800mV,RS-2為±422V)使LVDS能夠實現與PECL相當的數據速率(>800Mbps),同時功耗僅為十分之一。這種高速、低功耗和低噪聲的組合使LVDS成為3G基站中分配的理想信令標準。

圖1.與其他差分信號標準中使用的電壓模式驅動器相比,使用電流導引輸出配置的LVDS驅動器可減少接地反彈。LVDS驅動器還消除了擊穿電流。

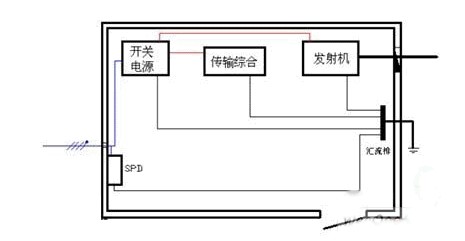

除了上述優點外,LVDS串行器和解串器還將為基站設計節省大量空間和成本。為了滿足3G網絡所需的帶寬,與2G系統相比,新基站需要更多的卡。對于執行擴頻、交錯和錯誤控制技術所需的大量數字信號處理的基帶卡尤其如此。隨著這些卡之間的數據吞吐量增加,傳統的TTL背板將不再足夠。TTL不能以足夠高的速度進行切換,而寬并聯總線需要大而昂貴的背板,這增加了系統尺寸和成本。MAX9205串行器和MAX9206解串器通過將11條TTL線路(10條數據+1條時鐘)轉換為一對高速LVDS來解決這個問題(圖2)。這種方法將互連復雜性降低了五倍。在3G系統等卡數較多的基站中,這兩種設備可節省大量空間和成本。

圖2.LVDS串行器與解串器(未顯示)結合使用,消除了使用標準TTL信令時所需的寬數據總線和相關的大型昂貴背板。此外,這些LVDS電路以3G網絡所需的速度切換。

MAX9205串行器將10位寬、并行LVTTL/LVCMOS數據轉換為LVDS串行數據流。內部添加的高狀態起始位和低狀態停止位對10位并行輸入數據進行框架處理,并確保串行數據流中的轉換。因此,每個12位并行輸入傳輸10個串行位。MAX9205接受16MHz至40MHz的寬參考時鐘,產生192Mbps (12位x 16MHz)至480Mbps (12位x 40MHz)的串行數據速率。但是,由于只有10位來自輸入數據,因此實際吞吐量是參考時鐘頻率的10倍。MAX9206解串器接收MAX9205的串行輸出,并將其轉換回10位寬的并行數據。由于解串器從串行數據流中恢復時鐘和數據,因此消除了并行總線時存在的時鐘到數據和數據到數據的偏斜。MAX9205和MAX9206共同構成減少卡間互連的完整方案。

將這些功能劃分為兩個IC,而不是單個集成SerDes,非常適合通常采用單向鏈路的3G基站。例如,基帶接收卡可能專用于對從無線電收發器卡接收的數據執行信號處理。使用此處描述的方法,基帶卡上只需要反序列化。因此,與獨立解串器相比,集成 SerDes 會消耗額外的空間并增加成本。

在已經采用串行背板的基站中,LVDS多端口中繼器可以進一步減少電路板空間和成本。大多數基站架構包含必須將其數據廣播或傳輸到多個目標卡的卡。例如,許多系統并行使用多個基帶卡來處理來自單個無線電收發器卡的接收數據。這種架構的暴力實現要求無線電卡包含與目標基帶卡上的解串器一樣多的串行器(圖 3a)。通過使用多端口中繼器,如MAX9150,串行器數量可減少多達10:1(圖3b)。當與單個串行器配合使用時,MAX9150僅用一個串行器代替10個串行器。此架構僅對指定具有足夠低抖動的多端口中繼器有效。抖動是與事件或信號邊沿理想時序的偏差,會阻止解串器成功從串行位流中恢復時鐘和數據。典型LVDS串行器/解串器對的抖動預算可低至幾百皮秒。信號路徑中的走線、電纜和連接器引起的抖動進一步降低了該預算。因此,串行器和解串器之間的信號路徑中的其他器件必須表現出極低的抖動。MAX9150僅保證120ps (最大值)的峰峰值抖動。

圖 3a.當多個基帶卡處理從無線電收發器卡接收的數據時,無線電卡通常包含與目標基帶卡上的解串器一樣多的串行器。

圖 3b.通過使用像MAX9150這樣的多端口中繼器,無線電收發器卡上的串行器數量可以減少多達10:1。

在高速串行信號路徑的其他部分,基站架構通常需要簡單的開關、多路復用和重復功能。與多端口中繼器示例一樣,這些功能必須在對抖動預算影響最小的情況下提供。MAX9152 2x2 LVDS交叉點開關在一個封裝中提供多種功能。它包括兩個LVDS/LVPECL輸入、兩個LVDS輸出和兩個邏輯輸入,用于確定哪些輸入連接到IC內部的哪些輸出。它可以被編程為將任何輸入連接到一個或兩個輸出。它可用于以下配置:2x2 交叉點開關、2:1 多路復用器、1:2 解復用器、1:2 扇出緩沖器或雙中繼器。這種靈活性使MAX9152非常適合用于容錯保護切換、用于診斷的環回切換、用于數據分配的扇出緩沖以及用于長距離通信的信號再生。MAX9152的超低120ps (最大值)峰峰值抖動確保高速串行鏈路中的可靠通信。

在低速信號路徑中,如時鐘分配網絡和控制總線,LVDS還通過取代TTL和RS-422等舊信號標準來提高性能。在對輻射噪聲具有高靈敏度的基站無線電收發器卡中,LVDS是分配PLL頻率合成器使用的參考時鐘的理想信號標準。雖然這些電路不需要LVDS的速度(基站參考時鐘通常工作在幾十MHz),但它們受益于LVDS的低功耗和低輻射噪聲。用于仲裁、握手和卡間其他外設通信的低速控制總線也受益于LVDS的噪聲和功耗降低。電平轉換器僅用于在LVTTL/LVCMOS和LVDS之間轉換信號,為構建LVDS時鐘分配網絡和控制總線提供了一種簡單的方法,可以從現有的LVTTL/LVCMOS設計中控制總線。Maxim的單線、雙線和四線驅動器和接收器系列是此類網絡的理想構建模塊,因為它們包括一些最小的(SC70和SOT23封裝)和最低的脈沖偏斜器件。(脈沖偏斜是這些器件抖動的主要指標。

總結

通過利用LVDS在時鐘分配、控制總線、背板和其他高速信號分配領域的優勢,3G基站可提供更高帶寬的無線服務,而無需相應增加成本、尺寸和功耗。本文討論的產品不僅通過LVDS信令標準提供這些優勢,而且還通過它們支持的架構和拓撲提供這些優勢。毫無疑問,全面熟悉LVDS技術、產品和應用對于任何開發下一代蜂窩基站的工程師來說都是必不可少的。

審核編輯:郭婷

-

lvds

+關注

關注

2文章

1045瀏覽量

65943 -

串行器

+關注

關注

0文章

116瀏覽量

14448 -

解串器

+關注

關注

1文章

107瀏覽量

13289

發布評論請先 登錄

相關推薦

3G 工業監控|3G工地監控|3G視頻監控

西門子3G WCDMA基站NB-880

3G無線基站技術及標準化

完整3G移動基站電源防雷解決方案

以TD-SCDMA為例的3G基站現場測試簡單介紹

AD6655在3G基站系統中的應用是什么?

LVDS促進3G基站的高速信號傳送

LVDS促進3G基站的高速信號傳送

LVDS實現3G基站的高速信號傳送

LVDS支持3G基站的高速信號分配

LVDS支持3G基站的高速信號分配

評論