觸發器是構成時序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進制信息的邏輯電路。在之前的文章中已經介紹過觸發器了,這里再介紹一下其他類型的觸發器。

1、基本RS鎖存器

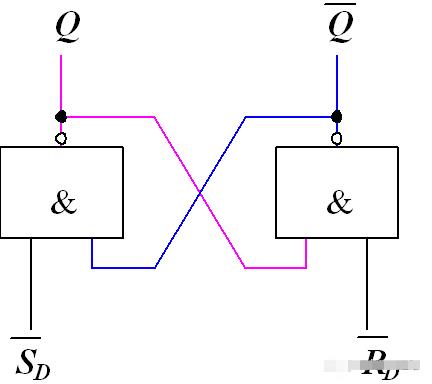

最簡單的觸發器是基本RS觸發器,基本RS鎖存器可以由兩個與非門構成,電路如下:

基本RS鎖存器由電平觸發,并且有一個重要的約束條件:/SD和/RD不能同時為零。即:/SD+/RD=1

2、同步RS鎖存器

許多時候,我們希望觸發器只有在時鐘來臨時,輸出狀態改變,其它時候,觸發器維持,因為這樣做可以讓多個電路單元的狀態同時得以改變,這個時鐘,我們稱為同步時鐘。

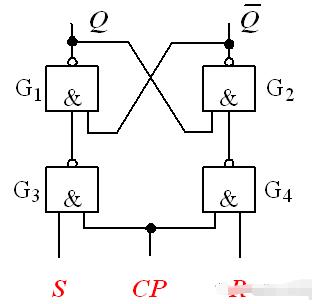

如下圖所示,將基本RS鎖存器的輸入端分別經過一個與非門作為鐘控信號。就變成了同步RS鎖存器。

同步RS鎖存器與基本RS鎖存器的不同之處在于,只有時鐘CP=1的時候,輸出狀態才能被改變。但是,同步鎖存器也具有一個約束條件,就是當CP=1時,S和R不能同時為1。

此外,同步RS鎖存器還有一個不足之處在于:當CP=1時,S和R若多次改變,每次改變都會影響輸出。這種現象,稱為空翻現象。

3、主從RS觸發器

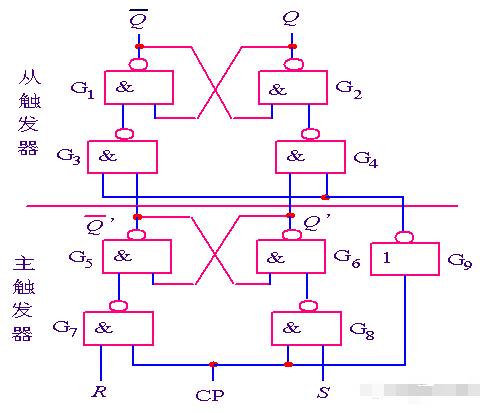

為了解決空翻為題,將兩個同步RS觸發器串聯,電路如下:

主從觸發器的觸發翻轉分為兩個節拍:

(1)當CP=1時,CP’=0,從觸發器被封鎖,保持原狀態不變:主觸發器工作,接收R和S端的輸入信號。

(2)當CP由1躍變到0時,即CP=0、CP’=1。主觸發器被封鎖,輸入信號R、S不再影響主觸發器的狀態;從觸發器工作,接收主觸發器輸出端的狀態。

主從觸發器的輸出改變僅僅取決于CP的下降沿時刻。有效的解決了空翻問題。但是,主從RS觸發器仍然存在約束條件:R、S不能同時為1。

4、主從JK觸發器

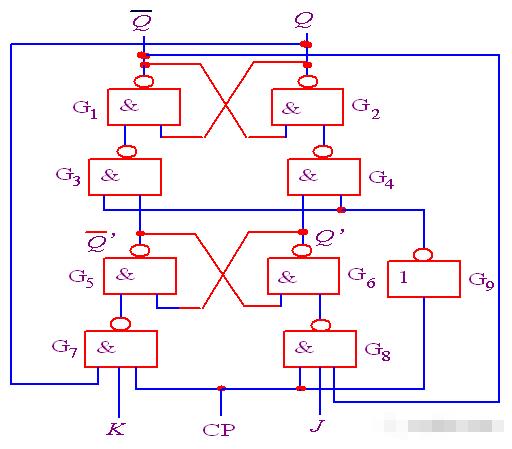

從基本RS鎖存器可以看出,基本RS鎖存器和同步RS鎖存器的輸出Q和/Q不會同時等于0,利用這個特點,若將主從RS鎖存器的兩個輸出分別反饋至輸入,即可解除這個約束。電路如下:

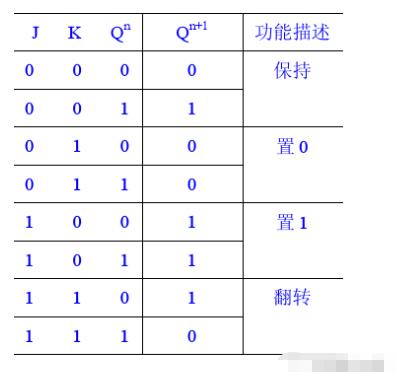

真值表如下:

功能描述:00不翻11翻,互補輸入,J為打入端。

5、D觸發器

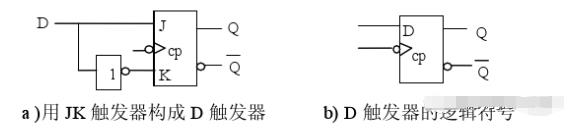

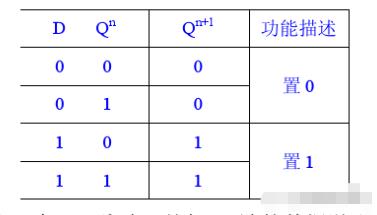

JK觸發器可以很方便地構成D觸發器,電路圖和真值表如下所示。

6、T觸發器

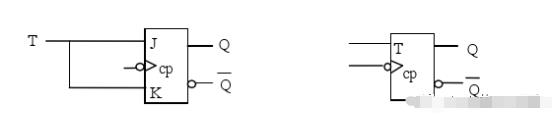

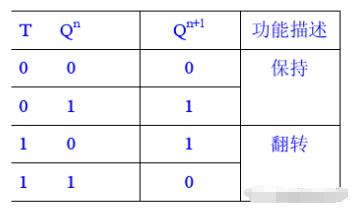

把JK觸發器的兩個輸入端J、K連起來,作為一個輸入端T,就構成T觸發器了,電路圖和真值表如下所示。

因為T=J=K,所以當T=0的時候,CP脈沖來后觸發器維持原狀不變。當T=1的時候,每一個CP脈沖來的時候,觸發器狀態翻轉一次。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42609 -

RS

+關注

關注

3文章

140瀏覽量

109887 -

鎖存器

+關注

關注

8文章

906瀏覽量

41495 -

JK觸發器

+關注

關注

1文章

43瀏覽量

15895 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132

發布評論請先 登錄

相關推薦

什么是邊沿觸發器_邊沿D觸發器介紹

觸發器的類型介紹

觸發器的類型介紹

評論