3.1 模塊介紹

模塊( module)是 Verilog 的基本描述單位, 是用于描述某個設計的功能或結構及與其他模塊通信的外部端口。

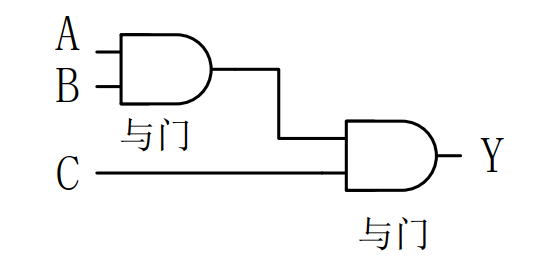

模塊在概念上可等同一個器件,就如調用通用器件(與門、三態門等)或通用宏單元(計數器、ALU、 CPU)等。因此,一個模塊可在另一個模塊中調用,一個電路設計可由多個模塊組合而成。一個模塊的設計只是一個系統設計中的某個層次設計,模塊設計可采用多種建模方式。

Verilog 的基本設計單元是―模塊‖。采用模塊化的設計使系統看起來更有條理也便于仿真和測試,因此整個項目的設計思想就是模塊套模塊,自頂向下依次展開。 在一個工程的設計里,每個模塊實現特定的功能,模塊間可進行層次的嵌套。

對大型的數字電路進行設計時,可以將其分割成大小不一的小模塊,每個小模塊實現特定的功能,最后通過由頂層模塊調用子模塊的方式來實現整體功能,這就是 Top-Down 的設計思想。 本書主要以 Verilog 硬件描述語言為主,模塊是 Verilog 的基本描述單位,用于描述每個設計的功能和結構,以及其他模塊通信的外部接口。

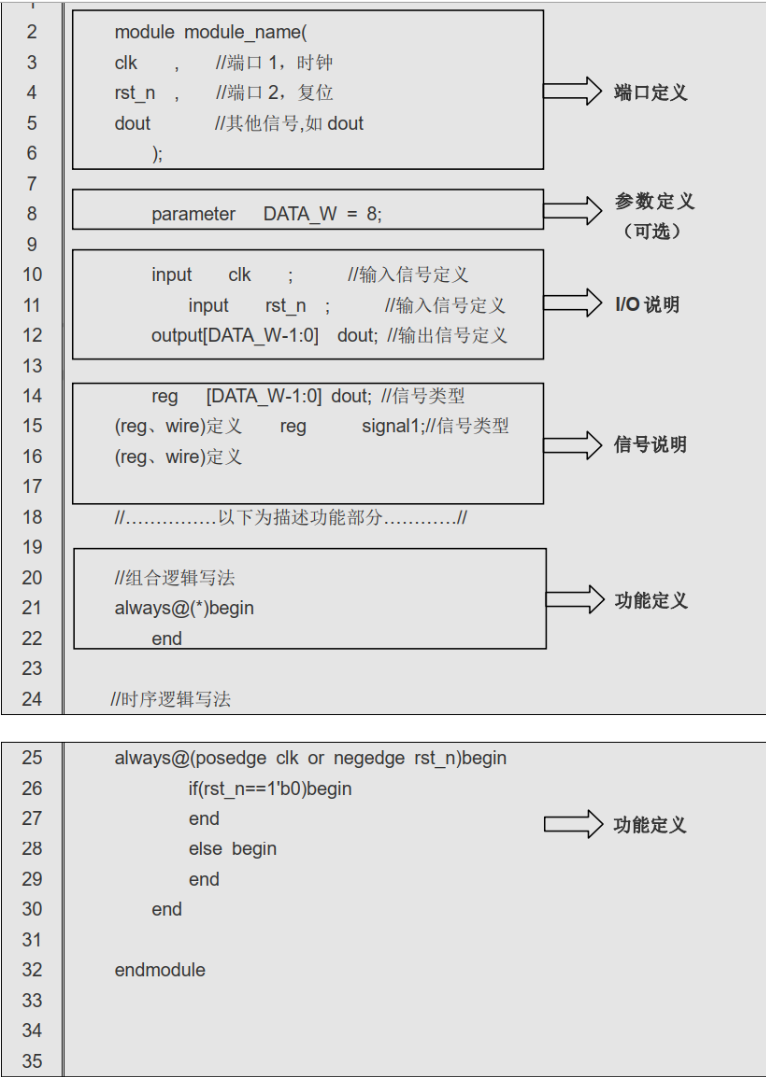

模塊有五個主要部分:端口定義、參數定義(可選)、 I/O 說明、內部信號聲明、功能定義。模塊總是以關鍵詞 module 開始,以關鍵詞 endmodule 結尾。它的一般語法結構如下所示:

3.2 模塊名和端口定義

第 1 至 5 行聲明了模塊的名字和輸入輸出口。其格式如下:module 模塊名(端口 1,端口 2,端口 3, ……);其中模塊是以 module 開始,以 endmodule 結束。模塊名是模塊唯一的標識符, 一般建議模塊名盡量用能夠描述其功能的名字來命名,并且模塊名和文件名相同。

模塊的端口表示的是模塊的輸入和輸出口名,也是其與其他模塊聯系端口的標識。

3.3 參數定義

第 8 行參數定義是將常量用符號代替以增加代碼可讀性和可修改性。這是一個可選擇的語句,用不到的情況下可以省略,參數定義一般格式如下:

parameter DATA_W = x;

3.4 接口定義

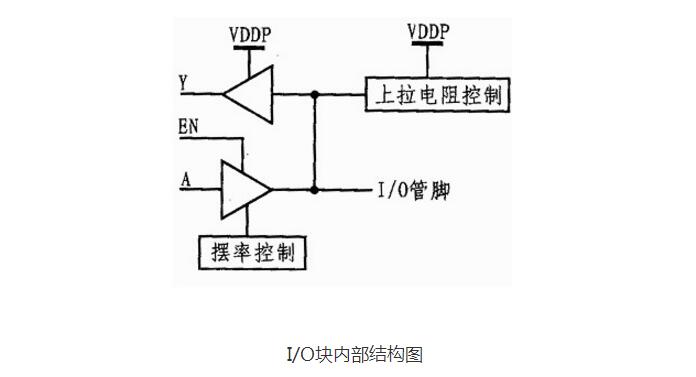

第 9 至 12 行是 I/O(輸入/輸出)說明,模塊的端口可以是輸入端口、輸出端口或雙向端口。其說明格式如下。

輸入端口: input [信號位寬-1 : 0] 端口名 1;

input [信號位寬-1 : 0] 端口名 2;

……;

輸出端口:output [信號位寬-1 : 0] 端口名 1;

output [信號位寬-1 : 0] 端口名 2;

……;

雙向端口: inout [信號位寬-1 : 0] 端口名 1;

inout [信號位寬-1 : 0] 端口名 2;

……;

3.5 信號類型

第 14 至 17 行定義了信號的類型。 這些信號是在模塊內使用到的信號,并且與端口有關的 wire和 reg 類型變量(即線網型與寄存器型)。 其聲明方式如下:

reg [width-1 : 0] R 變量 1, R 變量 2 ……;

wire [width-1 : 0] W 變量 1, W 變量 2……;

如果沒有定義信號類型,默認是 wire 型,并且信號位寬為 1。

3.6 功能描述

第 21 至 31 行是功能描述部分。模塊中最重要的部分是邏輯功能定義部分, 有三種方法可在模塊中產生邏輯。

用“assign”聲明語句,如描

述一個兩輸入與門: assign a = b & c。 詳細功能見“功能描述-組合邏輯”一節。

用“always”塊。即前面介紹的時序邏輯和組合邏輯。

模塊例化。詳細功能見“模塊例化”一節。

3.7 模塊例化

對數字系統的設計一般采用的是自頂向下的設計方式, 可將系統劃分成幾個功能模塊,每個功能模塊再劃分成下一層的子模塊。每個模塊的設計對應一個 module , 每個 module 設計成一個 Verilog HDL 程序文件。因此,對一個系統的頂層模塊采用結構化設計,即頂層模塊分別調用了各個功能模塊。

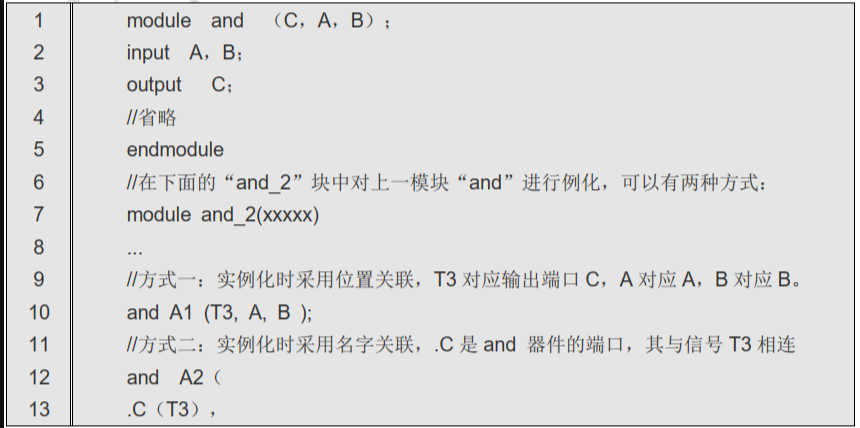

一個模塊能夠在另外一個模塊中被引用,這樣就建立了描述的層次。模塊實例化語句形式如下:

module_nameinstance_name(port_associations) ;

信號端口可以通過位置或名稱關聯, 但是關聯方式不能夠混合使用。端口關聯形式如下:port_expr / /通過位置。.

PortName (port_expr) / /通過名稱。

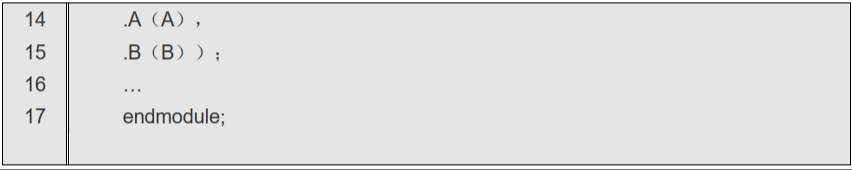

建議:在例化的端口映射中請采用名字關聯,這樣,當被調用的模塊管腳改變時不易出錯。在實例化中,可能有些管腳沒用到,可在映射中采用空白處理,如:

輸入管腳懸空端口的輸入為高阻 Z,由于輸出管腳是被懸空的,該輸出管腳廢棄不用。

————————————————

版權聲明:本文為CSDN博主「原來如此呀」的原創文章,遵循CC 4.0 BY-SA版權協議,轉載請附上原文出處鏈接及本聲明。

原文鏈接:https://blog.csdn.net/Royalic/article/details/121151907

-

模塊

+關注

關注

7文章

2731瀏覽量

47661 -

cpu

+關注

關注

68文章

10901瀏覽量

212669 -

Verilog

+關注

關注

28文章

1351瀏覽量

110259 -

計數器

+關注

關注

32文章

2261瀏覽量

94873 -

器件

+關注

關注

4文章

324瀏覽量

27903

發布評論請先 登錄

相關推薦

如何快速入門FPGA?

如何快速入門FPGA

求FPGA入門資料

FPGA入門:內里本質探索——器件結構

Xilinx FPGA無痛入門,海量教程免費下載

Xilinx FPGA入門連載38:SRAM讀寫測試之設計概述

Xilinx FPGA入門之PLL實例的基本配置

FPGA模塊化設計與AlteraHardCopy結構化ASIC

FPGA入門之什么是FPGA

FPGA入門之模塊結構

FPGA入門之模塊結構

評論