上拉是用電阻將不確定的信號(hào)箝位到高電平,電阻器還充當(dāng)限流器。同樣,下拉意味著通過(guò)電阻將不確定信號(hào)箝位到低電平。上拉是向器件輸入電流,下拉是輸出電流。

I 上拉電阻s

通常,非集電極(或漏極)開(kāi)路輸出電路(如普通柵極電路)只能提供有限的電流和電壓,但上拉電阻可以為電路創(chuàng)建輸出電流通道。

1. 概念

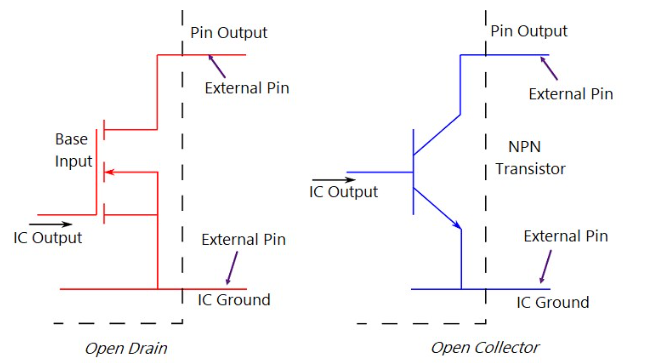

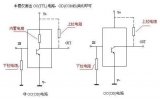

(1) 如果輸出電平為OC(集電極開(kāi)路,TTL)或OD(漏極開(kāi)路,CMOS),則在沒(méi)有上拉電阻的情況下將無(wú)法工作。沒(méi)有電源,任何電阻器都無(wú)法輸出高電平。

(2)如果電路中已經(jīng)有上拉電阻,但電阻過(guò)大,壓降過(guò)高,則輸出電流過(guò)大時(shí)輸出電平會(huì)降低。在這種情況下,可以施加一個(gè)上拉電阻器來(lái)為電阻器提供電流并“上拉”電平。將電阻與IC內(nèi)部的上拉電阻并聯(lián),總電流隨總電阻的減小而增加。這種方法也可用于匹配柵極電路的電平。還應(yīng)該注意的是,在線(xiàn)性范圍內(nèi)工作的電阻的上拉電阻不能太小。

2. 使用原因

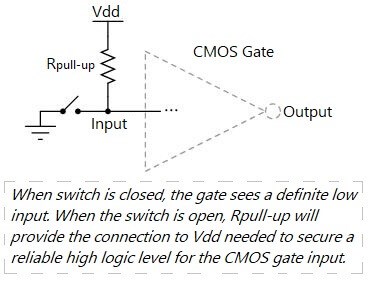

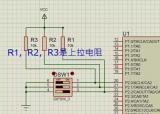

通常,當(dāng)IC用于單鍵觸發(fā)時(shí),如果沒(méi)有內(nèi)阻,為了保持鍵未觸發(fā)或觸發(fā)后恢復(fù)到原始狀態(tài),必須在IC外部連接另一個(gè)電阻。

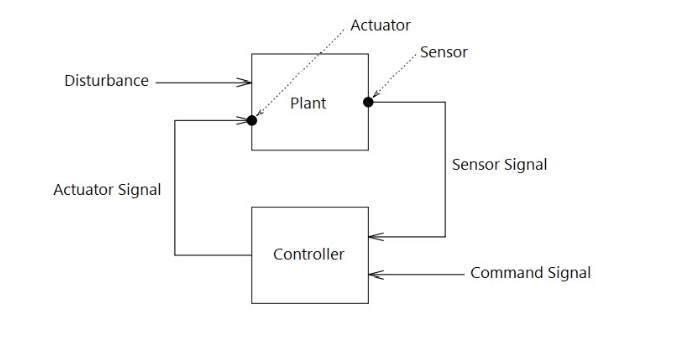

數(shù)字電路有三種狀態(tài):高電平、低電平和高電阻狀態(tài)。 在某些應(yīng)用中,高電阻狀態(tài)是不可取的,可以根據(jù)設(shè)計(jì)要求通過(guò)向上或向下拉來(lái)穩(wěn)定。

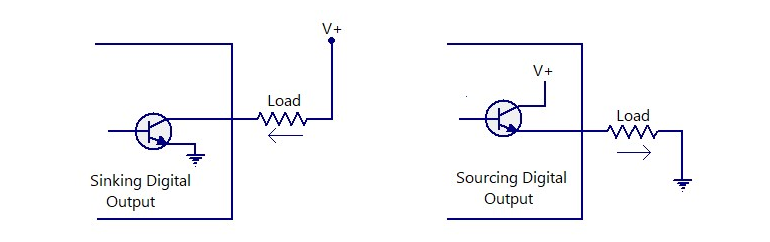

有些 I/O 端口可以設(shè)置,有些不能,有些端口是內(nèi)置的,有些是外部連接的。I/O端口的輸出類(lèi)似于晶體管,當(dāng)它連接到電阻器和電源時(shí),電阻器成為上拉電阻。同樣,端口在正常情況下處于高電平,但是當(dāng)它通過(guò)電阻連接到地時(shí),電阻器會(huì)變成下拉電阻。

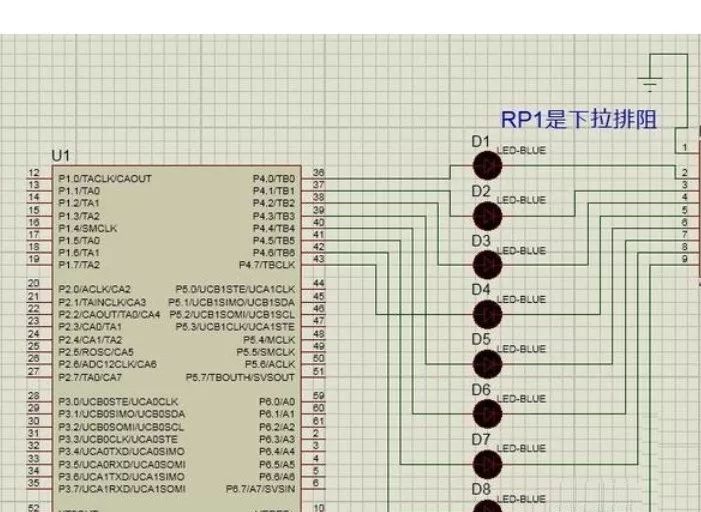

上拉電阻用于在總線(xiàn)驅(qū)動(dòng)能力不足時(shí)提供電流。一般來(lái)說(shuō),上拉會(huì)增加電流,下拉電阻用于吸收電流。

三、上拉電阻的功能與缺陷

(1) 功能

● 當(dāng)TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果電路的輸出高電平低于CMOS電路的最低高電平(一般為3.5V),則需要在TTL的輸出端連接一個(gè)上拉電阻,以提高輸出高電平。

● 柵極電路必須使用上拉電阻來(lái)提高輸出高電平。

● 為了增強(qiáng)輸出引腳的驅(qū)動(dòng)能力,一些微控制器通常使用上拉電阻。

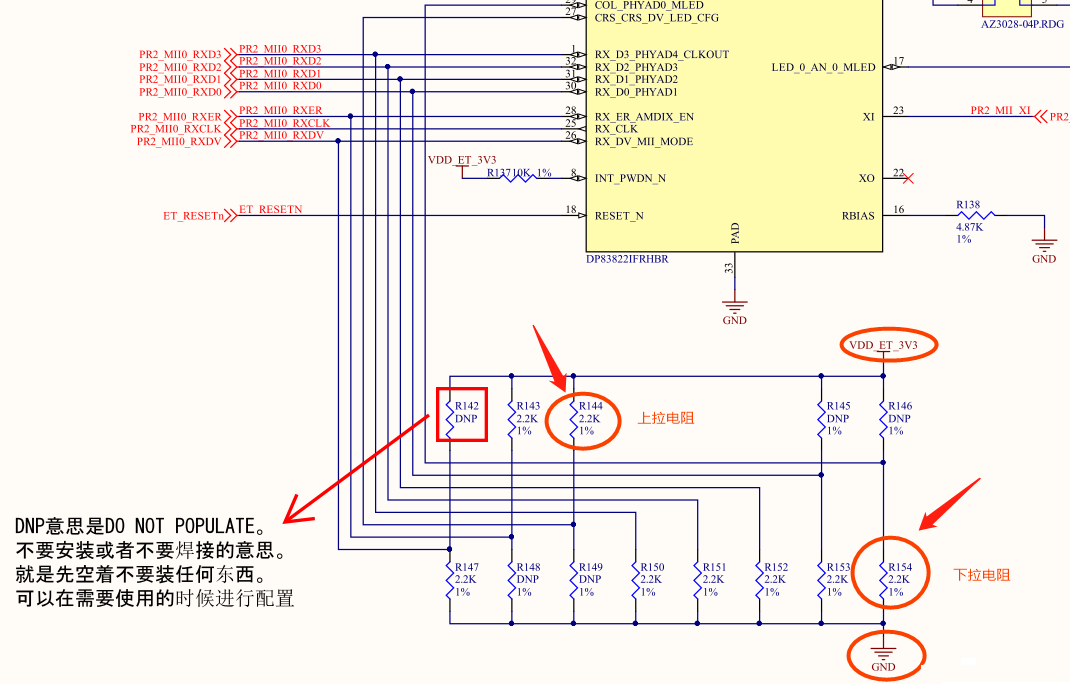

● 在CMOS芯片上,為防止靜電造成損壞,未使用的引腳不應(yīng)浮動(dòng)。相反,連接一個(gè)上拉電阻以降低輸入阻抗,并為負(fù)載屏蔽提供路徑。

● 在芯片引腳上增加一個(gè)拉電阻,提高輸出電平,從而提高輸入信號(hào)的噪聲容限,增強(qiáng)抗干擾能力。

● 提高主線(xiàn)的抗電磁信號(hào)能力。如果引腳浮動(dòng),則很容易受到外部電磁干擾的影響。

●長(zhǎng)線(xiàn)傳輸中的不匹配電阻容易引起反射波干擾。使用拉電阻可以匹配電阻并有效抑制干擾。

(2) 缺陷

當(dāng)電流流過(guò)上拉電阻時(shí),上拉電阻通常會(huì)消耗額外的能量,這可能會(huì)導(dǎo)致輸出電平延遲。此外,一些邏輯芯片對(duì)通過(guò)上拉電阻引入的電源的瞬態(tài)很敏感,因此需要帶濾波的獨(dú)立電壓源。

4. 注意事項(xiàng)

需要注意的是,如果上拉電阻過(guò)大,輸出電平會(huì)出現(xiàn)延遲(RC延遲)。

通常,CMOS柵極電路的輸出引腳不能浮動(dòng),而應(yīng)連接到上拉電阻并設(shè)置為高電平。

上拉電阻的選擇原則是:

(1)考慮到芯片的省電和吸電流能力,電阻應(yīng)足夠大。如果電阻大,電流會(huì)小。

(2)上拉電阻應(yīng)小,以保證足夠的驅(qū)動(dòng)電流。當(dāng)電阻小時(shí),電流很大。

(3)對(duì)于高速電路,過(guò)大的上拉電阻的邊緣可能會(huì)變平。

5. 上拉電阻的計(jì)算原理

(1)最大值的計(jì)算原理

確保上拉電阻明顯小于負(fù)載阻抗,以便輸出在高電平下有效。

例如,如果負(fù)載阻抗為1K,電源電壓為5伏,如果要求高電平不低于4.5伏,則最大上拉電阻R≧1K,這意味著最大值為1k。如果超過(guò) 1k,則輸出高電平將小于 4.5 伏。

(2)最小值的計(jì)算原則

確保不超過(guò)晶體管的額定電流。如果晶體管不是場(chǎng)效應(yīng)管而是普通的三極管,也可以根據(jù)飽和電流計(jì)算最小值。

例如,如果Rmin= 5v/47mA = 106歐姆,如果電阻小于該電阻,晶體管將過(guò)飽和。如果大于此值,則管的導(dǎo)體電阻會(huì)變大,不利于低電平輸出。

6.上拉電阻的應(yīng)用

可以在邏輯門(mén)與其輸入端之間放置一個(gè)上拉電阻。例如,輸入信號(hào)可以通過(guò)電阻上拉,開(kāi)關(guān)或跳線(xiàn)可以將輸入連接到地面。此外,它還可用于信息分配和選擇,或 外部設(shè)備信號(hào)的錯(cuò)誤檢測(cè)和校正。

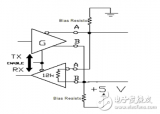

當(dāng)邏輯器件沒(méi)有提供電流時(shí),上拉電阻也可以工作。集電極開(kāi)路具有上拉電阻,此類(lèi)電路的輸出信號(hào)通常用于驅(qū)動(dòng)外部設(shè)備,將邏輯電路和連接到一條總線(xiàn)的多個(gè)設(shè)備組合在一起。

此外,上拉電阻可以與其他邏輯器件焊接在同一電路板上。在許多微控制器中,預(yù)計(jì)會(huì)將外部可編程上拉電阻施加到嵌入式控制應(yīng)用中,以減少對(duì)外部元件的需求。

II 下拉電阻器

下拉電阻直接接地,當(dāng)它連接到二極管時(shí),端連接到低電平。它被稱(chēng)為下拉電阻,因?yàn)殡娐饭?jié)點(diǎn)的電平被下拉到地。

1. 基本 C值

(1) 通過(guò)電阻將不確定信號(hào)接地,并將其固定在低電平。

(2) 下拉是輸出器件的電流

(3) 當(dāng)與下拉電阻連接的IO端口設(shè)置為輸入狀態(tài)時(shí),其正常狀態(tài)處于低電平。

2. 晶體管基板上的下拉電阻

由于以下原因,在晶體管基極上施加下拉電阻:

(1) 防止噪音干擾

使用下拉電阻可以防止晶體管因噪聲信號(hào)的影響而發(fā)生故障,從而使晶體管截止更加可靠。

晶體管的基極不能懸掛。當(dāng)輸入信號(hào)不確定時(shí)(如處于高阻抗?fàn)顟B(tài)),增加一個(gè)下拉電阻可以有效地將電路接地。

特別是當(dāng)GPIO(通用輸入/輸出)連接到這個(gè)基座時(shí),如果帶有GPIO的IC剛剛上電并初始化,GPIO的內(nèi)部也處于導(dǎo)通狀態(tài),非常不穩(wěn)定,容易產(chǎn)生噪聲,導(dǎo)致故障。在這種情況下,增加一個(gè)下拉電阻可以消除這種影響。如果當(dāng)其持續(xù)時(shí)間很短時(shí)出現(xiàn)尖銳的脈沖電平,則電壓很容易被電阻下拉,否則就不能下拉。

(2)避免時(shí)滯

當(dāng)晶體管開(kāi)關(guān)打開(kāi)時(shí),最好使用較短的ON和OFF時(shí)間。為了防止晶體管中剩余電荷在關(guān)斷狀態(tài)下造成的時(shí)間滯后,在基極和發(fā)射極之間增加了一個(gè)下拉電阻進(jìn)行放電。如果有高頻和深度飽和,應(yīng)特別注意。

(3) 便于設(shè)置偏置電壓

在基極上增加一個(gè)下拉電阻,主要是設(shè)置一個(gè)偏置電壓,這樣就不會(huì)有信號(hào)失真。特別是當(dāng)輸入信號(hào)中有交流電時(shí),如果溫度升高,Ic就會(huì)增加,導(dǎo)致Ie的增大和Re上的電壓下降。由于Vbe = Vb-IeRe,而Vb基本上由下拉電阻保持,所以Vbe減小了。Vbe的降低使Ib降低,導(dǎo)致Ic的增加,使Ic基本恒定。這也是反饋控制的原理。

同時(shí),為了防止輸入電流過(guò)大,增加一個(gè)電阻可以分一部分電流,這樣大電流就不會(huì)直接流入晶體管而損壞它。

MOS晶體管還需要一個(gè)下拉電阻來(lái)設(shè)置柵極偏置。由于MOS晶體管內(nèi)部的三個(gè)引腳相互絕緣,因此會(huì)產(chǎn)生電容效應(yīng)。當(dāng)信號(hào)消失時(shí),內(nèi)部等效電容可以通過(guò)下拉電阻放電,否則會(huì)發(fā)生邏輯錯(cuò)誤。

三、上拉電阻和下拉電阻的設(shè)置

當(dāng)我們選擇上拉和下拉電阻時(shí),應(yīng)考慮開(kāi)關(guān)管的特性和下拉電路的輸入特性,可以從以下幾個(gè)方面來(lái)說(shuō)明:

● 驅(qū)動(dòng)能力和功耗

以上拉電阻為例,一般來(lái)說(shuō),如果上拉電阻越小,驅(qū)動(dòng)能力就會(huì)更強(qiáng),功耗也會(huì)更大。這應(yīng)該是

● 驅(qū)動(dòng)低電平電路需求

同樣,以上拉電阻為例。當(dāng)高電平輸出且開(kāi)關(guān)關(guān)閉時(shí),上拉電阻應(yīng)能夠?yàn)橄虏侩娐诽峁┳銐虻碾娏鳌?/p>

● 高低電平

不同電路中高電平和低電平的閾值電平不同,應(yīng)適當(dāng)設(shè)置電阻,以確保可以輸出正確的電平。以上拉電阻為例,當(dāng)輸出為低電平且開(kāi)關(guān)導(dǎo)通時(shí),上拉電阻和開(kāi)關(guān)管的導(dǎo)通電阻應(yīng)低于零電平。

● 頻率特性

對(duì)于上拉電阻,上拉電阻與開(kāi)關(guān)管漏源電極之間的電容以及較低電平電路之間的輸入電容很容易造成RC延遲。阻力越大,延誤越大。

IV 上拉電阻和下拉電阻的原理分析

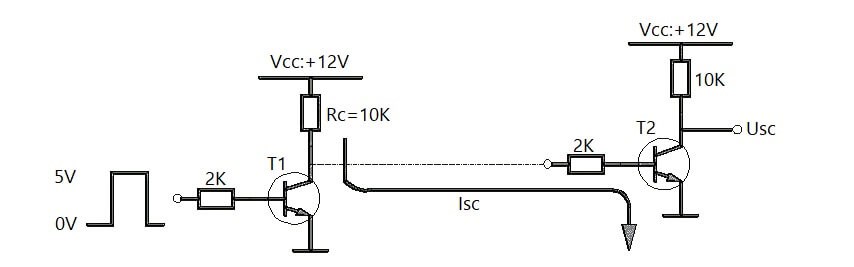

在電路圖-1中,假設(shè)晶體管T1在有電壓輸入時(shí)處于飽和狀態(tài)。

電路圖-1

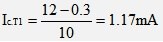

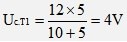

0-5V的脈沖電壓輸入到T1的基極。當(dāng)輸入電壓為5V時(shí),設(shè)置T1 Ube = 0.7V,因此 T1的基極電流:

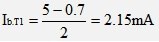

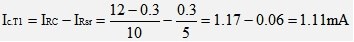

把T2的基極電流放在一邊,因?yàn)門(mén)1是飽和的,那么Uce = 0.3V,所以:

電路圖-2

現(xiàn)在我們來(lái)看電路圖-2 因?yàn)門(mén)2有輸入電阻,我們把它和基極電阻結(jié)合起來(lái)變成5K,也就是圖中的Rrsr。首先,使T1的輸入電壓為0V,T1將被切斷,其集電極應(yīng)輸出高電平。但實(shí)際集電極電壓是

既不高也不低。如果輸入電壓略高于0V,T1可能會(huì)進(jìn)入放大器區(qū)域,這將大大增加晶體管的功耗,并且集電極電壓將不穩(wěn)定。

當(dāng)T1管飽和時(shí),從邏輯上講,其集電極電壓為0.3V,這是一個(gè)低電平。收集器的節(jié)點(diǎn)-電流關(guān)系為:

那是:

無(wú)論是使用T1晶體管還是電路中的任何其他組件,都可以滿(mǎn)足這一點(diǎn)。因此,當(dāng)增加落后電平系統(tǒng)時(shí),會(huì)影響前一級(jí)的截止電壓,使晶體管的集電極電壓從高電平下降到既不高也不低的狀態(tài)。

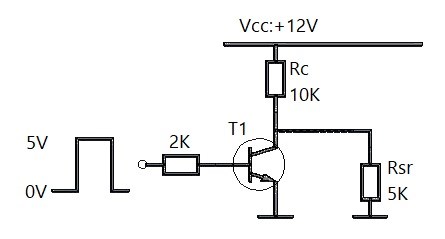

電路圖-3

在這種情況下,可以將上拉電阻連接到后電路的輸入端,如 電路圖-3中的R。該電阻的一端連接到電源Vcc,另一端連接到輸入端子。

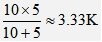

假設(shè)Rs = 5K,電阻10K和5K的并聯(lián)值為:

,

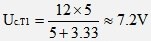

所以T1集電極的截止電壓為:

,

這比計(jì)算的最后一個(gè)值高得多。

因此,上拉電阻用于增加輸入級(jí)的高電平輸入電壓。

需要注意的是,當(dāng)T1管飽和時(shí),上拉電阻產(chǎn)生的電流會(huì)流入集電極。因此,上拉電阻是T1的吸電流負(fù)載。當(dāng)我們選擇上拉電阻的特定電阻時(shí),應(yīng)考慮前一階段的加熱功耗。

并且通過(guò)用相同的方法分析,我們可以看到下拉電阻是前一級(jí)的電流負(fù)載,對(duì)前一級(jí)晶體管的關(guān)斷狀態(tài)有影響。

V 上拉和下拉電阻電路

1. 上拉 R電鉆器 C軸

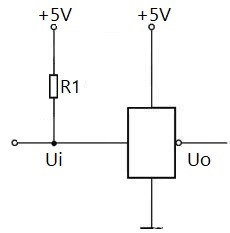

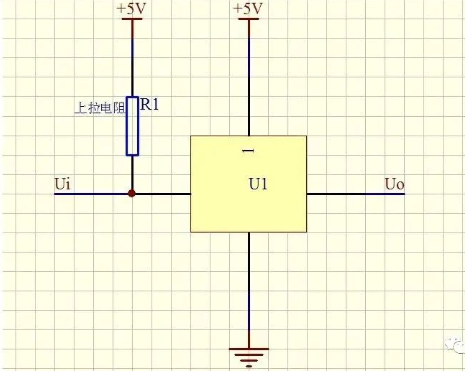

上拉電阻電路如圖所示,它是數(shù)字電路中的逆變器。當(dāng)沒(méi)有低電平注入逆變器的輸入端UI時(shí),上拉電阻R1可以使輸入端穩(wěn)定在高電平,防止導(dǎo)致逆變器故障的低電平干擾。

如果沒(méi)有上拉電阻,逆變器的輸入端被掛起,因此外部低電平干擾很容易進(jìn)入逆變器,從而導(dǎo)致逆變器向輸出高電平的方向翻轉(zhuǎn)。

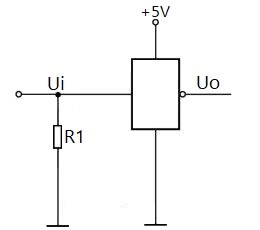

2. 下拉式 R 電擊器 C電擊器

該圖顯示了數(shù)字電路中的逆變器。輸入端Ui 通過(guò)下拉電阻R1接地,因此當(dāng)沒(méi)有高電平輸入時(shí),輸入端可以穩(wěn)定在低電平,而不會(huì)產(chǎn)生導(dǎo)致逆變器故障的高電平干擾。

如果省略下拉電阻R1,則逆變器的輸入端懸空且處于高阻抗。結(jié)果,外部高電平干擾很容易從輸入端添加到逆變器中,使逆變器向輸出低電平方向翻轉(zhuǎn)。

-

電阻

+關(guān)注

關(guān)注

86文章

5519瀏覽量

172094 -

上拉電阻

+關(guān)注

關(guān)注

5文章

360瀏覽量

30626 -

下拉電阻

+關(guān)注

關(guān)注

4文章

147瀏覽量

20537

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

上拉電阻和下拉電阻作用、區(qū)別和應(yīng)用

什么是上拉電阻和下拉電阻_上拉電阻和下拉電阻的區(qū)別_上拉電阻的作用原理

如何選擇正確值的上拉電阻和下拉電阻?

上拉電阻與下拉電阻

上拉電阻和下拉電阻之間有什么區(qū)別

上拉電阻和下拉電阻之間有什么區(qū)別

評(píng)論