當(dāng)使用帶外部存儲(chǔ)器的達(dá)拉斯半導(dǎo)體高速微控制器時(shí),P0開(kāi)關(guān)產(chǎn)生的噪聲可能會(huì)耦合到ALE。通過(guò)仔細(xì)的電路板布局和對(duì)多路復(fù)用地址/數(shù)據(jù)總線上的感應(yīng)噪聲的充分理解,可以將這些問(wèn)題降至最低。本應(yīng)用筆記著眼于DS80C320高速微控制器訪問(wèn)外部存儲(chǔ)器時(shí)的情況。

概述

8051 架構(gòu)允許通過(guò)使用端口 0 和端口 2 作為外部存儲(chǔ)器接口來(lái)訪問(wèn)外部程序和數(shù)據(jù)。8051 架構(gòu)在端口 0 上多路復(fù)用地址的數(shù)據(jù)和 LSB,需要 74373 鎖存器進(jìn)行多路復(fù)用。這意味著端口 0 將直接連接到至少兩個(gè)設(shè)備。如果使用外部數(shù)據(jù)SRAM或存儲(chǔ)器映射外設(shè),則總線上可能會(huì)放置更多器件。

由于端口 0 必須在地址和數(shù)據(jù)之間快速切換,因此需要強(qiáng)大的電流驅(qū)動(dòng)特性。遺憾的是,快速切換端口0的所有引腳的高瞬時(shí)電流要求可能會(huì)在ALE信號(hào)上產(chǎn)生噪聲。在某些情況下,這種噪聲會(huì)導(dǎo)致外部硬件鎖存不正確的地址,從而干擾程序和數(shù)據(jù)訪問(wèn)。這種情況比較少見(jiàn),大多數(shù)設(shè)計(jì)師都不會(huì)遇到。這個(gè)問(wèn)題的嚴(yán)重程度與與系統(tǒng)和軟件相關(guān)的幾個(gè)問(wèn)題直接相關(guān)。不通過(guò)端口 0 和端口 2 訪問(wèn)外部存儲(chǔ)器的設(shè)備不會(huì)遇到此問(wèn)題。

本應(yīng)用筆記將討論系統(tǒng)設(shè)計(jì)人員如何降低端口0開(kāi)關(guān)對(duì)器件工作的影響。它適用于任何通過(guò)端口 8051 和端口 0 訪問(wèn)外部存儲(chǔ)器的無(wú) ROM2 微控制器,包括 DS80C310 和 DS80C320。它也適用于任何具有內(nèi)部程序存儲(chǔ)器的微控制器,該微控制器訪問(wèn)外部存儲(chǔ)器。

ALE 噪聲生成

在某些系統(tǒng)條件下,ALE上感應(yīng)的噪聲會(huì)導(dǎo)致使用多路復(fù)用地址/數(shù)據(jù)總線時(shí)鎖存不正確的LSB地址。如圖1所示,噪聲是由處理器在MOVX寫(xiě)入期間停止驅(qū)動(dòng)內(nèi)存地址并開(kāi)始驅(qū)動(dòng)數(shù)據(jù)時(shí)端口0的高速切換產(chǎn)生的。在適當(dāng)?shù)臈l件下,噪聲脈沖可以上升到V以上IHTTL、LS、FS 和 HCT 邏輯的輸入閾值。在這種情況下,74373鎖存器可能會(huì)被錯(cuò)誤觸發(fā),鎖定不正確的地址并干擾MOVX寫(xiě)入的LSB地址。

圖1.數(shù)據(jù)存儲(chǔ)器寫(xiě)入(理想時(shí)序)。

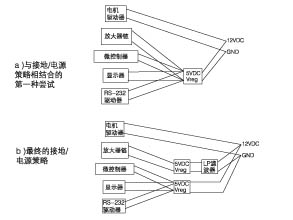

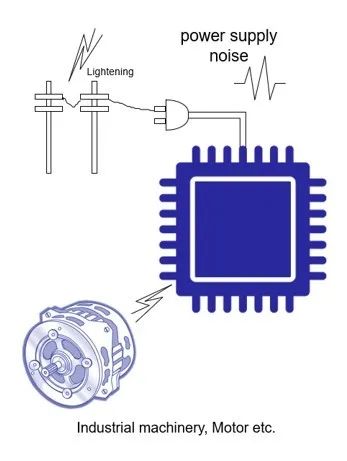

圖2顯示了如何產(chǎn)生噪聲脈沖的系統(tǒng)圖。當(dāng)處理器驅(qū)動(dòng)端口 0 引腳時(shí),會(huì)產(chǎn)生噪聲脈沖,該引腳具有高地址(參見(jiàn)圖 1 中的“A”),后跟數(shù)據(jù)為低電平(參見(jiàn)圖 1 中的“D”)。器件必須在每個(gè)引腳上吸收相對(duì)較大的電流(IB) 將線從高到低狀態(tài)。很明顯,從高電平到低電平變化的引腳越多,噪聲就越大。最壞的情況是在 MOVX 寫(xiě)入指令期間,LSB 地址為 FF(十六進(jìn)制),數(shù)據(jù)字節(jié)為 00(十六進(jìn)制)。由于所有八個(gè)端口引腳同時(shí)切換,因此最大電流將被吸入微控制器。處理器內(nèi)部和系統(tǒng)中的電感和電阻組合導(dǎo)致處理器內(nèi)部接地高于系統(tǒng)地。這反過(guò)來(lái)又會(huì)引發(fā) ALE 上看到的噪音。MOVX讀取的情況不涉及處理器的電流吸收,并且不會(huì)在ALE信號(hào)上產(chǎn)生明顯的噪聲。與噪聲大小有直接關(guān)系的系統(tǒng)元素包括:

端口 0 總線電容。

系統(tǒng)接地電感 (L2) 和電阻 (R2)。

系統(tǒng)電源電壓(V抄送).

圖2.ALE 噪聲源。

噪

有幾種技術(shù)可用于最小化端口0切換對(duì)ALE噪聲的影響。降低總線電容可降低放電所需的能量,從而降低峰值電流并降低噪聲脈沖中的峰值電壓。降低外部接地電阻和電感還可以通過(guò)降低電阻和感性壓降來(lái)降低噪聲水平。

電源電壓也與噪聲脈沖的電壓電平成正比。維護(hù) V抄送在推薦的規(guī)格范圍內(nèi)將限制噪聲電壓水平。

如圖0所示,添加與端口3串聯(lián)的低阻抗電阻,通過(guò)限制吸入微控制器的峰值電流來(lái)降低噪聲水平。必須注意驗(yàn)證這些電阻在處理器寫(xiě)入外部存儲(chǔ)器時(shí)不會(huì)對(duì)存儲(chǔ)器的壓擺率或最終輸入電壓電平產(chǎn)生不利影響。通常可以使用50Ω至150Ω范圍內(nèi)的值,而不會(huì)干擾寫(xiě)入周期時(shí)間。串聯(lián)電阻的實(shí)際值應(yīng)在終端系統(tǒng)中進(jìn)行驗(yàn)證。

圖3.噪。

在ALE信號(hào)線上使用電容也會(huì)顯著降低噪聲脈沖。同樣,必須在系統(tǒng)中驗(yàn)證值,注意不要將ALE信號(hào)的壓擺率降低到內(nèi)存訪問(wèn)不再有效的程度。通常,10至30pF之間的電容足以降低噪聲水平,而不會(huì)影響系統(tǒng)正常運(yùn)行。

輸入閾值

消除地址鎖存相關(guān)噪聲的最簡(jiǎn)單、最可靠的方法是選擇具有高輸入閾值的邏輯系列。標(biāo)準(zhǔn) TTL、LS、FS 和 HCT 邏輯器件具有 VIH閾值約為 2.0 伏。另一方面,HC(高速CMOS)或AC(高級(jí)CMOS)邏輯具有VIH在 3 伏的電源電壓下約為 5.5 伏。HC 或 AC CMOS 邏輯的較高閾值電平可將抗擾度提高約 1.5 V。這通常是防止 ALE 意外閉鎖所需的全部?jī)?nèi)容。

使用CMOS邏輯的一個(gè)缺點(diǎn)是它比其他邏輯系列慢。通過(guò)CMOS邏輯的傳播延遲通常在HC的18 ns和AC的10 ns范圍內(nèi),而使用2 V電源時(shí),F(xiàn)S邏輯的傳播延遲為4至5 ns。對(duì)于速度較慢的微控制器,如DS5000、DS5001和DS5002,由于時(shí)鐘速率較慢,傳播延遲通常不是問(wèn)題。速度較快的微控制器(如高速微控制器)應(yīng)仔細(xì)考慮較慢邏輯的時(shí)序影響。無(wú)論如何,應(yīng)在最終應(yīng)用中進(jìn)行測(cè)試,以使用較慢的CMOS邏輯驗(yàn)證效果。

審核編輯:郭婷

-

微控制器

+關(guān)注

關(guān)注

48文章

7646瀏覽量

151876 -

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

235914 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164188

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ST微控制器EMC設(shè)計(jì)指南

微控制器/模擬應(yīng)用中電源、接地和噪聲的管理

微控制器/模擬應(yīng)用中電源、接地和噪聲的管理

微控制器/模擬應(yīng)用中電源、接地和噪聲的管理

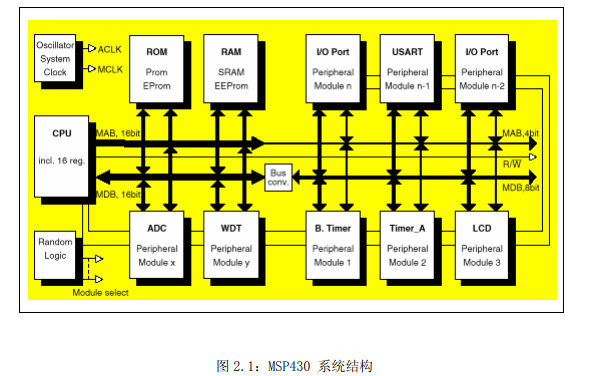

MSP430系列混合信號(hào)微控制器的中文用戶指南資料免費(fèi)下載

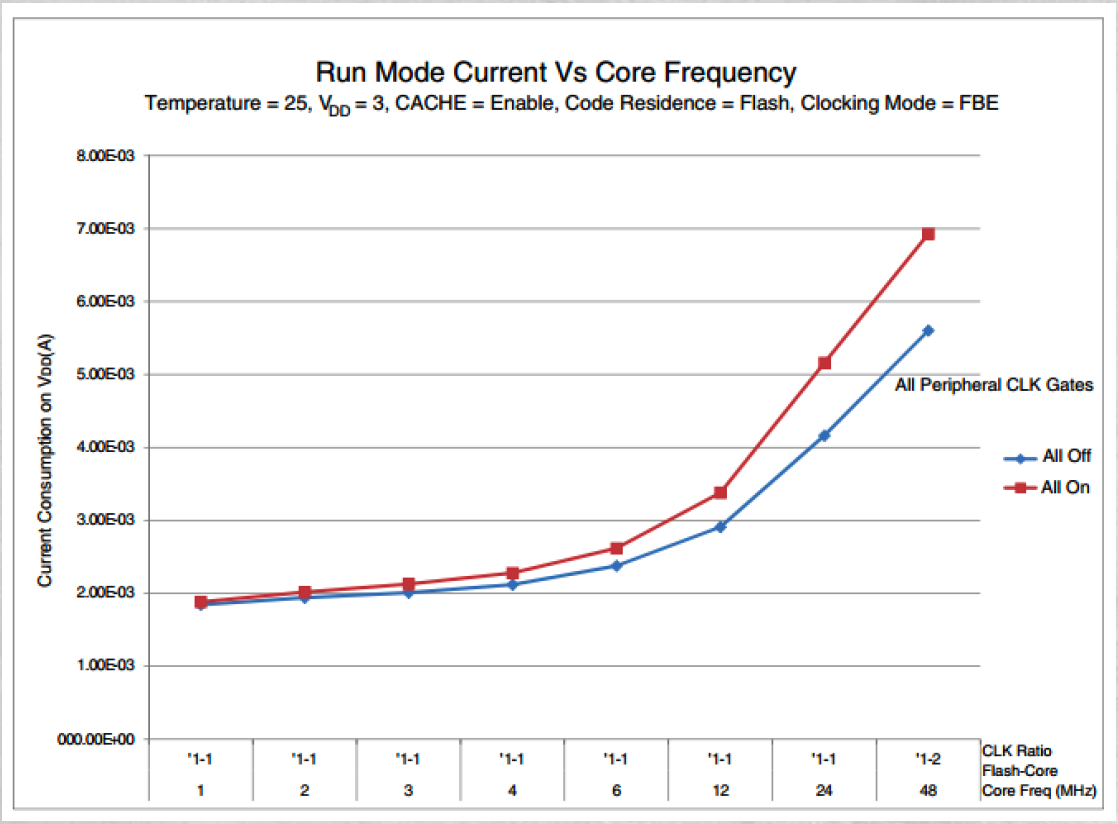

五種降低微控制器能耗的技術(shù)

如何降低微控制器系統(tǒng)中的噪聲影響(3)

降低ALE信號(hào)噪聲的微控制器設(shè)計(jì)指南

降低ALE信號(hào)噪聲的微控制器設(shè)計(jì)指南

評(píng)論