當今的許多儀器儀表和過程控制應用使用模數轉換器(ADC)轉換傳感器的模擬輸出進行處理和/或存儲。對于電壓輸入ADC,存在三種不同的輸入結構類型:單端、偽差分和全差分。本教程解釋了輸入類型之間的差異、優勢和權衡。

當今的許多電子儀器都依賴于微控制器或數字信號處理器(DSP)來處理現實世界的模擬信號。傳感器將溫度或壓力等自然參數轉換為電壓或電流。模數轉換器(ADC或A/D轉換器)將信號轉換為數字形式。

對于電壓輸入ADC,存在三種不同的輸入結構類型:單端、偽差分和全差分。

最簡單的解決方案是選擇與傳感器輸出相匹配的ADC輸入結構。但是,應考慮每種結構的權衡。此外,如果在傳感器和ADC之間使用信號調理電路,該電路會影響ADC輸入結構的選擇。一些ADC是可配置的,允許在單端或偽差分輸入結構(MAX186、MAX147)之間進行選擇,而其他ADC允許在單端或全差分(MAX1298、MAX1286)之間進行選擇。

全差分輸入

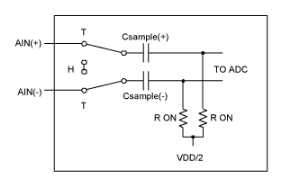

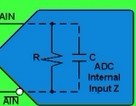

為了獲得最大的噪聲抑制,請使用全差分輸入。圖1所示為全差分ADC T/H輸入結構示例。在跟蹤模式下,Csample(+) 充電至 [AIN(+) D VDD/2] 和 Csample(-) 電荷為 [AIN(-) D VDD/2].當T/H切換到保持模式時,Csample(+)和Csample(-)串聯在一起,因此提供給ADC的電壓樣本是AIN(+)和AIN(-)的差值。差分架構與T/H中可接受的輸入帶寬相結合,是實現良好動態共模抑制的關鍵因素。

圖1.全差分 T/H 載物臺。

在嘈雜的環境中,耦合噪聲可能導致差分輸入超過ADC允許的輸入電壓范圍。為獲得最佳性能,請減小輸入信號范圍,以確保不超過ADC輸入范圍。

差分信號的另一個關鍵優勢是動態范圍增加。隨著電源降至3.3V或更低,設計工程師正在尋找實現更大輸入動態范圍的方法。理論上,給定單端和全差分輸入的相同電壓范圍,全差分輸入的動態范圍將是其兩倍(圖 2)。這是因為兩個差分輸入可能180°異相,如圖3所示。

圖2.全差分模式 - AIN(+) 和 AIN(-) - 180° 異相。

圖3.全差分模式與單端模式使ADC動態范圍翻倍。

另一種思考方式是與信噪比(SNR)有關。SNR根據ADC的滿量程輸入電平和最小可檢測信號來定義:

最小可檢測信號通常受本底噪聲的限制。由于全差分輸入具有滿量程輸入電壓電平的2倍,并且具有出色的直流和交流共模抑制(表現為噪聲),因此SNR增加。

浮動差分輸入

理想情況下,共模電壓超過GND和V。DD可以存在于差分系統中,前提是差分電壓不超過ADC輸入范圍。實際上,只有當傳感器和ADC隔離時,才能實現這一點。在圖4的示例中,AIN(+)和AIN(-)處的電壓落在ADC規定的輸入范圍內,但傳感器輸出電壓上的大共模電壓迫使ADC輸入超過最大輸入電壓規格。

圖4.高共模電壓。

圖5顯示了相同的系統,但使用具有電氣隔離接地的獨立電源。R偏見將輸入偏置為 V裁判/2,以盡量減少泄漏電流引起的漂移。只要接地之間存在隔離,ADC就只能看到AIN(+)和AIN(-)之間的差分電壓,因此傳感器(或ADC)被稱為“浮動”。(注意:為確保電流隔離,必須考慮傳感器接地和系統接地之間的所有泄漏路徑。電池供電系統固有地提供隔離,前提是其機箱與其內部ADC系統接地隔離)。

圖5.高共模電壓,帶獨立系統電源。

偽差分輸入

偽差分輸入類似于全差分輸入,因為它們將信號接地與ADC接地分開,允許消除直流共模電壓(與單端輸入不同)。然而,與全差分輸入不同,它們對動態共模噪聲的影響很小。

在圖6中,采樣僅發生在輸入AIN(+)信號上。不對共模信號 AIN(-) 進行采樣。在“TRACK”模式下,采樣電容通過串聯電阻R充電上.在“保持”模式下,采樣電容連接到AIN(-),反相輸入信號提供給ADC進行轉換。由于采樣僅發生在 AIN(+) 輸入上,因此在轉換期間 AIN(-) 必須保持在 ±0.1LSB 以內以獲得最佳性能。

圖6.偽差分 T/H 階段。

實現偽差分輸入的另一種方法按順序對AIN(+)和AIN(-)進行采樣,并提供兩個電壓的差值作為轉換結果。

對于動態信號,AIN(+) 和 AIN(-) 的相位在采樣期間不匹配,從而導致失真。選擇具有全差分輸入的ADC,用于動態時變信號。

偽差分輸入的典型應用是測量偏置到任意直流電平的傳感器。有些器件(如MAX146)具有COM引腳,允許單端輸入以共模電壓為基準,使其成為偽差分。所有輸入通道均以COM電壓為參考。

圖7顯示了在惠斯通電橋應用中連接的熱敏電阻。在此示例中,AIN(+) 和 AIN(-) 都不為零。ADC 的輸出代碼是差分電壓 AIN(+) - AIN(-) 的函數。偽差分輸入抵消了直流共模電壓。為確保AIN(-)穩定在±0.1LSB以內,請使用一個0.1μF電容將AIN(-)旁路至模擬地。

圖7.惠斯通電橋應用。

單端輸入

單端輸入通常足以滿足大多數應用的需求。在單端應用中,所有信號都以ADC上的公共接地為基準。每個通道使用單個輸入引腳。模擬接地引腳在多通道系統的所有輸入之間共享。信號路徑中的直流偏移和/或噪聲會減小輸入信號的動態范圍。如果信號源和ADC彼此靠近(即在同一電路板上,以便信號走線盡可能短),則單端輸入是理想的選擇。單端輸入更容易受到耦合噪聲和直流失調的影響。然而,信號調理電路可以減少這些影響。

圖8顯示了單端ADC的采樣保持(T/H)輸入的簡化示例。采樣電容在“TRACK”模式下通過串聯電阻切換到輸入引腳。當T/H進入“保持”模式(在實際轉換過程中)時,開關斷開,ADC將采樣電容兩端的電壓轉換為數字代碼。

圖8.單端 T/H 載物臺。

共模電壓和共模抑制比

共模電壓是指公共電壓(即兩個差分輸入端的幅度和相位相同(圖 9)。共模抑制比(CMRR)通常指定用于全差分輸入,描述了ADC抑制共模(通常為DC)電壓的能力。ADC輸入端出現的直流共模電壓與直流輸入失調具有相同的效果。通常,傳感器信號和地線在物理上非常接近,并且會耦合到共模噪聲中。共模噪聲的最大來源通常是來自電源線的50/60Hz噪聲。電源紋波、EMF、RF或高頻開關噪聲也可能是共模噪聲的來源。

圖9.共模電壓。

共模抑制比(CMRR)通常定義為差分電壓增益與共模電壓增益之比:

其中:

ADIFF = 差分電壓增益

ACM = 共模電壓增益

對于ADC,差分電壓增益(A差異) 定義為 Δ Output_Code/Δ Differential_Voltage共模電壓增益定義為 Δ Output_Code/Δ Common_Mode_Voltage。對于全差分輸入,輸出代碼相對于共模電壓的變化很小;因此,CMRR會很大,并且通常以對數刻度表示。

需要注意的是,CMRR依賴于頻率相關參數。隨著共模電壓頻率的增加,AIN(+)和AIN(-)之間實現最佳共模抑制的相位匹配變得更加難以維持。因此,共模抑制在高頻下效果較差。

總結

將傳感器與ADC接口需要將傳感器/信號調理輸出與ADC輸入相匹配。電壓輸出傳感器提供單端或差分輸出。對于單端信號,所有輸入均以系統地為基準。差分信號提供正信號和負信號,正輸出 (AIN+) 以負輸出 (AIN-) 為參考。

三種常見的ADC輸入結構適用于單端或差分輸出傳感器:單端、偽差分或全差分。最簡單的方法是在測量單端信號時使用單端ADC。如果使用差分ADC測量單端信號,只需將ADC AIN(-)引腳連接到模擬地即可。這允許使用多通道差分輸入ADC測量單端和差分信號。

差分輸入可以通過測量傳感器正負端之間的電壓差來提供比單端輸入的性能改進。這提供了共模抑制。選擇用于直流共模電壓抑制的偽差分ADC。對于需要激勵的傳感器,使用偽差分ADC可以將偏置電壓歸零,并允許傳感器接地與模擬接地不同。偽差分輸入不提供交流共模抑制。對于動態共模抑制,請選擇全差分ADC。全差分輸入通過抑制直流和動態共模電壓提供最佳性能。最終選擇使用哪種輸入結構將取決于傳感器、信號調理電路、應用和精度要求。

審核編輯:郭婷

-

dsp

+關注

關注

554文章

8030瀏覽量

349320 -

轉換器

+關注

關注

27文章

8724瀏覽量

147416 -

adc

+關注

關注

98文章

6512瀏覽量

545017

發布評論請先 登錄

相關推薦

STM32 ADC的工作原理及其庫函數配置概述

電流積分模數轉換器(ADC),什么是電流積分模數轉換器(AD

如何使用8051單片機和閃存的精密模數轉換器(ADC)的詳細概述

ADC轉換器輸入概述

ADC轉換器輸入概述

評論