前面我們分享了中斷及ARM體系中對中斷的處理、GIC-600以及redistributor的相關知識,本篇將介紹ARM存儲一致性模型的相關知識。

按照慣例,先講基礎原理,再說ARM的相關部分。

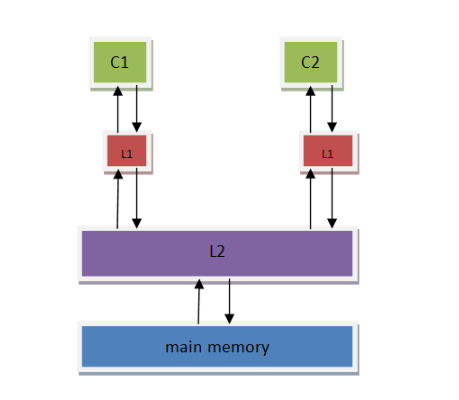

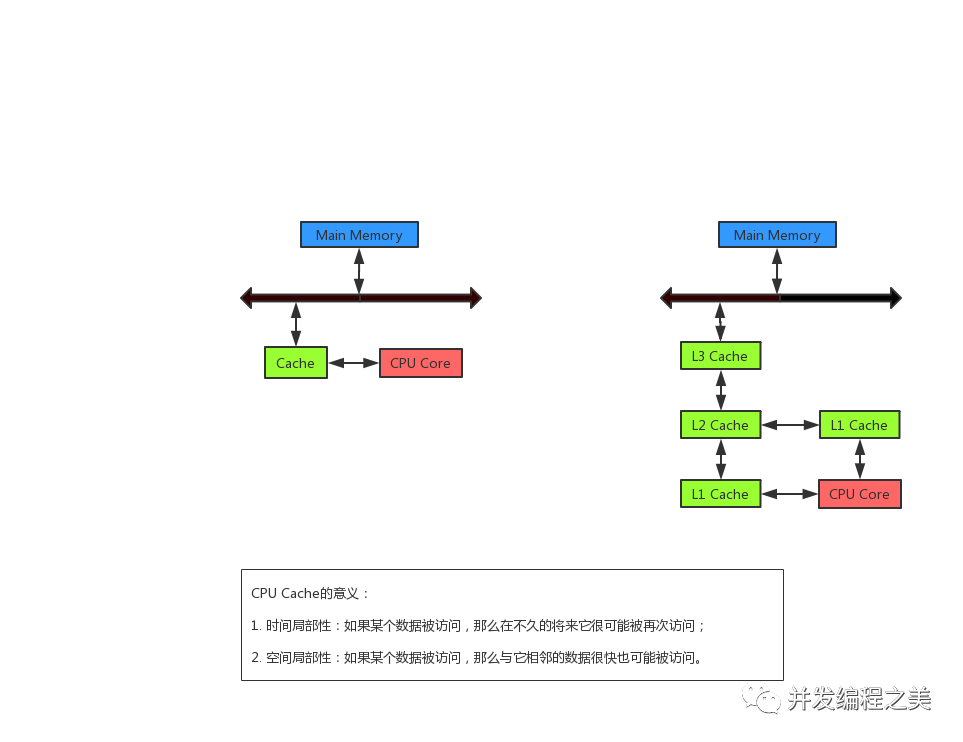

今天要說的這個是存儲一致性(memory consistency),不要跟前面講過緩存一致性(cache coherence)混淆了。緩存一致性協議解決的是對單個存儲器地址的訪問之間如何排序的問題,而對于不同地址的訪問并不是緩存一致性協議所要考慮的問題。存儲一致性問題在任何具有或不具有高速緩存的系統中都存在,雖然高速緩存的存在有可能進一步加劇存儲一致性問題。

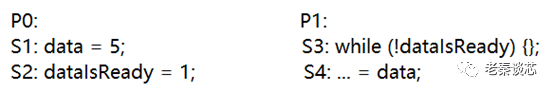

存儲器模型(memory model)又稱為存儲一致性模型。用于定義系統中對存儲器訪問需要遵守的原則,只要軟件和硬件都遵循該原則,就能保證多核程序能運行得到確切的結果。 對于程序員來說,通常直覺上會隱式地假定存儲器操作是按一定次序的。來看下面的例子,假定有兩個線程P0和P1。

在線程P0中,執行S1,賦值data為5;執行S2,賦值dataIsReady為1。在線程P1中,等待dataIsReady這個變量變為1,然后把data賦值給其它變量。在我們直觀看來,S1先于S2執行,通過dataIsReady來阻塞P1的S3執行,那么執行S4的時候,拿到的data一定是5。

實際上,未必是這樣,可能S2的結果早于S1傳播到P1,S4拿到的data就有可能是舊值,而不是5! 在我們的直觀感覺里,對于變量的寫操作會即時傳播,或者說是原子性的,即P0的寫操作必須以不能分割的步驟傳播到P1。我們把關于存儲器訪問次序的隱式期望表示為:來自一個處理器的存儲器訪問應該以程序的次序執行,并且每個訪問的執行必須是原子性的。

這樣一種期望被正式定義為順序一致性(SC)模型。順序一致性模型雖然能嚴格的解決存儲訪問次序問題,但是由于過于嚴厲,會產生巨大的性能開銷。因為當某一個寫入操作未執行完,其它的操作可能會全部暫停下來。所以現在大部分處理器都不會實現順序一致性,而是實現一些較為松弛的一致性模型。

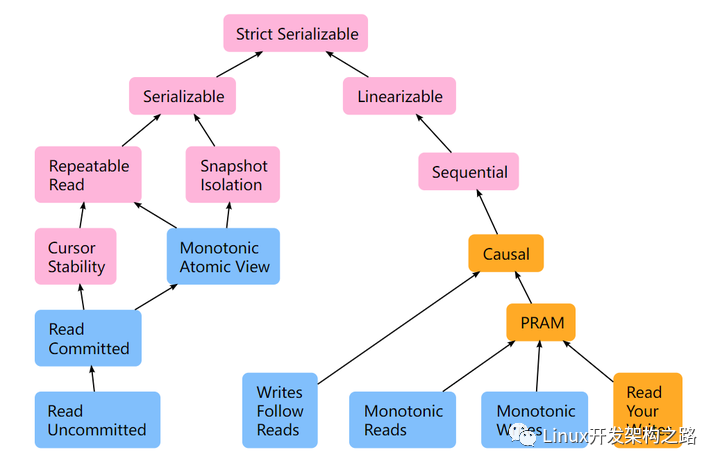

下面將根據從強到弱的限制程度排序,列舉幾種典型的存儲器模型:

1. 順序一致性模型(sequential consistency,SC)

也稱為強定序模型,從施加的限制來看,該模型下load/store是順序的訪問存儲器。每個處理器都按照程序順序來執行程序,即便訪問的是不同存儲器地址,也不能改變訪問順序。從全局看,每個存儲器寫操作都需要能被系統中所有的處理器同時觀測到,同一時刻只有一個處理器和存儲系統相連,因此對memory的訪問時原子化的,串行化的。順序一致性模型簡單直觀,但限制了CPU硬件和編譯器的優化,影響了整個系統的性能。

2. 完全存儲定序模型(Total Store Order,TSO)

由于處理器主頻和存儲器頻率相差較大,系統設計人員通常會在CPU中增加存儲緩沖區(store buffer),它的作用是為store指令提供緩沖,使得處理器不用等待存儲器的響應。但是由于存儲緩沖的存在,一些在store之后的load指令可能會越過該指令提前執行,那一個core的store-load操作通常會被其他core看成亂序執行了,變成load-store了。因此在在該模型下,訪存操作的四種組合store-store,store-load,load-store,load-load中,只有store-load存在亂序。store操作在store_buffer中順序執行。load同樣按順序執行,但可穿插到多個store執行過程中

3. 部分存儲定序模型(Part Store Order,PSO)

系統設計人員并不滿足TSO模型帶來的性能提升,于是繼續在TSO的基礎上放松訪問內存訪問限制,允許處理器以非FIFO來處理store buffer緩沖區的指令,處理器只保證地址相關指令在store buffer中以FIFO的形式進行處理,而其它的則可以亂序處理。

4. 處理器一致性模型(Processor Consistency,PC)

該模型比順序一致性弱。在SC中,要維持每一條load/store指令與后續load/store指令的次序。在處理器一致性模型中,則放松了較早的store指令和較晚的load指令之間的次序。當一條store指令還未被執行時,允許一條較晚的load指令像高速緩存發出請求甚至結束。這一點的重要性在于,store指令可以在寫緩沖區排隊并在稍晚執行,同時,load指令不需要等待較早的store指令結束就可以訪問高速緩存,所以降低了load指令的時延。

5. 弱序一致性模型(Weak Order Consistency,WO)

該模型的主要思想是把同步操作和普通訪存操作區分開來,兩個同步操作之間的訪存操作的順序不受影響,依然遵循指令程序順序。WO模型利用了兩個假設:程序是適當同步的;程序員正確的向硬件表示哪些load和store是起到同步訪問作用的。

程序員必須用硬件可識別的同步操作把對可寫共享單元的訪問保護起來,以保證多個處理器對該共享單元的訪問是互斥的。該模型增加了程序員的負擔,但能有效提高性能。目前,很多的商業化處理器實現的就是WO,比如ARM。

6. 釋放一致性模型(Release Consistency,RC)

該模型是對弱一致性模型的改進,它把同步操作進一步分成獲取操作(acquire)和釋放操作(release)。acquire用于獲取對某些共享存儲單元的獨占性訪問權;release用于釋放該訪問權。執行的順序為:acquire-> load/store ->release。

與WO類似,RC允許編譯器自由改變load指令和store指令的次序,但是不允許它們越過一個獲取同步向前移動,也不允許它們越過一個釋放同步向后移動。與WO不同的是,單靠指令的操作碼不容易表示同步訪問。 通常來說,存儲一致性模型對訪存事件次序施加的限制越弱,越有利于提高性能,但增加了編程難度。

且限制越強的存儲器模型程序可以在限制較弱的存儲器模型上運行,很少會導致錯誤。 關于存儲器一致性模型,有很多的學術文章和書籍,我所了解的也就是一點皮毛。其實,今天講的這些,都是基礎知識。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19293瀏覽量

229934 -

ARM

+關注

關注

134文章

9098瀏覽量

367684 -

存儲器

+關注

關注

38文章

7493瀏覽量

163873 -

fifo

+關注

關注

3文章

388瀏覽量

43692 -

編譯器

+關注

關注

1文章

1634瀏覽量

49139

原文標題:技術分享 | ARM系列 - - 存儲模型(一)

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ARM系列 - - 存儲模型(一)

順序一致性和TSO一致性分別是什么?SC和TSO到底哪個好?

一致性規劃研究

CMP中Cache一致性協議的驗證

TTCN在TD-SCDMA終端RRM一致性測試系統中的應用

加速器一致性接口

Cache一致性協議優化研究

優化模型的乘性偏好關系一致性改進

自主駕駛系統將使用緩存一致性互連IP和非一致性互連IP

DDR一致性測試的操作步驟

深入理解數據備份的關鍵原則:應用一致性與崩潰一致性的區別

介紹ARM存儲一致性模型的相關知識

介紹ARM存儲一致性模型的相關知識

評論