緒論

使用Vivado Block Design設(shè)計(jì)解決了項(xiàng)目繼承性問(wèn)題,但是還有個(gè)問(wèn)題,不知道大家有沒(méi)有遇到,就是新設(shè)計(jì)的自定義 RTL 文件無(wú)法快速的添加到Block Design中,一種方式是通過(guò)自定義IP,但是一旦設(shè)計(jì)的文件有問(wèn)題就需要重新修改,同時(shí)需要控制接口時(shí)候還需要在AXI總線模板基礎(chǔ)上進(jìn)行修改,再同時(shí)繁瑣的步驟也讓人“望而卻步”。下面介紹一種簡(jiǎn)單的方式。

我目前使用的是 Vivado 2019.1、2020.2,但據(jù)我所知,此功能幾乎適用于 Vivado 的所有版本(如果不正確,請(qǐng)隨時(shí)在后臺(tái)更正)。

創(chuàng)建 Vivado 項(xiàng)目

為了開(kāi)始這個(gè)例子,我創(chuàng)建了一個(gè)基于 Zynq 的新 Vivado 項(xiàng)目(這只是我的例子,但這個(gè)項(xiàng)目的內(nèi)容并不特定于任何特定的 FPGA 開(kāi)發(fā)板),同時(shí)這個(gè)項(xiàng)目中包括一個(gè)通過(guò)AXI-Lite控制的自定義RTL。

添加設(shè)計(jì)文件并編寫(xiě)自定義 RTL

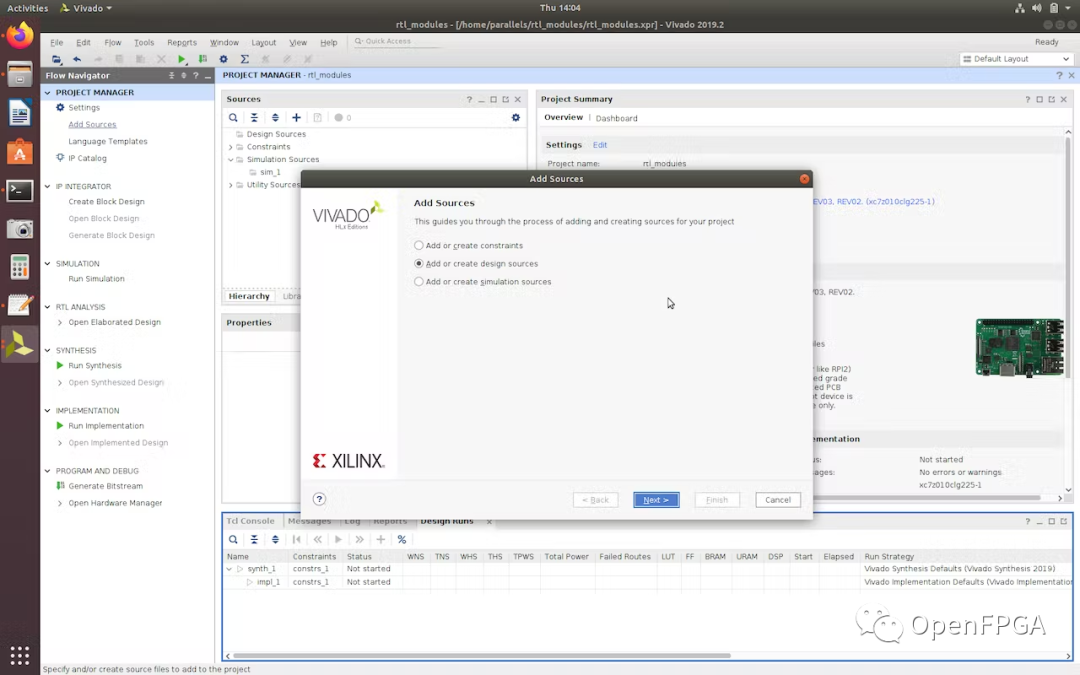

不用于仿真目的的自定義 RTL(即測(cè)試文件)都被視為 Vivado 中的設(shè)計(jì)源。使用 Flow Navigator 中的Add Sources選項(xiàng)并選擇Add or create design sources ,然后單擊 Next。

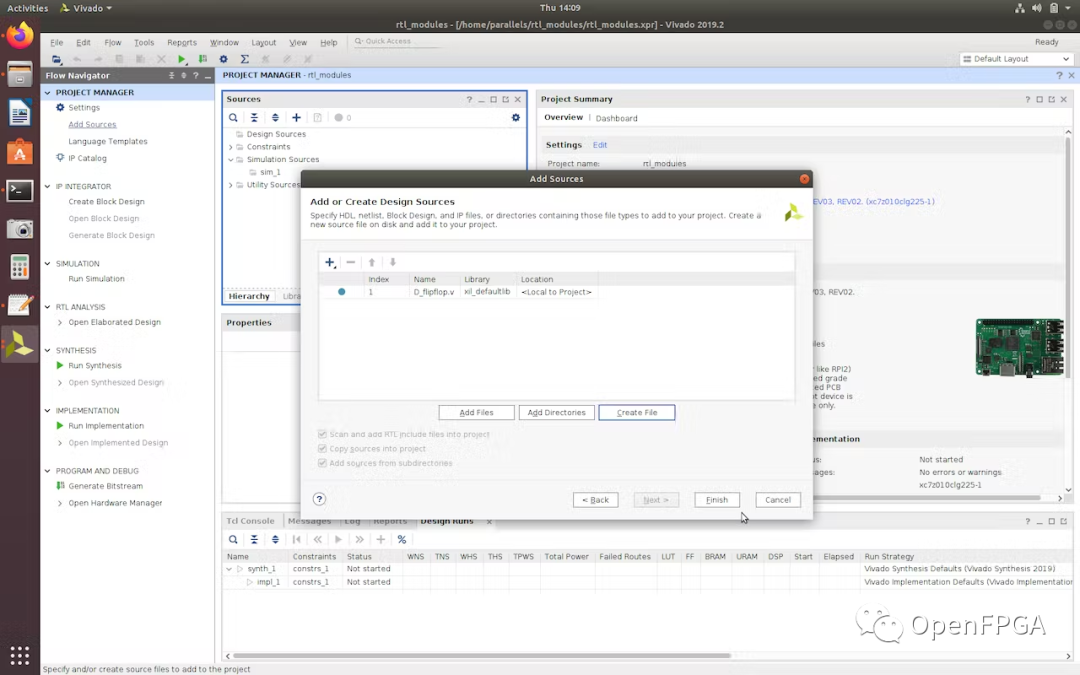

我們創(chuàng)建一個(gè)名為D_flipflop的新文件并添加了以下邏輯:

moduleD_flipflop( inputclk, inputreset, inputd_in, outputregq_out ); always@(posedgeclk) begin if(reset==1'b1) begin q_out<=?1'b0; ????????????????end ????????????else? ????????????????begin ????????????????????q_out?<=?d_in; ????????????????end ????????end endmodule

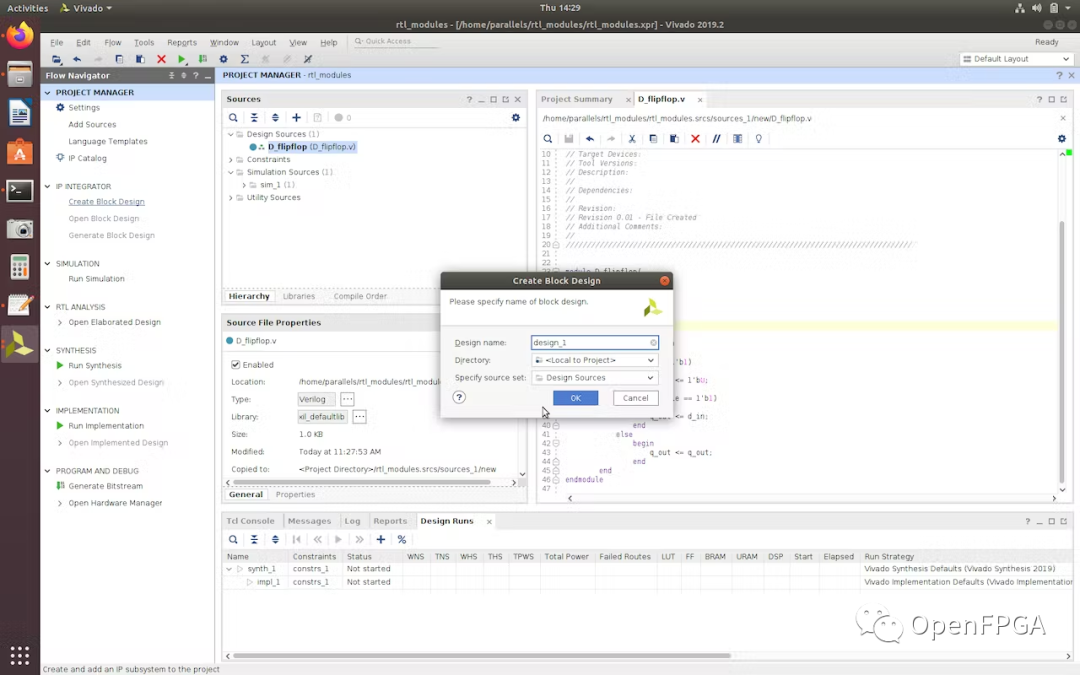

創(chuàng)建Block Design

使用 Flow Navigator 窗口中的Create Block Design選項(xiàng),將新的Block Design添加到項(xiàng)目中。

將 Zynq 處理系統(tǒng) IP 塊添加到設(shè)計(jì)中,并運(yùn)行自動(dòng)設(shè)置或者自動(dòng)連線。

將 RTL 模塊添加到Block Design

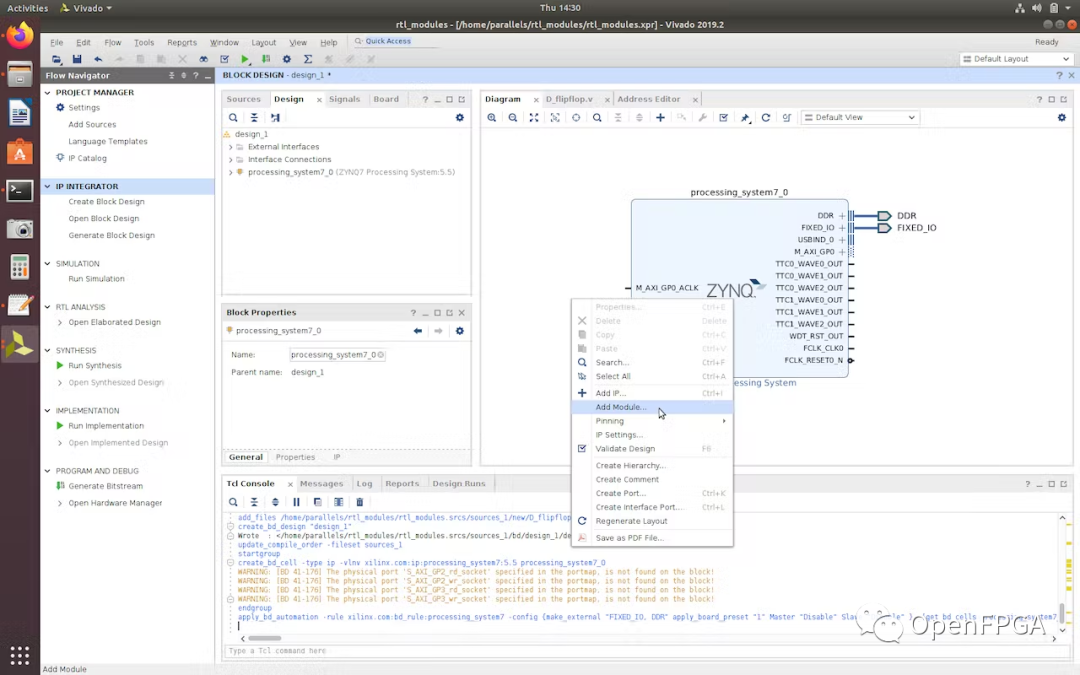

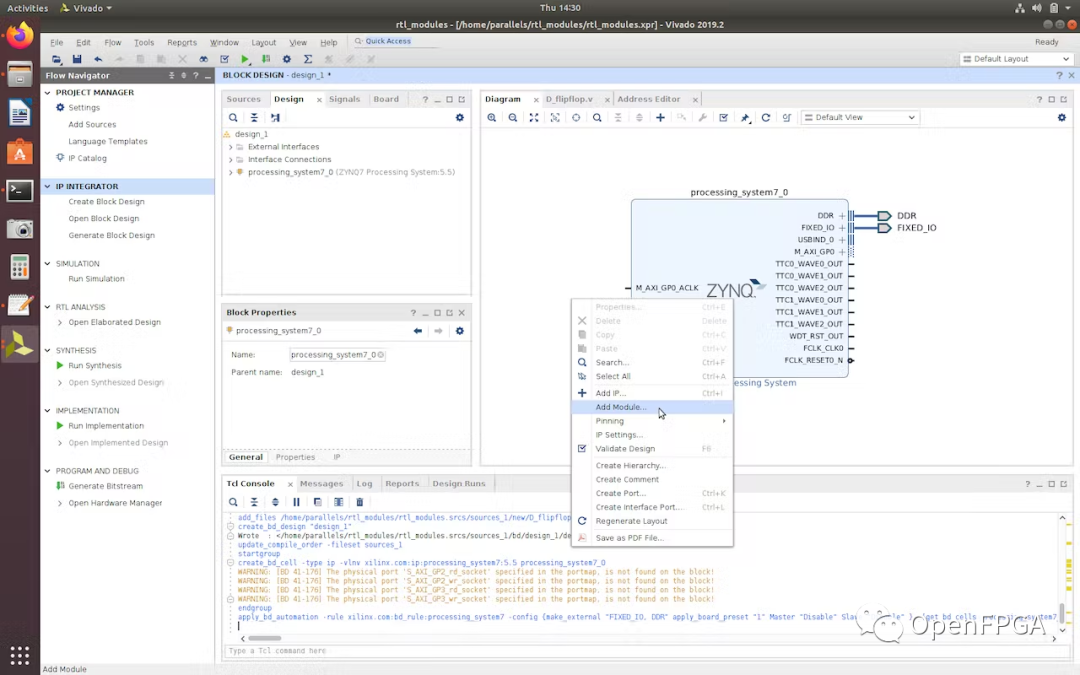

要添加我們?cè)谏弦徊街袆?chuàng)建的 D 觸發(fā)器的 RTL 模塊,右鍵單擊 Diagram 窗口空白處的任意位置,然后選擇Add Module...選項(xiàng)。

Vivado 將自動(dòng)顯示它在當(dāng)前項(xiàng)目中找到的所有有效 RTL 模塊。由于寫(xiě)入或?qū)氲疆?dāng)前項(xiàng)目中的模塊是我們剛剛設(shè)計(jì)的 D 觸發(fā)器,因此它是本例中的唯一選項(xiàng)。

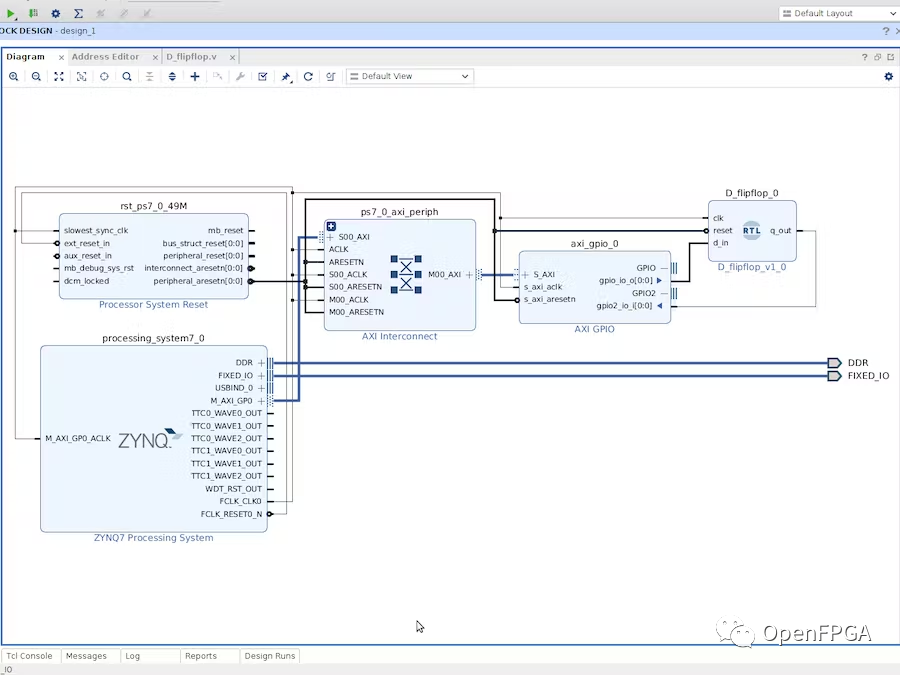

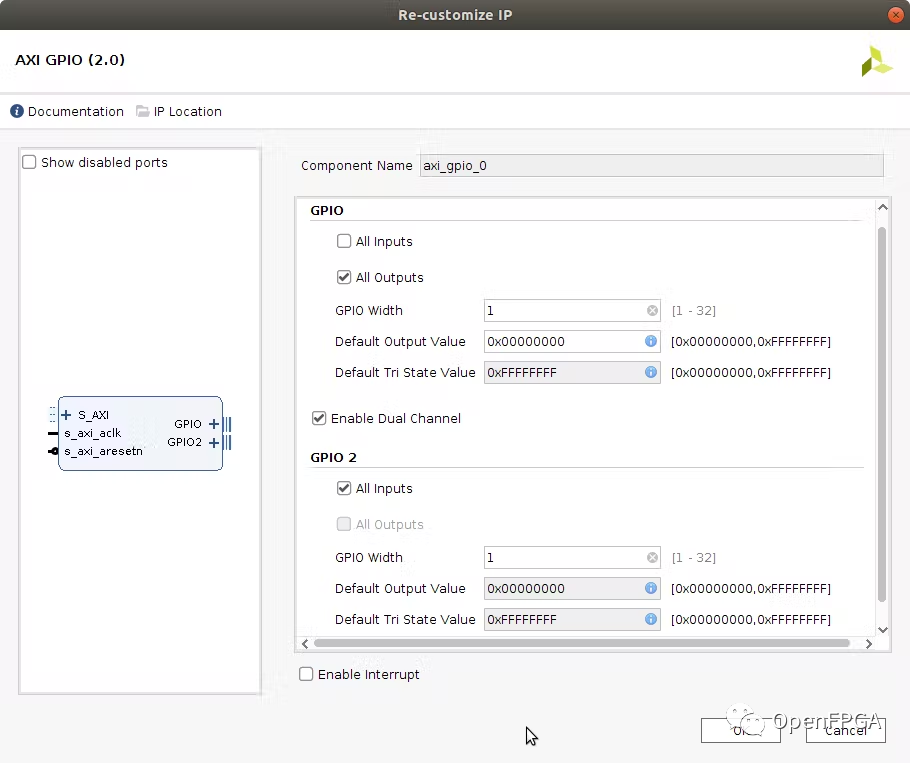

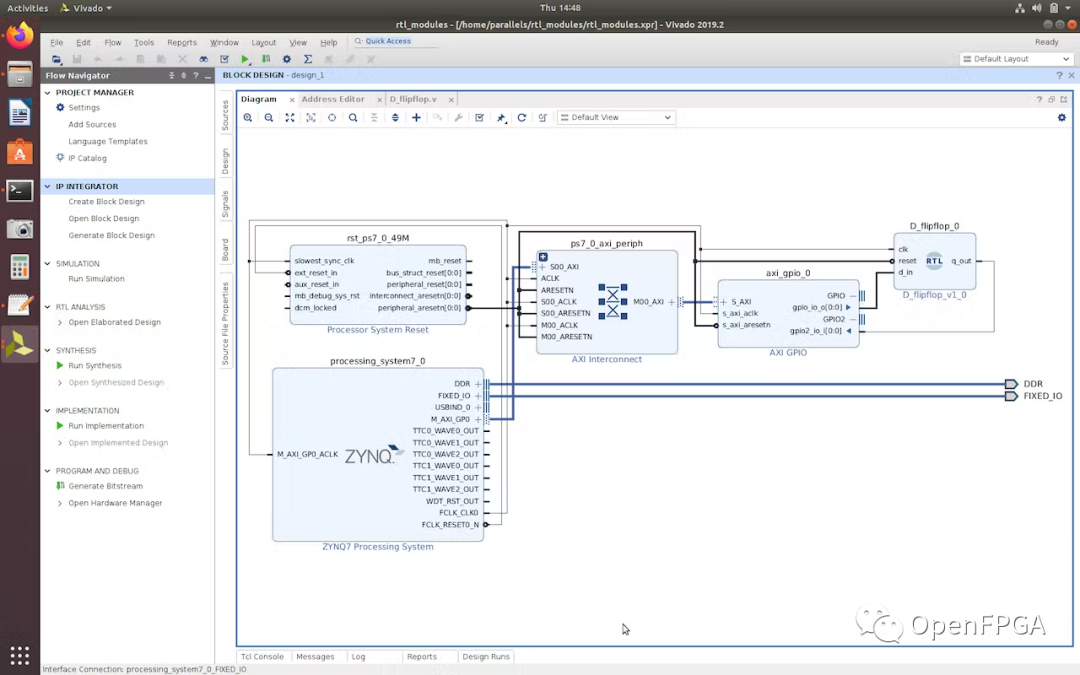

為了給觸發(fā)器提供源,我添加了一個(gè) AXI GPIO IP ,其中第一個(gè)通道作為輸出,第二個(gè)通道作為輸入。自動(dòng)連接即可。

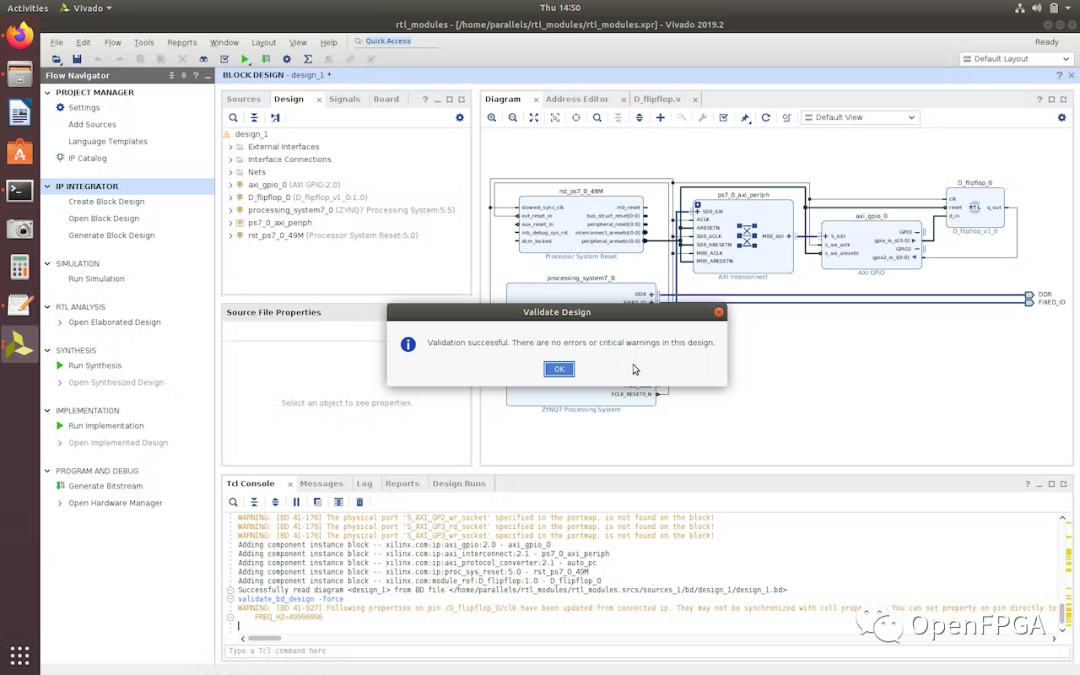

為 AXI GPIO 模塊運(yùn)行自動(dòng)連接后,將輸出 GPIO 通道連接到觸發(fā)器的 d_in,將觸發(fā)器的 q_out 連接到輸入 GPIO 通道。

全部連接好后,點(diǎn)擊那個(gè)勾勾進(jìn)行驗(yàn)證。

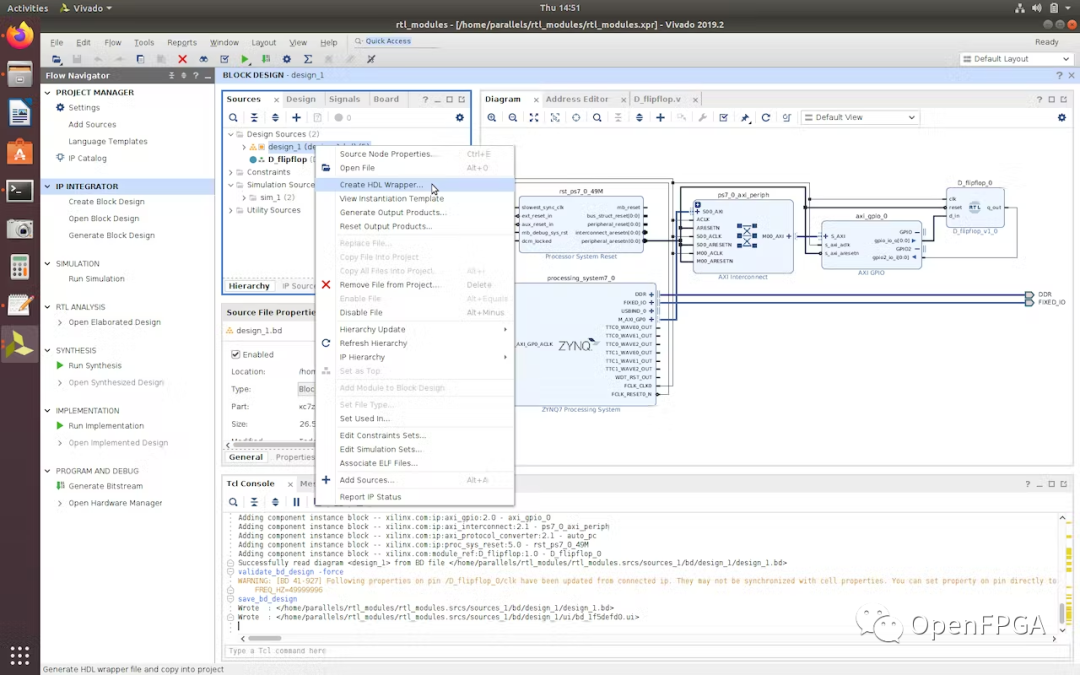

Block Design完成后,為Block Design生成頂層文件。

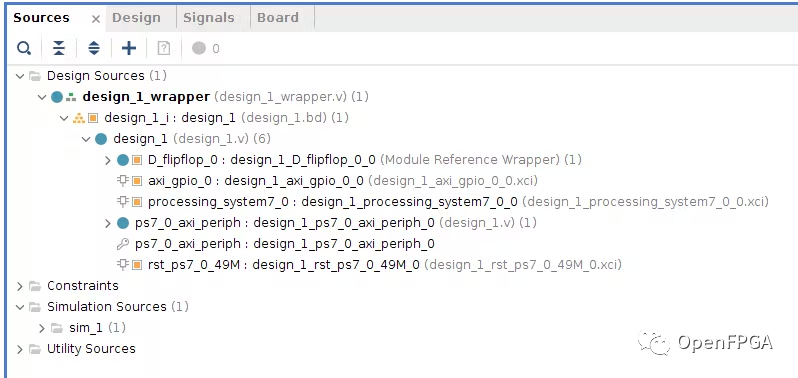

完成后可以看下整個(gè)項(xiàng)目的文件層次結(jié)構(gòu)。

就是這樣,OVER~

審核編輯:劉清

-

HDL

+關(guān)注

關(guān)注

8文章

328瀏覽量

47433 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59917 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14297 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66801

原文標(biāo)題:[Vivado那些事兒]將自定義 IP (HDL)添加到 Vivado 模塊設(shè)計(jì)(Block Design)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在Vivado 2015.2塊設(shè)計(jì)上打開(kāi)子層次結(jié)構(gòu)彈出一個(gè)新的Block Design窗口

無(wú)法打開(kāi)Vivado項(xiàng)目

使用VIVADO IDE設(shè)計(jì)的最有效方法是什么?

如何使用Vivado IP Block Design?

在Vivado中Block Design如何改名稱?

Vivado的helloword程序(一):硬件工程部分

Vivado Design Suite 2014.4.1 現(xiàn)已推出!

Block Design中的Bug的解決辦法及解決思路

Vivado Design Suite設(shè)計(jì)套件的UltraFast設(shè)計(jì)方法的介紹

C語(yǔ)言派生類的定義與繼承性認(rèn)識(shí)的實(shí)驗(yàn)和源代碼免費(fèi)下載

Vivado BDC (Block Design Container)怎么用

將RTL模塊添加到Block Design的步驟

Vivado Design Suite教程:動(dòng)態(tài)功能交換

Vivado Design Suite用戶指南:綜合

使用Vivado Block Design設(shè)計(jì)解決項(xiàng)目繼承性問(wèn)題

使用Vivado Block Design設(shè)計(jì)解決項(xiàng)目繼承性問(wèn)題

評(píng)論