由于機器學習、數據分析、物聯網等技術的不斷發展,以后生產的數據只會越來越多,并且越來越復雜。而半導體則是驅動這一切的引擎。為了日后能夠以更快的速度、更低的功耗和更少的延遲來傳輸更多數據,SoC設計也必須有所改變。摩爾定律逐漸趨向極限,在更小的芯片上集成更多的晶體管幾乎是不可能的,只有半導體創新才能實現各種性能的提升。 如今SoC設計比以往規模更大、更復雜,但同時也帶來了固有的集成挑戰:用于芯片設計非差異化方面的標準半導體IP模塊不再像以前那樣即插即用。如果獨立的IP模塊可在關鍵應用中提供全面的IP解決方案,從而簡化從裸片到電路板以及其他方面的集成路徑,情況會怎么樣呢?如果半導體IP供應商能夠提供更多像ASIC供應商那樣提供解決方案,又會怎么樣呢?

IP中的ASIC模型用例

對于芯片設計企業來說,是采用客戶自有工具(COT)模型,還是外包給ASIC供應商,是他們需要做出的重要決定。COT模型可能具備DIY成本優勢,但前提是芯片產量足夠高,并擁有自己的后端團隊和工具、業務運營和基礎設施、良好的代工關系和測試能力,只有這些條件都滿足,才能將設計付諸實踐。 但如果沒有像行業巨頭們那么大的運營規模該怎么辦呢?選擇ASIC供應商來處理芯片開發和制造工作應該會是絕大多數小規模公司的選擇。雖然這樣做相當于要放棄一些自主控制權,但承擔的風險卻低得多。開發者們只需將設計前端交給所選的ASIC供應商,然后等待芯片交付即可。 針對特定應用的類似模型如何映射到設計的IP部分?雖然IP可能會提供標準功能,但將這些功能集成到高端設計中的過程根本不是標準過程。要使用IP,就必須解決設計中各個組件部分的不一致問題,例如通道數量、時鐘速度、I/O數量和類型等等。此類變量的差異因應用而異。 為IP模塊建立針對特定應用、易于使用的集成模型可以幫助開發者克服這些障礙。與ASIC模型類似,包含完整應用解決方案的IP能夠有效降低成本和風險、減少資源用量,并縮短產品上市時間。 大多數應用都需要不同的定制。PCI Express(PCIe)接口就是一個很好的例子。在高性能計算(HPC)、存儲、汽車、移動以及其他應用等不同領域,接口IP通常在功耗、性能、面積和延遲(PPA&L)方面的權衡會大不相同。例如,如果PCIe IP用在服務器內,則需要具備高性能,這樣才能完成芯片之間的長距離連接(長達12至14英寸)。在這個例子中,良好的性能比功耗更重要。而在電池供電的移動設備中則并非如此,移動設備需要低功耗狀態,并可以為此在性能上做出權衡。 新思科技構建的IP已經超越了模塊本身,成為了一種適合多種不同應用場景的完整解決方案。無論應用是否要在各種功能、技術PPA&L或針對特定客戶的定制方面尋求差異化,這類解決方案可以滿足應用的各種需求。五個步驟,滿足特定應用需求

新思科技是唯一一家擁有滿足開發者所需的規模和基礎設施的IP供應商。針對特定應用IP解決方案,我們采用五步法:

-

成熟產品組合:新思科技擁有豐富的高質量IP核組合。例如,HPC SoC可以使用五到六個不同的IP模塊:以太網、PCIe、內存接口、Die-to-Die、安全性等。我們針對所有這些提供始終如一的用戶體驗,包括支持、集成、易用性等,并與代工廠建立了穩固的合作關系以運行測試芯片,并會替開發者對測試芯片進行表征并運行此芯片。

-

PPA&L:新思科技擁有多代架構,這些架構針對各種因應用而異的技術要求進行了優化,尤其是在功耗、性能、面積和延遲等方面。

-

完整解決方案:新思科技并不是單單提供PHY或控制器等IP模塊,而是可以為整個子系統提供完整的預驗證解決方案,使得接口IP即插即用,并針對PPA&L進行優化。

-

集成和支持:新思科技在構建和測試系統方面擁有豐富的經驗,能夠以輔助資料和支持的形式為開發者提供打造良好設計的秘訣,讓集成從一開始就能順利進行。輔助資料包括路由可行性研究、封裝基板指南、信號和電源完整性模型以及串擾分析。

- 生態系統:我們與整個生態系統的合作伙伴建立了長期的合作關系,比如代工廠、測試設備供應商、系統供應商,以及從超大規模用戶到邊緣等各種行業中其他經驗豐富的廠商。我們在許多標準機構中發揮著主導作用,經常幫助定義以太網、PCIe、UCIe、MIPI、USB等標準,因此我們的IP符合關鍵規范,并能幫助開發者成功實現互操作性。與各大代工廠密切的合作,也使得我們了解工藝幾何結構及其發展。

面向復雜高級SoC設計的

一站式半導體IP解決方案

與ASIC供應商的開發過程非常相似,新思科技IP開發過程涉及大量的嚴格調查。新思科技能夠深刻理解各項設計挑戰,并會在現實環境中復證大型SoC設計,并進行充分集成,以提供完整解決方案,從而簡化高級設計流程,幫助開發者們取得成功。 新思科技對PHY、PCS或MAC IP進行布局布線,并能夠快速關閉時序。新思科技的IP從裸片到封裝基板,再到電路板都由自己完成,以確保發生高速封裝逸出的層數最少。新思科技構建了一個擁有數百條通道的大型客戶SoC模型,然后深入分析該SoC來了解串擾和IR壓降。 新思科技善于總結自身經驗,并整理了一套完整的準則來分享這些知識。過去,開發者只是在選擇IP后收到相關功能的.gds文件并上傳到FTP站點,艱難的集成工作都要自己完成。那樣的日子現在已經一去不復返了。現在開發者們可以通過我們整理的準則來了解如何將IP模塊放在一起,集成到封裝中,并構建電路板。新思科技始終致力于簡化設計工作,加快設計速度,將開發者們從高度迭代的設計過程中解脫出來。 雖然很難單獨復證“每一位”客戶的情況,但通過從早期采用者那里所汲取的經驗,并結合了其獨特的經驗和挑戰。在與開發者們聯手簡化設計的過程中,新思科技也同時構建了自己的庫。這些經驗將成為開發者們的強大助力。

為開發者們提供最強力支持

新思科技廣泛涉足各個半導體設計領域,在各種垂直市場積攢了豐富的經驗和知識,并具備提供特定應用解決方案所需的規模和基礎設施。新思科技對于在現實場景中定制標準半導體IP的經驗十足,為開發者們提供完整IP解決方案,這樣不但能夠助力開發者縮短產品上市時間,還可降低風險和成本。

原文標題:從獨立模塊到完整解決方案,IP開啟ASIC模式

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

新思科技

+關注

關注

5文章

805瀏覽量

50387

原文標題:從獨立模塊到完整解決方案,IP開啟ASIC模式

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

國外服務器獨立ip的好處

Cadence展示完整的PCIe 7.0 IP解決方案

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰的任務!

新思科技推出業界首款PCIe 7.0 IP解決方案

如何使用AT固件開啟ESP32 Ethernet DHCP Server模式?

新思科技推出業界首款PCIe 7.0 IP解決方案

西門子推出Solido IP驗證套件,為下一代IC設計提供端到端的芯片質量保證

多端口能量路由實時控制仿真系統解決方案

原生獨立ip的原理是什么?

NVMe Host Controller IP實現高性能存儲解決方案

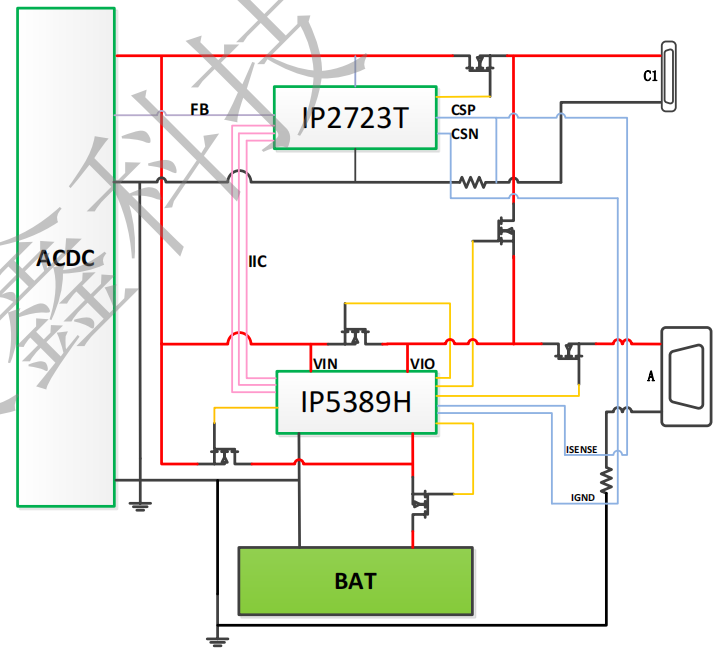

IP5389H+IP2723T適配器移動電源方案-AC獨立方案

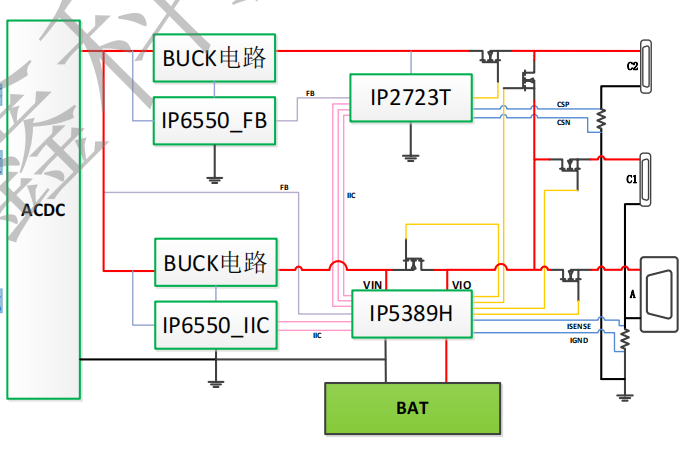

IP5389H+IP2723T適配器移動電源-ACC獨立方案

從百兆到百G,DWDM光模塊的演進

從獨立模塊到完整解決方案,IP開啟ASIC模式

從獨立模塊到完整解決方案,IP開啟ASIC模式

評論