已發表的文章

本章節將簡要介紹安森美(onsemi)近期正在進行的研究。參考文獻部分列出了相關出版物,可為讀者提供希望獲取的所有細節,以便更深入地了解這些技術主題。

偏置溫度不穩定性 (BTI)

眾所周知,BTI是硅器件的退化模式,由于在半導體/氧化物界面或附近產生陷阱或陷阱電荷,MOSFET的閾值電壓漂移,最終導致導通電阻增加的不利影響。SiC MOSFET也受到影響,而且需要應對寬帶隙材料,這使得研究工作更加復雜。在直流模式和開關模式下,都需要充分了解材料的行為。

多年來,安森美一直將SiC/SiO2界面表征及其本征可靠性評估作為工作重點之一,并建立了一個研究網絡,通過選定的研究合作伙伴和實驗技術,研究和改善界面狀態和遷移率(見圖4)。

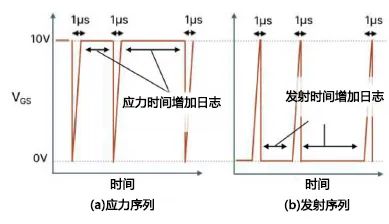

通過使用高溫(正和負)柵極偏置應力,對封裝后的器件進行導通和關斷狀態的靜態BTI評估,包括應力后電氣參數的漂移分析。動態 BTI評估則需要更全面的方法。安森美投入相應資源來研究超快速偏置溫度不穩定性(UF-BTI),并對施加正(PBTI)或負(NBTI)柵極應力(或兩者)時的閾值電壓(Vth)漂移進行測量和建模,如圖10所示。

圖10 用于研究SiC MOSFET上超快速BTI的應力/測量/發射序列示意圖

在PBTI期間,“視在”Vth將漂移到更高的電壓(由于電子俘獲),而在NBTI期間,“視在”Vth將漂移到更低的電壓(由于電子發射或空穴俘獲)。PBTI具有一個長久可恢復分量,而NBTI只是部分可恢復。

傳統的IDVG表征方案無法捕獲快速分量。但在典型開關應用中(100 kHz,即大約5到10 秒),快速BTI分量將占主導地位,有可能成為潛在的應用障礙。

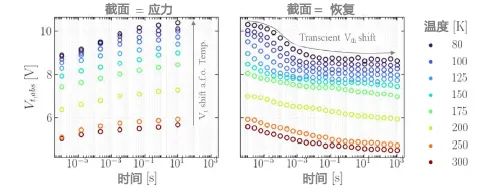

安森美收集的數據低至秒級范圍,并且覆蓋了廣闊的溫度范圍,包括低溫。

圖11 VG = +10 V的PBTI期間和后續恢復期間

Vth漂移與時間和溫度的函數關系

圖12 Vg = -10 V的NBTI期間和后續恢復期間

Vth漂移與時間和溫度的函數關系

具體步驟如下:

◆提取俘獲發射時間(CET)圖(Vth漂移由俘獲的電荷引起,分布在能量和空間中)。圖11顯示了在10 V PBTI應力條件下,Vth在應力期間和后續恢復期間的漂移,圖12則為-10 V NBTI應力下

◆Vth漂移的直流和交流建模(快速BTI分量用于應用,慢速BTI分量用于長期本征可靠性)

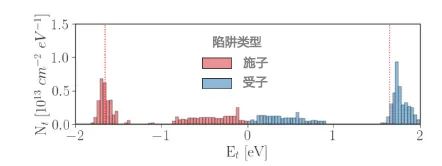

◆提取物理模型(缺陷類型、能量和深度),如圖13所示

◆預測實際應用要求下的壽命。

圖13 在NBTI和PBTI(使用Comphy模型)之后擬合絕對Vth漂移

從而可提取陷阱分布

低溫UF-BTI研究結果已在ISPSD2022上發表[4]。

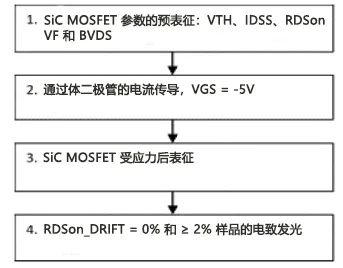

體二極管退化

SiC MOSFET中的體二極管應力引起的雙極退化會導致導通電阻增加,這是由正向偏置時流經體二極管的電流觸發的。這種退化有時也會報告為正向電壓漂移或關斷狀態的泄漏增加。圖14描述了該測試程序,而圖15則顯示了脈沖測量期間的正向壓降VF和電流ID。

圖14雙極退化測試程序

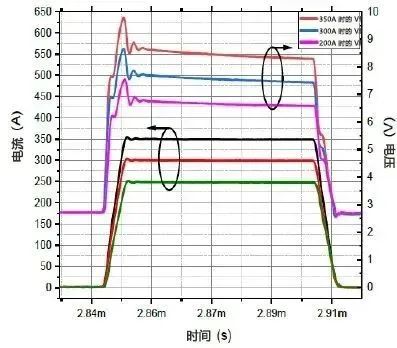

圖15 在250、300和350 A 且VGS = -5 V時的脈沖電流測量期間

測得的體二極管瞬態正向壓降VF和電流ID

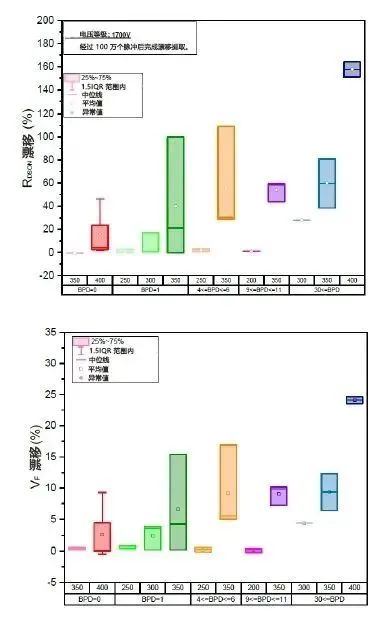

安森美評估了這種退化機制——最近在ECSCRM2021 [2]上發表了一項研究結果,對SiC MOSFET裸片中的BPD進行獨立映射[CX1],以建立體二極管應力后的RDSon漂移與器件中BPD數量之間的相關性。RDSon和VF漂移隨器件中BPD數量的增加而明顯增加。然而,必須使用極高的電流密度(J > 1600 A/cm2)才能觀察到無BPD時MOSFET的顯著退化(圖16)。

圖16 1700 V 25 mΩ SiC MOSFET上的RDSon和VF漂移與BPD數量以及電流的關系

體二極管應力為100 萬個50 秒的長脈沖

安森美針對所有SiC技術節點實施了以下措施:

◆實行目檢,對每個生產晶圓進行全面的基晶面位錯(BPD)掃描

◆采用高摻雜的外延緩沖層,將限制BPD堆垛層錯的發展

◆最后,對最大電流密度的設計規則進行了定義,將其保持在每個MOSFET的安全工作區域內。

由于綜合考慮了這三個因素,可以認為,安森美SiC MOSFET技術在高達1200 V時不受體二極管退化效應的影響。

動態應力

動態條件下的退化是與寬帶隙材料相關的問題之一。安森美已在內部開發的測試臺上開展動態應力研究(樣本量有限)。下面我們介紹一個室溫動態柵極應力測試的示例。

關于較大樣本量(例如三個批次,每批次80 件)的動態應力測試,目前正在開發(內部開發以及與設備供應商合作開發)相應解決方案。

室溫動態柵極應力:在T = 25℃、VDS = 0 V條件下,使用在-8 V 和20 V之間切換、占空比為50%的柵極驅動器,實施瞬態且無過沖的VGS應力[3]。

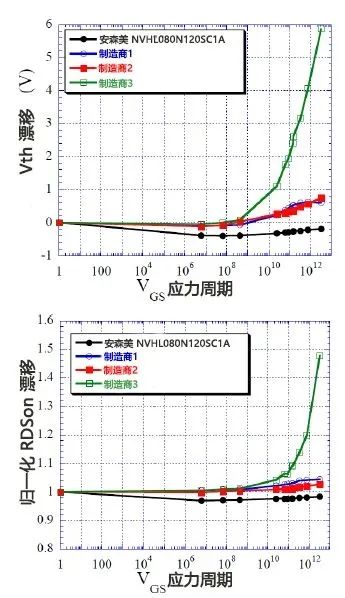

圖17 安森美的商用1200 V 80 mΩ SiC MOSFET和其他三個制造商的1200 V SiC MOSFET產品的Vth漂移和歸一化RDSon漂移

在不同的時間間隔后中斷應力測量,以運行由Vth和RDSon組成的測試程序。圖17顯示了安森美的商用1200 V 80 mΩ SiC MOSFET以及其他三個制造商的1200 V SiC MOSFET產品的Vth漂移和歸一化RDSon漂移(其中兩個制造商的VGS = -8 V,超出了數據手冊的額定值)。

總結

如本白皮書所述,安森美開發了一套全面的跨部門合作方案來評估SiC產品,高效且可靠地將其投放于市場。

縝密的設計方法、嚴格的生產監控、制造控制、充分的篩選和穩健的認證計劃相結合,為SiC產品的穩定與可靠奠定了基礎。

本文簡要介紹了一些SiC器件所特有的挑戰,進而引述了安森美對其進行表征和建模的方法。

我們已發表的文章提供了安森美正在進行的物理參數研究(欲了解最新研究成果,請閱讀參考文獻)。

參考文獻

[1]

SiC 柵極氧化物壽命提取和建模的充電擊穿 (QBD) 方法——P. Moens1、J. Franchi1、J. Lettens1、L. De Schepper1、M. Domeij1 和 F. Allerstam1——1安森美——ISPSD 2020

[2]

1700 V SiC MOSFET 的脈沖正向偏置體二極管應力與基晶面位錯的獨立映射——S. Kochoska1、M. Domeij1、S. Sunkari1、J. Justice1、H. Das1、H. Lee1, X.Q.Hu1 和 T. Neyer1——1安森美——ECSCRM 2021

[3]

平面型 SiC MOS 技術的柵極氧化層可靠性和 Vth 穩定性——M. Domeij1、J. Franchi1、S. Maslougkas1、P. Moens1、J. Lettens1、J. Choi1 和 F. Allerstam1——1安森美——ECSCRM 2021

[4]

碳化硅金屬氧化物半導體場效應晶體管的低溫超快偏置溫度不穩定性陷阱分析——F. Geenen1、F. Masin2、A. Stockman1、C. De Santi2、J. Lettens1、D. Waldhoer3、M. Meneghini2、T. Grasser3 和 P. Moens1——1安森美比利時;2意大利帕多瓦大學;3奧地利維也納理工大學——ISPSD 2022

往期推薦

碳化硅(SiC)——寬禁帶半導體材料的征服之旅(第一部分)

原文標題:碳化硅(SiC)——寬禁帶半導體材料的征服之旅(第二部分)

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

32文章

1703瀏覽量

92127

原文標題:碳化硅(SiC)——寬禁帶半導體材料的征服之旅(第二部分)

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

碳化硅與傳統硅材料的比較

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

碳化硅SiC制造工藝詳解 碳化硅SiC與傳統半導體對比

碳化硅SiC在電子器件中的應用

注冊開放,搶占坐席 | 英飛凌寬禁帶論壇全日程首發

SIC 碳化硅認識

碳化硅(SiC)——寬禁帶半導體材料的征服之旅(第二部分)

碳化硅(SiC)——寬禁帶半導體材料的征服之旅(第二部分)

評論