DATACLK輸出邊沿精度高度依賴于輸入CLK信號的相位噪聲。DATACLKP/N 源自 CLKP/N 輸入,因此對系統的整體保真度貢獻了最少的額外抖動或占空比誤差。本文檔詳細介紹了MAX19693的建立和保持時序規格,以及其總峰峰值抖動的實驗室測量。

介紹

系統時序分析通常采用加性抖動計算,以確保在溫度、電壓和工藝變化范圍內滿足正確的總線時序。從其他信號派生的時鐘信號表現出占空比失真和抖動增加。千兆赫范圍內的時鐘速率會增加這些附加時序誤差的影響。

MAX19693工作在高達2GHz的時鐘頻率。它對輸入CLK進行分頻以創建用于同步上游數字源的DATACLK信號。DATACLK 信號的微小時序變化可能導致數據接口違反設置和保持時序規范。準確量化這些誤差可實現更穩健的系統設計。

數據CLK輸出和數據輸入時序

MAX19693的負保持時間會導致采樣窗口在采樣邊沿之前塌陷。但是,負保持時間并不排除使用更長或正保持時間,它只是意味著采樣在設置后很早就發生。保持時間可以更長,設計人員必須確保它們不違反后續設置時間要求。

DAC具有多個具有各種傳播延遲的內部時鐘,這些時鐘決定了設置和 t拿相對于 DATACLK 輸出信號的規格。MAX19693還支持雙倍數據速率(DDR)和四路數據速率(QDR)數字輸入速率。在 DDR 或 QDR 模式下,內部時鐘系統的運行速度都比 DATACLK 快。在這種情況下,內部CLK在每個偶數時鐘上升沿采樣,而DATACLK輸出從每個奇數時鐘上升沿轉換。數據系統的內部工作原理通常被掩蓋,但只要最終用戶遵循時序規范,它們就不應該成為問題。

數據輸出函數

DATACLK是一種差分LVDS信號,用于將源數據(FPGA)與DAC輸入時鐘同步,以便在高速下正確進行采樣對齊。源自DAC輸入時鐘的內部信號用于鎖存四個12位LVDS輸入端口上接收的數字數據:DAP/N[11:0]、DBP/N[11:0]、DCP/N[11:0]和DDP/N[11:0]。為了正確對輸入數據端口信號進行時間對齊,該內部鎖存時鐘的一個版本作為輸出信號提供給用戶(DATACLK)。DATACLK 可以配置為 DDR 信號,它使用 DATACLK 的上升沿(0° 相位)和下降沿(180° 相位)來同步輸入數據的鎖存,也可以配置為四通道數據速率 (QDR),它使用上升(0° 相位)、上升 + 90°、下降(180° 相位)和下降 + 90° 來鎖存 DAC 輸入數據。

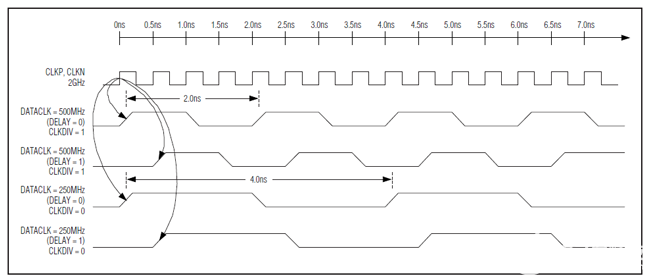

圖1.DATACLK 輸出和 CLK 輸入時序對齊。

LVDS DATACLKP/DATACLKN (DATACLK) 輸出信號通過基本的 D 觸發器(2 分頻或 4 分頻)和緩沖電路從 CLKP/CLKN (CLK) 輸入 DAC 時鐘獲得。由于DATACLK輸出信號來自CLK輸入信號,因此輸入時鐘上的任何抖動都將轉換為輸出時鐘,并增加由內部緩沖和時鐘域電路引起的系統抖動誤差。此抖動“加法器”是所調查的值。

DATACLK 抖動和占空比誤差 – 實驗室分析

使用三種方法來測量DATACLK和CLK抖動,以提取DATACLK的占空比誤差和抖動“加法器”。

首先是使用安捷倫/是德科技無限 DSA91304A(13GHz,40Gsps)數字信號分析儀,同時使用標準 50?輸入和差分探頭(7GHz,安捷倫 1134A)。輸入DAC CLK的測量表明羅德與施瓦茨SMF100A信號發生器的抖動值大于預期。隨后確定數字信號分析儀(DSA)的指定采樣誤差在500mV范圍內為~17mV,從而產生~12ps峰峰值(~12ps)的最佳抖動測量能力。????P-P).DSA的表現比這更好,在~6psP-P,但這不會提供回答 DATACLK 抖動問題所需的整體測量功能。

第二次嘗試使用泰克 Tek 11801C 數字采樣示波器 (DSO) 同時使用 50?采樣頭 (SD-26) 和高阻抗采樣頭 (SD-14)。遺憾的是,用于 Tek DSO 的觸發方法要求將輸入信號的一個版本連接到觸發輸入,通常使用功率分配器和延遲線 (DL-11)。由于 DATACLK 是輸入時鐘的 4 分頻版本,因此采樣邊沿會產生類似眼圖的跡線。Tek 11801C 沒有高級抖動分析,直方圖功能無法提供可靠的測量結果(大約 40ps?P-P輸入時鐘源的抖動)。

使用泰克 DPO72304SX 數字熒光示波器 (DPO) 測量 DATACLK 抖動的最終方法取得了成功。

實驗室設置

MAX19693評估板用于測量抖動。評估板(EV kit)通過FPGA夾層卡(FMC)適配器連接到Xilinx VC707 FPGA評估系統,為MAX19693 RF DAC提供輸入數據。羅德與施瓦茨SMF100A信號發生器配置為2.000GHz、+15dBm輸出,作為連接到CLK SMA的MAX19693EVKIT的CLK源。評估板由兩路實驗室電源供電,一種為兩個V供電1.8V。?DD和 AVCLK,第二個為 3.3V 用于 AVDD。泰克 DPO72304SX DPO 用于測量 CLK 輸入和 DATACLK 輸出抖動值。輸入的CLK信號在評估板上的三路變壓器網絡之后連接到Tek P7713差分探頭。類似地,另一個P7713差分探頭連接到評估板上R2、R3輸出抽頭的DATA-CLKP/N輸出信號。Tek DPO 配置為觸發目標信號,并設置為使用 CLK 輸入和 DATACLK 輸出信號的“一鍵抖動”設置來測量抖動。

實驗室結果

DAC時鐘輸入抖動和數據時鐘輸出抖動的評估可以采取幾種不同的形式。Tek DPO 具有內置的分析算法,可測量時間間隔誤差 (TIE)、總抖動 (TJ)、隨機抖動 (RJ) 和確定性抖動 (DJ)。鑒于兩個信號都應該是周期性的,并且基本上是固定的頻率/數據速率,這些方法中的任何一種都應該指示MAX19693“增加”到系統中的抖動。

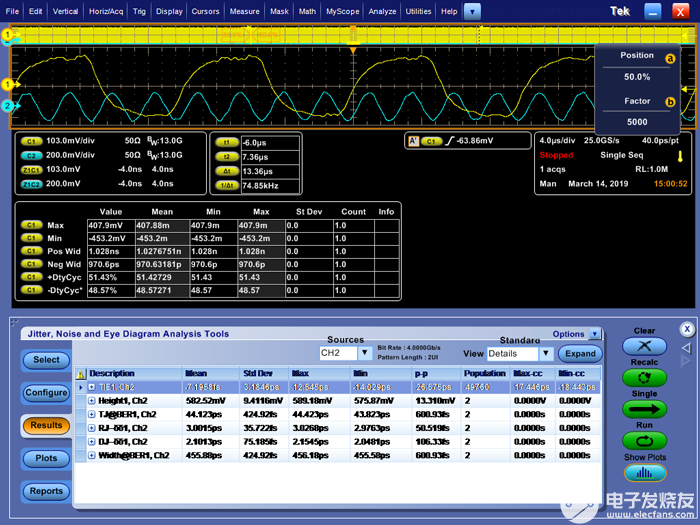

圖5.CLK 輸入抖動分析。

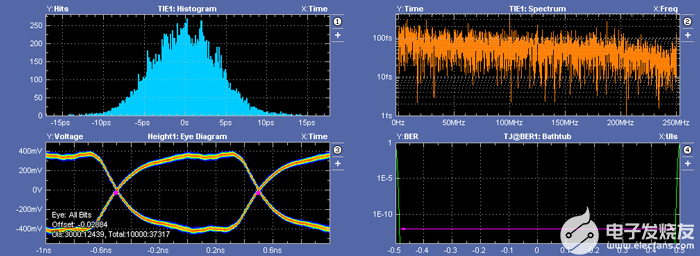

圖6.CLK 直方圖、眼圖、TIE 光譜和浴缸圖。

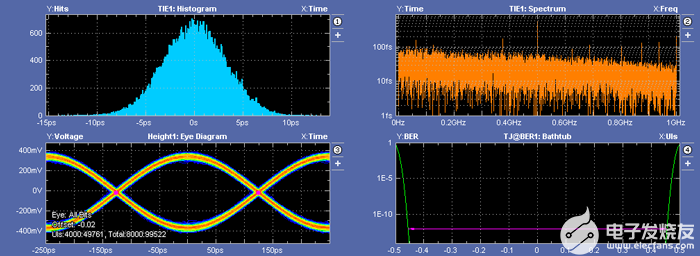

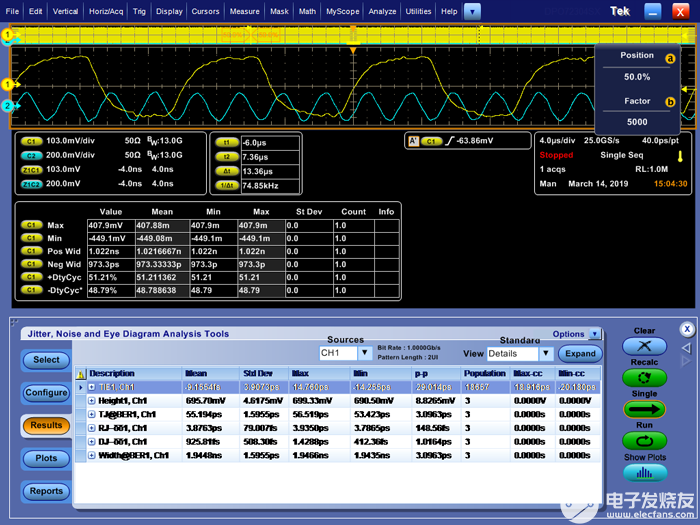

圖7.DATACLK 輸入抖動分析。

圖8.DATACLK 直方圖、眼圖、領帶譜和浴缸圖。

下表匯總了收集的三個數據集以及輸入 CLK 和輸出 DATACLK 抖動測量的結果值:

表 1.CLK 輸入抖動和 DATACLK 輸出抖動測量

| 樣本 | 綁P-P | 泰杰P-P | RJP-P | DJP-P |

|---|---|---|---|---|

| CLK 1 | 26.6點 | 601fs | 51fs | 106fs |

| DATACLK 1 | 29.0點 | 3.1點 | 149fs | 1.0ps |

| CLK 2 | 26.6點 | 601fs | 66.8fs | 727FS |

| DATACLK 2 | 29.0點 | 4.2點 | 275fs | 1.0ps |

| CLK 3 | 26.6點 | 788FS | 66.8fs | 727FS |

| 數據CLK 3 | 32,321 | 5.7點 | 275fs | 2.9點 |

直接從輸出峰峰值抖動中減去輸入峰峰值抖動,得到MAX19693的增量或總“增加”抖動。這種“增加”的抖動包括占空比誤差和系統抖動的成分,如表2所示。

表 2.MAX19693 “新增”數據抖動

| 樣本 | 綁P-P | 泰杰P-P |

|---|---|---|

| 樣本 1 | 2.4點 | 2.5點 |

| 樣本 2 | 3.3秒 | 3.6點 |

| 樣本 3 | 5.5點 | 4.9點 |

| 樣品 平均 | 3.7點 | 3.7點 |

對這三個樣本求平均值,得出總“增加”峰峰值抖動的典型值為3.7ps。

數據抖動 – 仿真

仿真結果使用100mV幅度和10ps脈沖寬度的電源瞬變以及1ps上升/下降時間(500ps周期和+V)運行。e和 -Ve錯開250ps。仿真選項包括無噪聲選項、瞬態噪聲選項和具有“蠕變”(每個周期10ps)的電源噪聲序列,可提供異步電源噪聲結果。蠕變仿真為300ns運行,噪聲從100ns開始,在300ns時持續到結束,因此允許在200ns噪聲窗口內使用大約100個周期的500MHz時鐘。

表 3.MAX19693 模擬數據抖動

| 模擬 | 最小值 | 麥克斯 | JP-P | s |

|---|---|---|---|---|

| 無噪音 | -5.7fs | 10.8fs | 16.5fs | 3.3fs |

| 瞬態噪聲 | -9.6fs | 14.4fs | 24.0fs | 5.4fs |

| 電源 噪音蠕變 | -1.56秒 | 2.12點 | 3.68點 | 0.84點 |

結論和建議

對內部電路的回顧和分析為“添加”到CLK輸入的DATACLK輸出抖動提供了2~4ps的保守估計。進一步的仿真和實際實驗室測量都表明峰峰值抖動值約為3.7ps。基于這些結果,Maxim建議MAX19693 DATACLK“增加”輸出抖動的保守值為4ps,用于時序預算計算。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605127 -

示波器

+關注

關注

113文章

6279瀏覽量

185623 -

適配器

+關注

關注

8文章

1966瀏覽量

68164

發布評論請先 登錄

相關推薦

低抖動高精度時鐘發生器MAX3625B相關資料分享

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

評估低抖動PLL時鐘發生器的電源噪聲抑制

MAX19692EVKIT-MAX19693EVKIT: Evaluation Kit for the MAX19692/MAX19693 Data Sheet MAX19692EVKIT-MAX19693EVKIT: Evaluation Kit for the MAX1969

MAX19693 DCLK抖動評估

MAX19693 DCLK抖動評估

評論