JESD204A/JESD204B串行接口行業(yè)標(biāo)準(zhǔn)旨在解決以高效和節(jié)省成本的方式將最新的寬帶數(shù)據(jù)轉(zhuǎn)換器與其他系統(tǒng)IC互連的問題。其動機是標(biāo)準(zhǔn)化接口,通過使用可擴展的高速串行接口,減少數(shù)據(jù)轉(zhuǎn)換器與其他設(shè)備(如現(xiàn)場可編程門陣列(FGPA)和片上系統(tǒng)(SoC))設(shè)備)之間的數(shù)字輸入/輸出數(shù)量。

趨勢表明,新應(yīng)用以及現(xiàn)有應(yīng)用的進(jìn)步正在推動對采樣頻率和數(shù)據(jù)分辨率越來越高的寬帶數(shù)據(jù)轉(zhuǎn)換器的需求。與這些寬帶轉(zhuǎn)換器之間傳輸數(shù)據(jù)會帶來重大的設(shè)計問題,因為現(xiàn)有I/O技術(shù)的帶寬限制迫使轉(zhuǎn)換器產(chǎn)品需要更高的引腳數(shù)。因此,系統(tǒng)的PCB設(shè)計在互連密度方面變得越來越復(fù)雜。挑戰(zhàn)在于路由大量高速數(shù)字信號,同時管理電噪聲。提供具有GSPS采樣頻率的寬帶數(shù)據(jù)轉(zhuǎn)換器的能力,使用更少的互連,簡化了PCB布局挑戰(zhàn),并允許在不影響整體系統(tǒng)性能的情況下實現(xiàn)更小的外形尺寸。

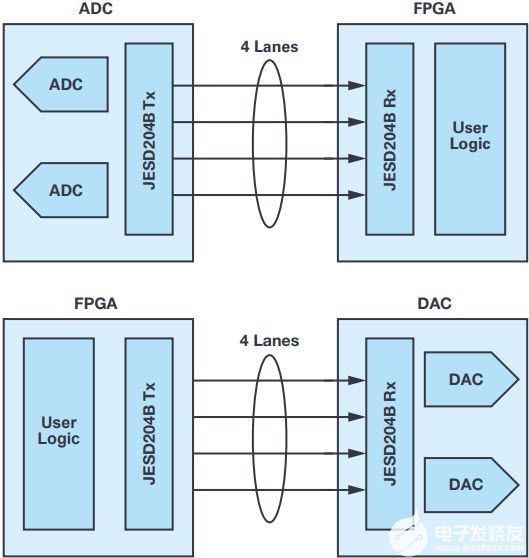

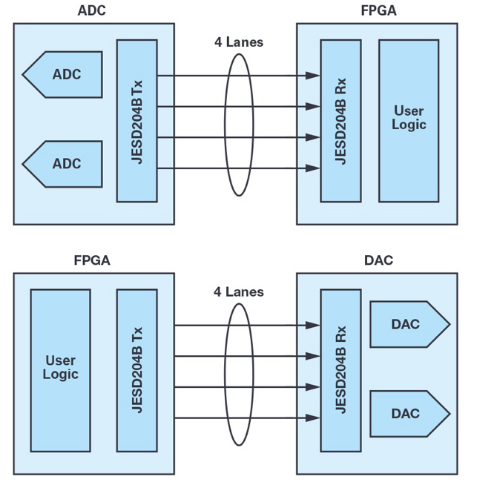

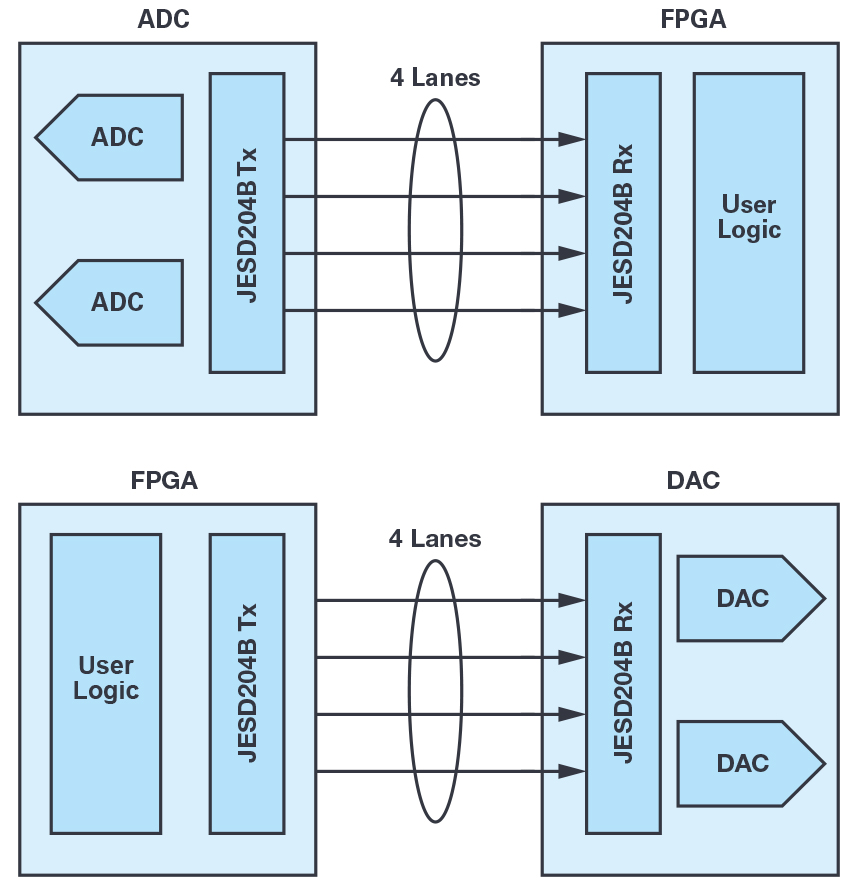

市場力量繼續(xù)要求在給定系統(tǒng)中提供更多特性、功能和性能,從而推動了對更高數(shù)據(jù)處理能力的需求。高速模數(shù)轉(zhuǎn)換器和數(shù)模轉(zhuǎn)換器-FPGA接口已成為一些系統(tǒng)OEM滿足其下一代數(shù)據(jù)密集型需求的限制因素。JESD204B串行接口規(guī)范專門用于通過尋址這一關(guān)鍵數(shù)據(jù)鏈路來幫助解決此問題。圖1顯示了使用JESD204A/JESD204B的典型高速轉(zhuǎn)換器-FPGA互連配置。

圖1.采用 JESD204A/JESD204B 接口的典型高速轉(zhuǎn)換器至 FGPA 互連配置(來源:Xilinx)。?

推動該規(guī)范部署的一些關(guān)鍵終端系統(tǒng)應(yīng)用,以及串行低壓差分信號(LVDS)和JESD204B之間的對比,是本文其余部分的主題。

推動對JESD204B需求的應(yīng)用

無線基礎(chǔ)設(shè)施收發(fā)器

當(dāng)今無線基礎(chǔ)設(shè)施收發(fā)器中使用的基于 OFDM 的技術(shù)(如 LTE)使用在 FPGA 或 SoC 設(shè)備上實現(xiàn)的 DSP 模塊驅(qū)動天線陣列元件,為每個用戶的手機生成波束。每個陣列元件都需要在發(fā)送或接收模式下每秒在FPGA和數(shù)據(jù)轉(zhuǎn)換器之間移動數(shù)百兆字節(jié)的數(shù)據(jù)。

軟件定義無線電

當(dāng)今的軟件定義無線電利用先進(jìn)的調(diào)制方案(可動態(tài)重新配置)和快速增加的信道帶寬,以提供前所未有的無線數(shù)據(jù)速率。天線路徑中的高效、低功耗、低引腳數(shù)FPGA至數(shù)據(jù)轉(zhuǎn)換器接口對其性能起著關(guān)鍵作用。軟件定義無線電架構(gòu)是多載波、多模無線網(wǎng)絡(luò)收發(fā)器基礎(chǔ)設(shè)施不可或缺的一部分,支持 GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX 和 TD-SCDMA。

醫(yī)療成像系統(tǒng)

包括超聲、計算斷層掃描 (CT) 掃描儀、磁共振成像 (MRI) 在內(nèi)的醫(yī)學(xué)成像系統(tǒng)可生成許多數(shù)據(jù)通道,這些數(shù)據(jù)通道通過數(shù)據(jù)轉(zhuǎn)換器流向 FPGA 或 DSP。 不斷增加的 I/O 數(shù)量要求使用中介層來匹配 FPGA 和轉(zhuǎn)換器引腳排列,從而增加了 PCB 的復(fù)雜性,從而推動了組件數(shù)量。這為客戶的系統(tǒng)增加了額外的成本和復(fù)雜性,而更高效的JESD204B接口可以解決這一問題。

雷達(dá)和安全通信

當(dāng)今先進(jìn)的雷達(dá)接收機上日益復(fù)雜的脈沖結(jié)構(gòu)正在將信號帶寬推向1 GHz或更高。最新一代有源電子縮放陣列(AESA)雷達(dá)系統(tǒng)可能有數(shù)千個元件。需要基于SERDES的高帶寬串行接口將陣列元件數(shù)據(jù)轉(zhuǎn)換器連接到處理傳入和生成傳出數(shù)據(jù)流的FPGA或DSP。

串行LVDS與JESD204B的比較

在LVDS系列和JESD204B接口之間進(jìn)行選擇

為了在使用LVDS或各種版本的JESD204串行接口規(guī)格的轉(zhuǎn)換器產(chǎn)品之間進(jìn)行最佳選擇,比較每個接口的特性和功能是有用的。表 1 中提供了簡短的表格比較。在SERDES級別,LVDS和JESD204之間的顯著區(qū)別是通道數(shù)據(jù)速率,與LVDS相比,JESD204支持每通道串行鏈路速度的三倍以上。在比較多器件同步、確定性延遲和諧波時鐘等高級特性時,JESD204B是唯一提供此功能的接口。需要寬帶寬多通道轉(zhuǎn)換器且對所有通道和通道的確定性延遲敏感的系統(tǒng)將無法有效使用 LVDS 或并行 CMOS。

| 功能 | 串行低密度驅(qū)動器 | JESD204 | JESD204A | JESD204B |

| 規(guī)范發(fā)布 | 2001 | 2006 | 2008 | 2011 |

| 最大通道速率 (Gbps) | 1.0 | 3.125 | 3.125 | 12.5 |

| 多車道 | 不 | 不 | 是的 | 是的 |

| 車道同步 | 不 | 不 | 是的 | 是的 |

| 多設(shè)備同步 | 不 | 是的 | 是的 | 是的 |

| 確定性延遲 | 不 | 不 | 不 | 是的 |

| 諧波時鐘 | 不 | 不 | 不 | 是的 |

LVDS 概述

LVDS是將數(shù)據(jù)轉(zhuǎn)換器與FPGA或DSP接口的傳統(tǒng)方法,LVDS于1994年推出,旨在提供比現(xiàn)有RS-422和RS-485差分傳輸標(biāo)準(zhǔn)更高的帶寬和更低的功耗。隨著1995年TIA/EIA-644的發(fā)布,LVDS實現(xiàn)了標(biāo)準(zhǔn)化。LVDS的使用在1990年代后期有所增加,隨著2001年TIA/EIA-644-A的發(fā)布,該標(biāo)準(zhǔn)進(jìn)行了修訂。

LVDS使用具有低電壓擺幅的差分信號進(jìn)行高速數(shù)據(jù)傳輸。發(fā)射器通常驅(qū)動±3.5 mA電流,極性與邏輯電平相匹配,通過100 Ω電阻發(fā)送,在接收器處產(chǎn)生±350 mV電壓擺幅。始終導(dǎo)通的電流沿不同方向布線,以產(chǎn)生邏輯 1 和 0。LVDS的始終開啟特性有助于消除在單端技術(shù)中晶體管打開和關(guān)閉時有時會發(fā)生的同步開關(guān)噪聲尖峰和潛在電磁干擾。LVDS的差分特性也提供了對共模噪聲源的相當(dāng)大的抗擾度。TIA/EIA-644-A 標(biāo)準(zhǔn)建議最大數(shù)據(jù)速率為 655 Mbps,盡管它預(yù)測理想傳輸介質(zhì)的速度可能超過 1.9 Gbps。

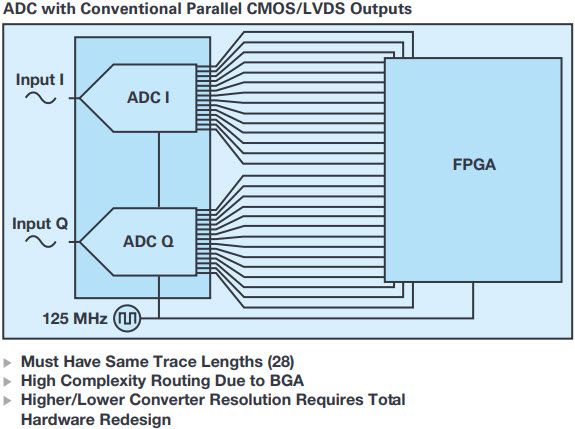

FPGA或DSP與數(shù)據(jù)轉(zhuǎn)換器之間數(shù)據(jù)通道數(shù)量和速度的大幅增加,特別是在前面描述的應(yīng)用中,給LVDS接口帶來了一些問題(見圖2)。在現(xiàn)實世界中,差分LVDS線的帶寬限制在約1.0 Gbps。在許多當(dāng)前應(yīng)用中,這就產(chǎn)生了對大量高帶寬PCB互連的需求,每個互連都是潛在的故障點。大量的走線也增加了PCB的復(fù)雜性或整體外形尺寸,從而提高了設(shè)計和制造成本。在某些應(yīng)用中,數(shù)據(jù)轉(zhuǎn)換器接口成為在帶寬密集型應(yīng)用中實現(xiàn)所需系統(tǒng)性能的限制因素。

圖2.使用并行CMOS或LVDS的系統(tǒng)設(shè)計和互連方面的挑戰(zhàn)。

JESD204B 概述

JESD204數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)由JEDEC固態(tài)技術(shù)協(xié)會JC-16接口技術(shù)委員會創(chuàng)建,旨在為數(shù)據(jù)轉(zhuǎn)換器提供更高速的串行接口,以增加帶寬并減少高速數(shù)據(jù)轉(zhuǎn)換器與其他設(shè)備之間的數(shù)字輸入和輸出數(shù)量。該標(biāo)準(zhǔn)基于IBM開發(fā)的8b/10b編碼技術(shù),該技術(shù)消除了對幀時鐘和數(shù)據(jù)時鐘的需求,能夠以更高的速度實現(xiàn)單線對通信。

2006年,JEDEC發(fā)布了針對單個3.125 Gbps數(shù)據(jù)通道的JESD204規(guī)范。JESD204接口是自同步的,因此無需校準(zhǔn)PCB走線的長度以避免時鐘偏差。JESD204利用許多FPGA上提供的SERDES端口來釋放通用I/O。

JESD204A于2008年發(fā)布,增加了對多個時間對齊數(shù)據(jù)通道和通道同步的支持。這種增強功能使得使用更高帶寬的數(shù)據(jù)轉(zhuǎn)換器和多個同步數(shù)據(jù)轉(zhuǎn)換器通道成為可能,對于蜂窩基站中使用的無線基礎(chǔ)設(shè)施收發(fā)器尤其重要。JESD204A還提供多器件同步支持,這對于使用大量ADC的器件(如醫(yī)療成像系統(tǒng))非常有用。

JESD204B是該規(guī)范的第三個修訂版,將最大通道速率提高到12.5 Gbps。 JESD204B還增加了確定性延遲,可在接收器和發(fā)射器之間傳達(dá)同步狀態(tài)。JESD204B中也引入了諧波時鐘,使得從具有確定性相位的低速輸入時鐘獲得高速數(shù)據(jù)轉(zhuǎn)換器時鐘成為可能。

結(jié)論

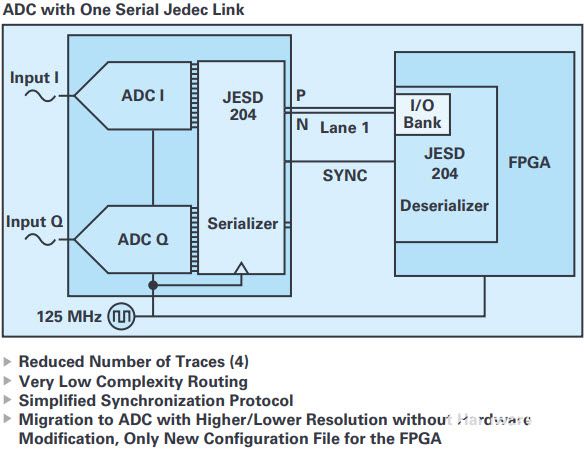

JESD204B工業(yè)串行接口標(biāo)準(zhǔn)減少了高速數(shù)據(jù)轉(zhuǎn)換器與FPGA和其他器件之間的數(shù)字輸入和輸出數(shù)量。更少的互連簡化了布局,并有可能實現(xiàn)更小的外形尺寸(參見圖 3)。這些優(yōu)勢對于各種高速數(shù)據(jù)轉(zhuǎn)換器應(yīng)用非常重要,例如無線基礎(chǔ)設(shè)施收發(fā)器、軟件定義無線電、醫(yī)療成像系統(tǒng)以及雷達(dá)和安全通信。ADI公司是JESD204標(biāo)準(zhǔn)委員會的原始參與成員,我們同時開發(fā)了兼容的數(shù)據(jù)轉(zhuǎn)換器技術(shù)和工具以及全面的產(chǎn)品路線圖。通過為客戶提供將我們的尖端數(shù)據(jù)轉(zhuǎn)換器技術(shù)與JESD204A/JESD204B接口相結(jié)合的產(chǎn)品,我們希望使客戶能夠解決他們的系統(tǒng)設(shè)計問題,同時利用這一重大的接口突破。

圖3.JESD204具有高速串行I/O功能,解決了系統(tǒng)PCB復(fù)雜性挑戰(zhàn)。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8784瀏覽量

148904 -

soc

+關(guān)注

關(guān)注

38文章

4247瀏覽量

219970 -

lvds

+關(guān)注

關(guān)注

2文章

1052瀏覽量

66378

發(fā)布評論請先 登錄

相關(guān)推薦

寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的JESD204B與串行LVDS接口考量

JESD204B的系統(tǒng)級優(yōu)勢

串行LVDS和JESD204B的對比

JESD204標(biāo)準(zhǔn)解析

JESD204B串行接口時鐘的優(yōu)勢

FPGA高速數(shù)據(jù)采集設(shè)計之JESD204B接口應(yīng)用場景

FPGA高速數(shù)據(jù)采集設(shè)計之JESD204B接口應(yīng)用場景

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協(xié)議有什么特點?

JESD204B中的確定延遲到底是什么? 它是否就是轉(zhuǎn)換器的總延遲?

寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的JESD204B與串行LVDS接口考量

JESD204B協(xié)議介紹

針對高速數(shù)據(jù)轉(zhuǎn)換器的最新高速JESD204B標(biāo)準(zhǔn)帶來了驗證挑戰(zhàn)

寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的JESD204B與串行LVDS接口考量

JESD204B與串行LVDS接口在寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用中的考慮因素

JESD204B與串行LVDS接口在寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用中的考慮因素

評論