ADI最新一代高速DAC具有出色的相位噪聲,可在下一代低相位噪聲、快速跳頻捷變RF/微波頻率合成器中實(shí)現(xiàn)尺寸、重量、功耗/性能和成本優(yōu)勢(shì)。一個(gè)挑戰(zhàn)是,為了實(shí)現(xiàn)這種DAC功能,固定DAC采樣時(shí)鐘必須具有非常低的SSB相位噪聲,這超出了主流寬帶VCO PLL的能力。本文提供了一種采用模擬鑒相器(PD)的方法,與傳統(tǒng)的相位/頻率鑒相器頻率合成器相比,該方法可將環(huán)內(nèi)相位噪聲性能提高10 dB至20 dB。為了滿足最苛刻的相位噪聲系統(tǒng)要求,建議的固定時(shí)鐘實(shí)現(xiàn)方案是使用模擬PLL鎖定的介質(zhì)諧振器振蕩器(DRO)。其它更常規(guī)的例子是采用市售的MMIC VCO提供的。本文解釋了基于DAC的粗/細(xì)混頻器微波合成器的優(yōu)勢(shì),并提供了框圖、測(cè)量的相位噪聲結(jié)果和應(yīng)用電路,以便感興趣的工程師可以在實(shí)驗(yàn)室中試用。

介紹

航空航天與國防(ADEF)社區(qū)對(duì)相位噪聲有著合理的癡迷。例如,雷達(dá)、電子戰(zhàn)(EW)和大量其他應(yīng)用需要快速跳頻頻率合成器和激勵(lì)器提供一流的相位噪聲性能。這些頻率功能模塊通常設(shè)置關(guān)鍵系統(tǒng)性能,例如雷達(dá)雜波衰減,并用于更大的頻率轉(zhuǎn)換、調(diào)諧器和調(diào)制方案。ADI公司最新一代高速DAC具有極低的加性相位噪聲,實(shí)現(xiàn)了簡化敏捷頻率生成架構(gòu)的長期夢(mèng)想。向基于 DAC 的頻率合成的演進(jìn)可實(shí)現(xiàn)更小的尺寸、重量、功耗和成本 (SWaP-C) 解決方案,取代更大、更昂貴的信號(hào)鏈。然而,為了實(shí)現(xiàn)潛在的相位噪聲,系統(tǒng)設(shè)計(jì)人員不能只使用任何舊的采樣時(shí)鐘源方案。本文介紹在實(shí)現(xiàn)采樣時(shí)鐘以獲得最佳DAC相位噪聲時(shí)的相位噪聲考慮因素和權(quán)衡。更進(jìn)一步,本文探討了一種在Ku波段至Ka波段范圍內(nèi)實(shí)現(xiàn)寬帶快速跳頻頻率合成器的低相位噪聲方法。提供應(yīng)用電路框圖和測(cè)量數(shù)據(jù),以便設(shè)計(jì)人員可以在工作臺(tái)上復(fù)制實(shí)驗(yàn)數(shù)據(jù),并在設(shè)計(jì)中利用該方法。

電子戰(zhàn)和雷達(dá)中的SSB相位噪聲影響

ADEF傳感系統(tǒng)需要在惡劣的電磁環(huán)境中以時(shí)間關(guān)鍵的方式攔截不希望被檢測(cè)到的敵方目標(biāo)的微小信號(hào)或回波。瞬時(shí)無雜散動(dòng)態(tài)范圍(SFDR)是一個(gè)品質(zhì)因數(shù),通常用于表示接收系統(tǒng)在存在大阻塞信號(hào)的情況下對(duì)小信號(hào)的檢測(cè)能力。SFDR以IMD2或IMD3和本底噪聲表示,本底噪聲假定是均勻的,即從任何載波相位噪聲肩上充分偏移,以避免頻率偏移依賴性使方程過于復(fù)雜。這是一個(gè)可接受的假設(shè),比如說,距離載波10 MHz。然而,電子戰(zhàn)和雷達(dá)應(yīng)用需要在這個(gè)10 MHz偏移區(qū)域內(nèi)更靠近載波的位置運(yùn)行。因此,SFDR中沒有明確捕獲的一個(gè)重要方面是,在不埋在載波噪聲肩中的情況下,可以保持多近的發(fā)射載波動(dòng)態(tài)范圍。該噪聲肩是單邊帶(SSB)相位噪聲,表示為載波頻率偏移的函數(shù):L(f)。

通信和衛(wèi)星通信系統(tǒng)可能更關(guān)心單個(gè)集成均方根抖動(dòng)數(shù),該抖動(dòng)數(shù)將相位噪聲肩負(fù)中的總噪聲積分在目標(biāo)偏移上,而大多數(shù)雷達(dá)和電子戰(zhàn)設(shè)計(jì)人員更關(guān)心載波特定頻率偏移處的點(diǎn)SSB相位噪聲包絡(luò)。通常,這需要盡可能低,特別是在1 kHz至1 MHz范圍內(nèi)的多普勒偏移時(shí)。頻率合成器設(shè)計(jì)人員面臨的挑戰(zhàn)是,這個(gè)關(guān)鍵任務(wù)區(qū)域通常是與鎖相環(huán)(PLL)噪聲結(jié)構(gòu)相關(guān)的高相位噪聲平臺(tái)期。最小化該區(qū)域的噪聲貢獻(xiàn)是本文的主要目標(biāo)。

如果本文有一個(gè)要點(diǎn),請(qǐng)記住,大多數(shù)雷達(dá)和電子戰(zhàn)系統(tǒng)理想情況下希望采樣時(shí)鐘SSB相位噪聲饋送到DAC以下~10 dB,允許DAC設(shè)置系統(tǒng)的相位本底噪聲,而不是時(shí)鐘!在實(shí)踐中,我們將看到這是非常困難的。這證明了ADI公司的DAC相位噪聲性能已經(jīng)變得多么出色,以及基于DAC的合成器具有多么大的變革性。

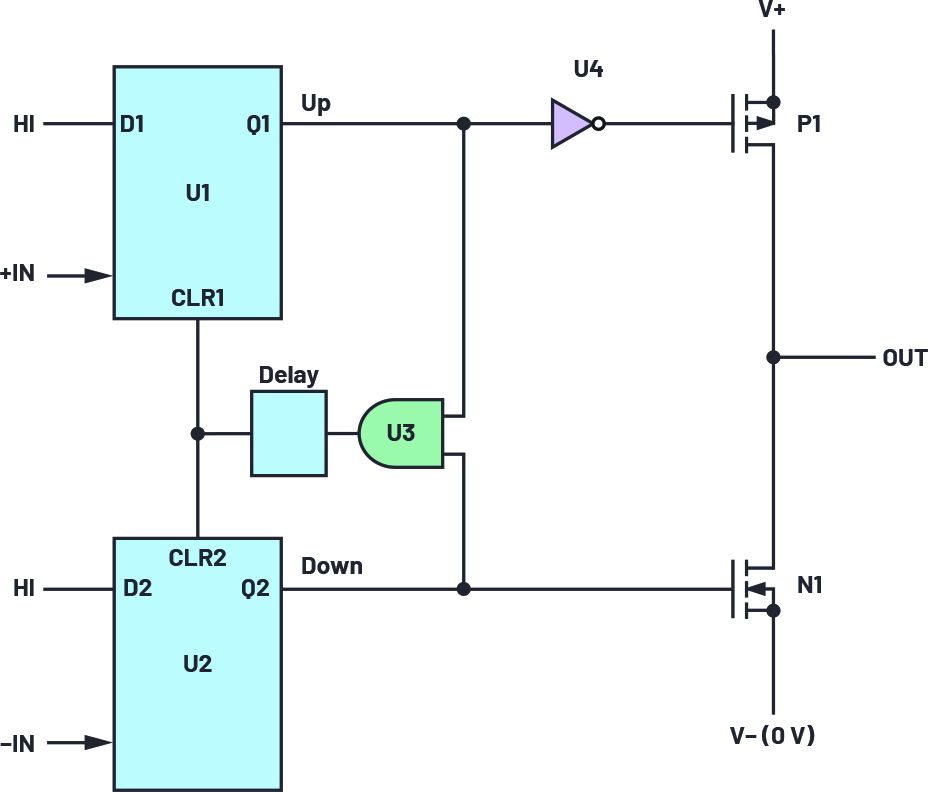

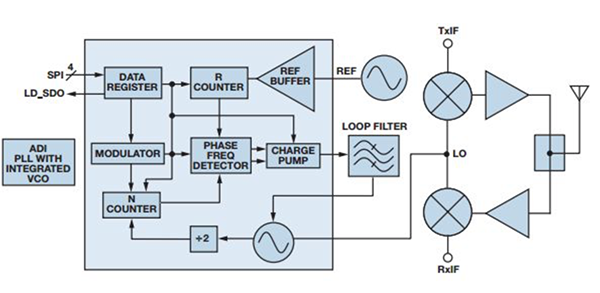

在整個(gè)討論中,DPLL 通常是指采用有源相位/頻率檢測(cè)器 (PFD) 和分頻器方案的任何集成 PLL 或頻率合成器芯片。圖1所示為經(jīng)典數(shù)字PFD。

圖1.經(jīng)典的數(shù)字相位/頻率檢測(cè)器(PFD)。

APLL是指采用無源混頻器作為鑒相器(PD)。需要明確的是,SSB相位噪聲適用性對(duì)每個(gè)人來說意味著不同的東西,這取決于特定的任務(wù)要求和應(yīng)用用例。多倍頻程微波調(diào)諧、可編程性、易用性和低SWaP-C是寬帶MMIC PLL-VCO合成器的現(xiàn)代優(yōu)勢(shì)。對(duì)于本文未介紹的大多數(shù)寬帶調(diào)諧頻率合成器應(yīng)用,ADI的集成PLL-VCO頻率合成器是最佳選擇。我們只考慮DAC固定采樣時(shí)鐘的這個(gè)特定用例。例如,表 1 中使用的描述符旨在傳達(dá)與此利基用例相關(guān)的比較性能。

現(xiàn)在有什么不同?

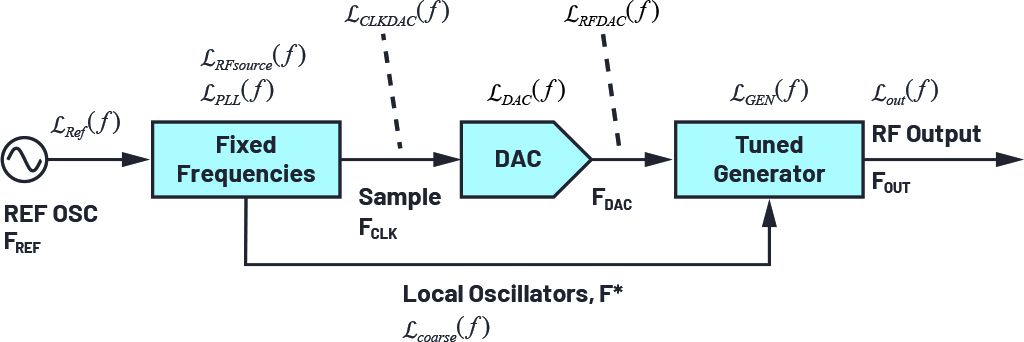

過去,使用真實(shí)中頻實(shí)現(xiàn)基于DAC的高速合成的障礙是DAC的采樣速率相對(duì)較低(即100 MSPS)和低模擬頻率帶寬(即250 MHz)。在使用較舊的DAC時(shí),低IF使轉(zhuǎn)換變得困難,并迫使一些笨重的,也許是不可能的RF濾波器。另一種選擇,倍頻,是不切實(shí)際的,因?yàn)樗璧母叱朔ㄒ蜃樱ǚQ為N)轉(zhuǎn)化為DAC加性相位噪聲L代數(shù)轉(zhuǎn)換器(f) 過高,特別是在地板上。提醒從F1上變頻到F2時(shí)相干頻率轉(zhuǎn)換的影響:

換言之,ADI的較低采樣速率DAC加成相位噪聲很好,但它的直接載波頻率太低,無法在低SWaP-C下實(shí)際轉(zhuǎn)換為微波范圍。

快進(jìn)到今天,游戲已經(jīng)改變。DAC采樣速率、模擬帶寬和由此產(chǎn)生的直接實(shí)際中頻頻率能力已增加到多GHz,加性相位噪聲L代數(shù)轉(zhuǎn)換器(f) 仍然非常出色,因此我們終于有了一款多功能構(gòu)建模塊,為實(shí)現(xiàn)低 SWaP、微波、寬帶、快速調(diào)諧頻率合成器開辟了各種新選擇。

使用高速DAC的寬帶微波頻率合成器

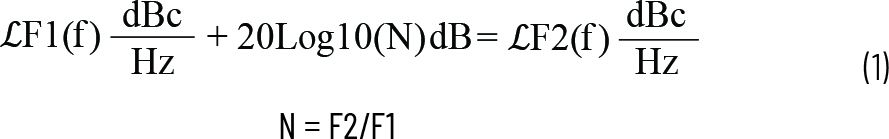

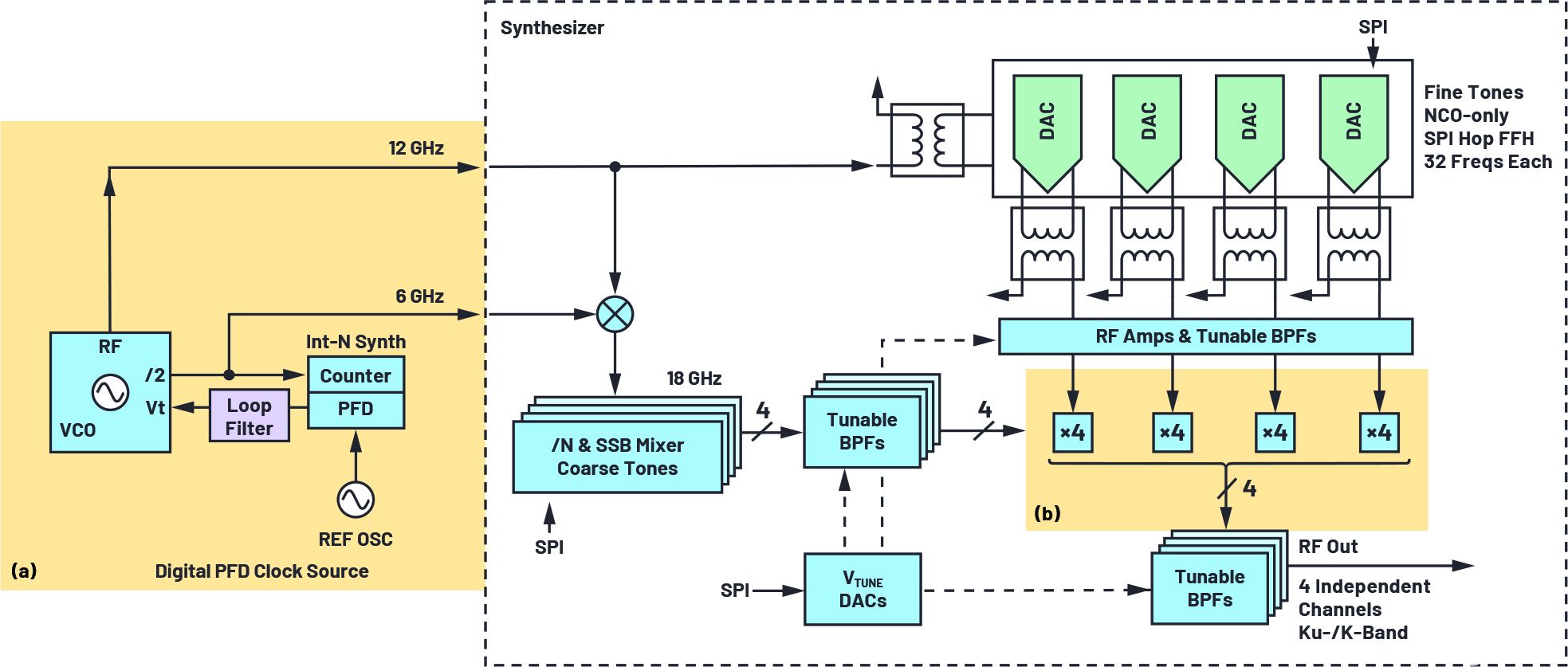

圖2是我們?cè)诖颂峒暗幕贒AC的頻率合成器的基本描述。每個(gè)功能塊在與載波的不同偏移處對(duì)整體相位噪聲的貢獻(xiàn)略有不同。本次討論的中心點(diǎn)是如何設(shè)計(jì)每個(gè)模塊,以使出色的DAC添加劑(也稱為殘差)相位噪聲能力L代數(shù)轉(zhuǎn)換器(f) 設(shè)置系統(tǒng)相位噪聲。我們會(huì)發(fā)現(xiàn)這不是微不足道的。

?代數(shù)轉(zhuǎn)換器(f) 加性相位噪聲由多個(gè)因素組成,例如器件 1/f 噪聲和隨機(jī)模式等實(shí)現(xiàn)技術(shù)。電源相位噪聲下降是一個(gè)臭名昭著的妖怪,謹(jǐn)慎的低噪聲LDO實(shí)現(xiàn)至關(guān)重要。

參考振蕩器 F裁判是頻率合成器將被鎖定的系統(tǒng)相位參考信號(hào),通常在100 MHz范圍內(nèi)。?裁判(f) 是絕對(duì)源相位噪聲,它將頻率合成器相位噪聲設(shè)置為最接近的偏移,通常為 <1 kHz。使用SWaP-C平衡參考相位噪聲性能和頻率是一項(xiàng)重要的系統(tǒng)權(quán)衡:如果參考相位噪聲不足,則下游相位噪聲的恢復(fù)介于不可能和非常痛苦之間。不要在參考時(shí)鐘上偷工減料。

固定頻率模塊是鎖相環(huán) (PLL) 所在的位置,鎖相環(huán)將本地 RF 電壓控制源 (RF 源) 鎖定到頻率參考。射頻源絕對(duì)相位噪聲的選擇L射頻源(f)是與SWaP-C權(quán)衡的另一個(gè)權(quán)衡,SWaP-C設(shè)置肩部與本底噪聲相遇處的遠(yuǎn)偏移相位噪聲。PLL技術(shù)是一種加性相位噪聲貢獻(xiàn)者L鎖 相 環(huán)(f) 確定臨界中間偏移平臺(tái)(通常為 1 kHz 至 1 MHz)處的相位噪聲。PLL有源環(huán)路濾波器使用的運(yùn)算放大器具有重要的噪聲貢獻(xiàn),因此歸入這一類。這個(gè)中間偏移SSB相位噪聲區(qū)域?qū) 的影響最大射頻發(fā)展委員會(huì)(f)并且經(jīng)常決定合成器任務(wù)的適用性。本討論的第一部分側(cè)重于最小化采樣時(shí)鐘相位噪聲L中科達(dá)克(f) 允許DAC相位噪聲L代數(shù)轉(zhuǎn)換器(f) 支配L射頻發(fā)展委員會(huì)(f)。

調(diào)諧發(fā)生器模塊是加性相位噪聲貢獻(xiàn)者L根(f) 將DAC RF輸出與一組固定頻率與絕對(duì)相位噪聲L 混合粗(f) 上變頻為寬帶捷變射頻輸出。本討論的第二部分側(cè)重于最小化相位噪聲L的技術(shù)外(f) 和雜散,一旦你有你的DAC輸出,需要將其轉(zhuǎn)換為更高的微波頻段。

圖2.基于DAC的寬帶頻率合成和相位噪聲貢獻(xiàn)因素框圖。

圖3.相位噪聲對(duì)整個(gè)DAC時(shí)鐘源相位噪聲的貢獻(xiàn)。

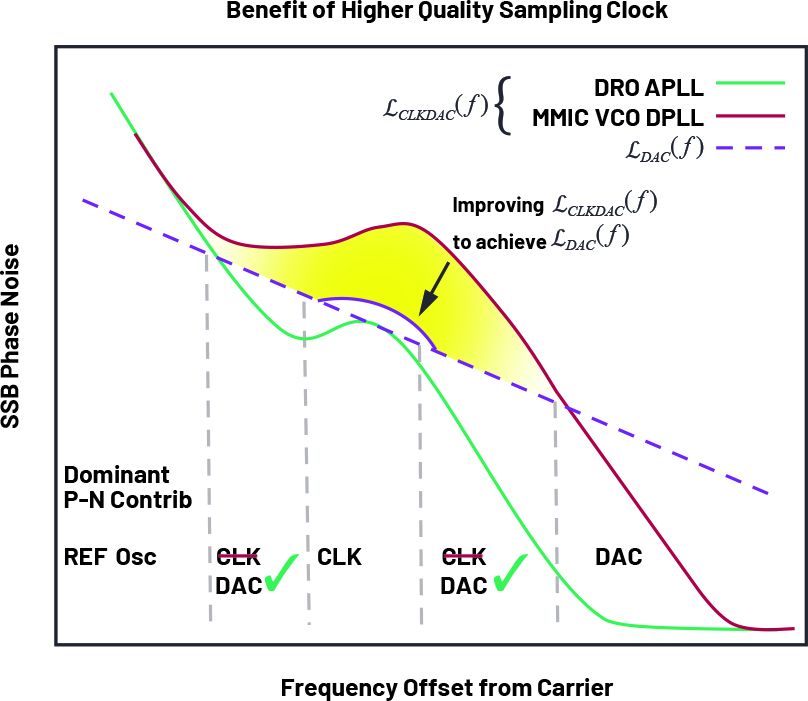

圖4.您需要較低相位噪聲采樣時(shí)鐘的原因。

總結(jié)圖2、圖3和圖4中的重要相位噪聲關(guān)系:

關(guān)鍵目標(biāo)是 L代數(shù)轉(zhuǎn)換器(f) 設(shè)定 L射頻發(fā)展委員會(huì)(f),L的捐款盡可能少中科達(dá)克(f)。

?外(f < 1 kHz) 為 L裁判(f < 1 kHz) + 20LogN (N = 最終/參考頻率比)。

?中科達(dá)克(f > 1 kHz) 高度依賴于我們選擇如何實(shí)現(xiàn) L射頻源(f)和L鎖 相 環(huán)(f). L裁判(f) 本底噪聲也將在這里發(fā)揮作用。

?外(f > 1 kHz)取決于上述因素,以及我們?nèi)绾芜x擇上變頻L射頻發(fā)展委員會(huì) (f > 1 kHz)。建議使用 L 的方法粗(f < 1 kHz)。

新的DAC優(yōu)勢(shì),新的時(shí)鐘挑戰(zhàn)

我的一位同事引用了悲傷守恒的自然法則,當(dāng)傳統(tǒng)的信號(hào)鏈被重新吸吮以支持較低的SWaP-C進(jìn)步時(shí)。該定律在這里適用,因?yàn)槲覀冎恍枰fSWaP-C的一小部分來執(zhí)行基于DAC的調(diào)諧發(fā)生器功能塊(悲傷減少),但固定頻率源變得更加微妙(悲傷增加)。由于DAC的加性相位噪聲非常低(這是一件好事,這也是本文的原因),并且由于采樣時(shí)鐘現(xiàn)在相當(dāng)高,為12 GSPS(這也是一件好事,允許可以合理濾除真正的IF),采樣時(shí)鐘源所需的SSB相位噪聲迫使我們考慮更復(fù)雜的時(shí)鐘源解決方案。換言之,使用MMIC VCO-PLL不足以實(shí)現(xiàn)DAC加性相位噪聲潛力。

我們首先考慮圖2中參考振蕩器、固定頻率塊和DAC的相互作用。固定頻率模塊由鎖相環(huán)中的RF壓控振蕩器(VCO)組成,該鎖相環(huán)將RF源鎖定到參考振蕩器。鎖相環(huán)由一個(gè)分頻器或轉(zhuǎn)換器、PFD和采用運(yùn)算放大器的有源環(huán)路濾波器組成。

在以后的討論中比較了三個(gè)不同的實(shí)現(xiàn)示例:

| 描述 | 射頻 Osc | PD/PFD |

SSB 相位 噪聲 |

SWaP-C |

易用性 |

| 毫米式 VCO DPPL | 多媒體視頻 | 主動(dòng)式聚苯乙烯 | 好 | 最好 | 最好 |

| MMIC VCO APLL | 多媒體視頻 |

無源 混頻器PD |

更好 | 更好 |

窮 |

| 德羅阿普爾 | 剛果民主共和國 |

無源 混頻器PD |

最好 | 窮 |

窮 |

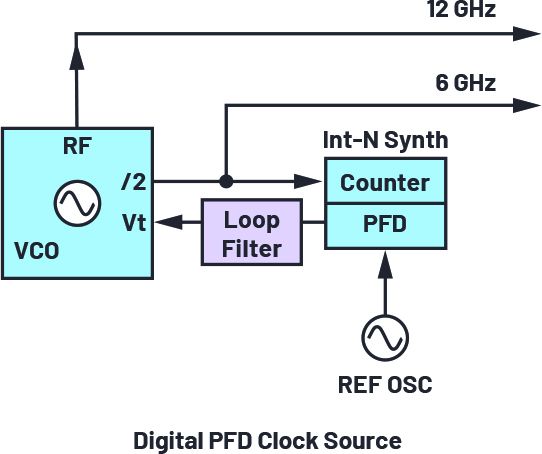

舊的又是新的

模擬鑒相器比污垢更古老,是現(xiàn)代集成有源相位/頻率檢測(cè)器(PFD)合成器的祖父。在絕大多數(shù)現(xiàn)代寬帶頻率合成器應(yīng)用中,它們已經(jīng)過時(shí),考慮到集成頻率合成器IC的進(jìn)步,這是理所當(dāng)然的。當(dāng)需要在最佳SWaP-C下使用寬帶調(diào)諧VCO-PLL時(shí),模擬PD是一個(gè)糟糕的選擇。那么,為什么在此DAC時(shí)鐘用例中選擇模擬PD?這與無源模擬PD的出色附加相位噪聲有關(guān)。PD比較兩個(gè)輸入頻率,并輸出代表相位差的拍頻信號(hào)。當(dāng)比較頻率正交或鎖定時(shí),PD輸出0 V DC信號(hào)。在采用有源PFD的整數(shù)N分頻和小數(shù)N分頻頻率合成器中,兩個(gè)比較輸入信號(hào)的最大工作頻率通常在100 MHz至500 MHz左右。 HMC698系列等頻率合成器/PFD可以工作高達(dá)1.3 GHz的PFD輸入,這有利于相位噪聲,但代價(jià)是更高的直流功率。最重要的是,有源PFD本身會(huì)產(chǎn)生加性1/f噪聲,并且高度依賴于實(shí)現(xiàn),也就是說,并非所有結(jié)果都是平等的。因此,在此示例中選擇了HMC440,其具有非常低的PFD 1/f噪聲。在將環(huán)內(nèi)PD頻率轉(zhuǎn)換為RF輸出頻率時(shí),以盡可能高的頻率操作PD的經(jīng)驗(yàn)法則可降低該環(huán)內(nèi)加性PD相位噪聲平臺(tái)的理論20LogN增加。像ADF4401A這樣的轉(zhuǎn)換環(huán)路可以實(shí)現(xiàn)盡可能高的PFD頻率,同時(shí)避免來自有源分頻器的噪聲。

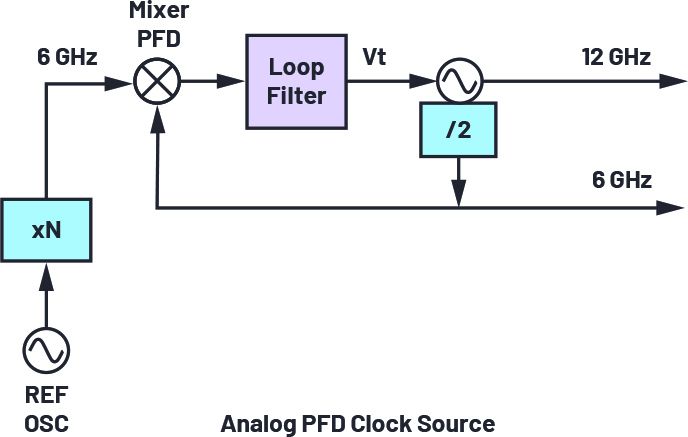

圖5.模擬鎖相環(huán) (APLL) 的簡化框圖。

圖6.數(shù)字鎖相環(huán) (DPLL) 的簡化框圖。

例如,讓我們考慮使用PFD的鎖相10 GHz RF輸出信號(hào),其附加噪聲為–153 dBc/Hz。為了簡化起見,我們假設(shè)PFD是主要的環(huán)內(nèi)噪聲貢獻(xiàn)因素(并不總是正確的)。以10 MHz運(yùn)行PFD將獲得以下帶內(nèi)相位噪聲(即平臺(tái)):

對(duì)于完全相同的情況,讓我們?cè)?100 MHz 時(shí)將 PFD 頻率高出 10×。環(huán)內(nèi)相位噪聲改善至:

20 dB 的優(yōu)勢(shì)是巨大的。始終將您的 PFD 時(shí)鐘盡可能高。使用基于模擬混頻器的PD有幾個(gè)優(yōu)點(diǎn)。

無源混頻器的加法噪聲非常低,因此通常可以忽略不計(jì)。運(yùn)算放大器有源環(huán)路濾波器噪聲成為環(huán)內(nèi)限制噪聲貢獻(xiàn)者。

比較頻率可以根據(jù)需要高,通常為多個(gè)GHz,這與環(huán)內(nèi)組件的殘余噪聲相平衡。通常,頻率越高,可用的殘余噪聲RF放大器選擇越小。

總之,最佳無源PD頻率足夠高,使得PD和帶內(nèi)分頻器的加性噪聲低于乘法參考振蕩器的絕對(duì)相位噪聲,但又不會(huì)太高,以免RF放大器殘余噪聲降低性能。需要多個(gè)RF放大器。

RF放大器殘余相位噪聲本身就是一個(gè)話題。工藝技術(shù)以及節(jié)點(diǎn)和電路架構(gòu)是重要因素。一般來說,Si BJT提供最佳性能,但頻率范圍(<1 GHz)有限。砷化鎵HBT是次佳的器件,通常可通過Ku波段獲得(例如,ADL8150、HMC606LC5、HMC3653和HMC3587)。

pHEMT放大器在高頻下廣泛使用,但由于殘余相位噪聲變化很大,因此應(yīng)謹(jǐn)慎使用。一般來說,pHEMT相位噪聲不是很大,并且會(huì)出現(xiàn)溫度變化。

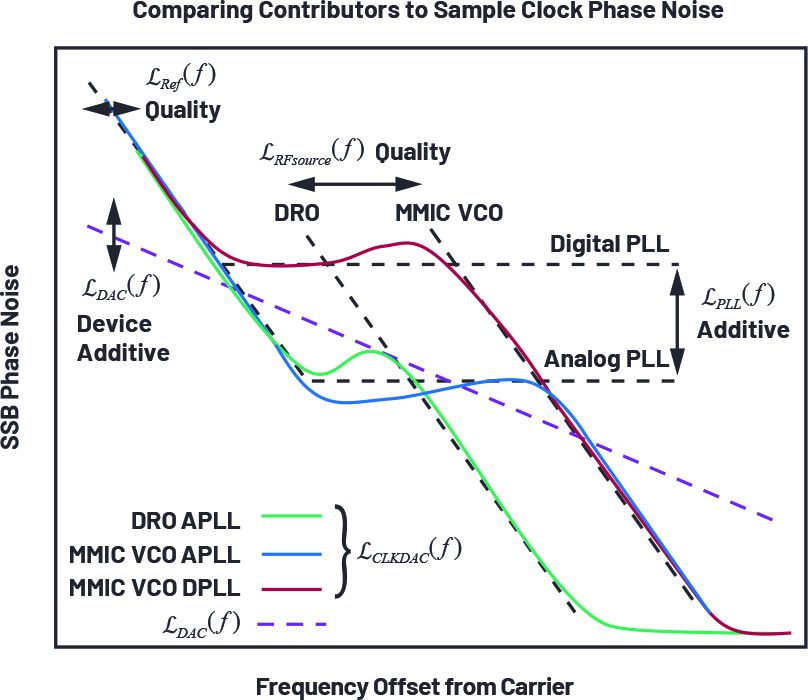

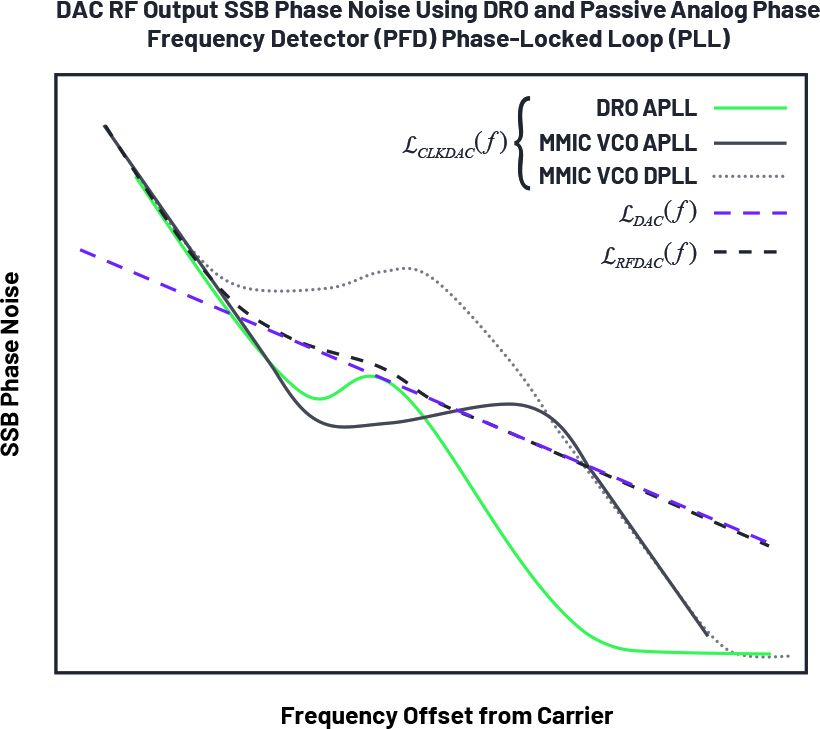

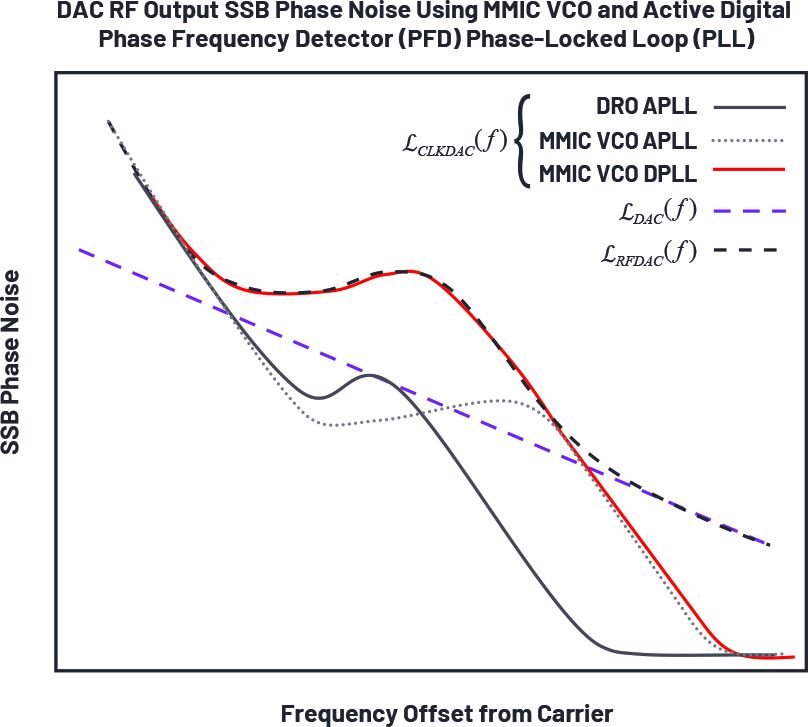

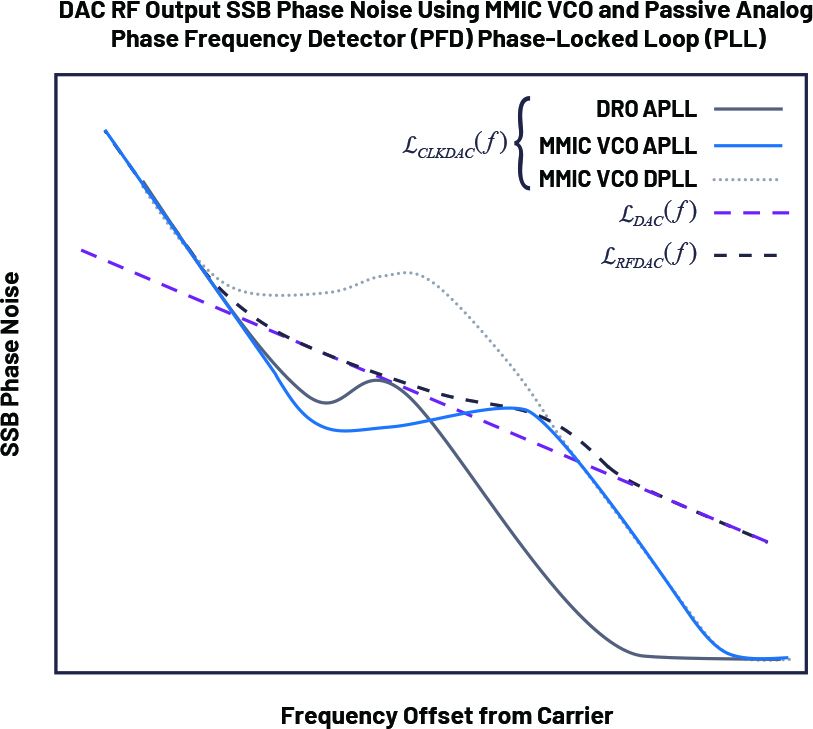

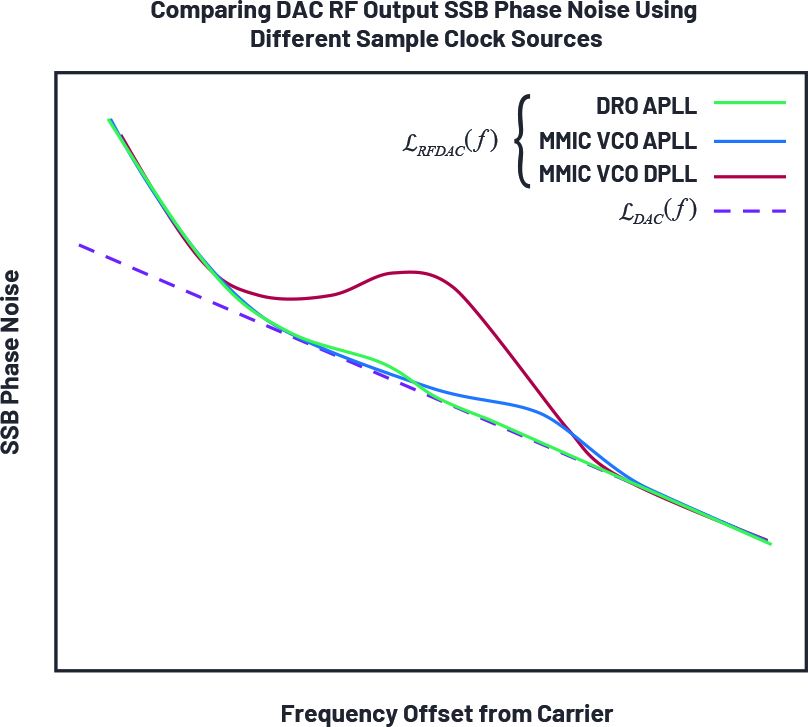

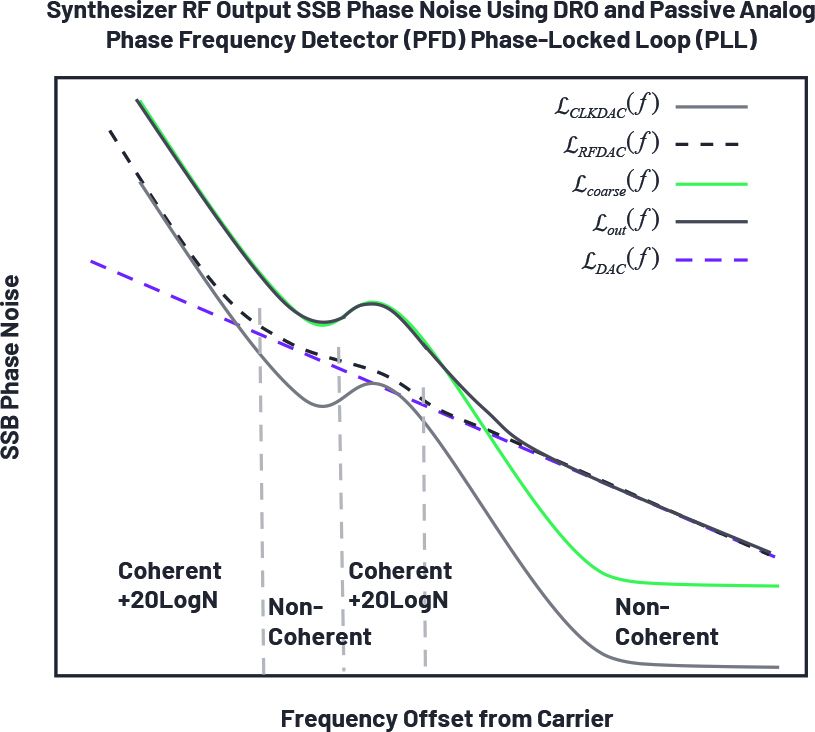

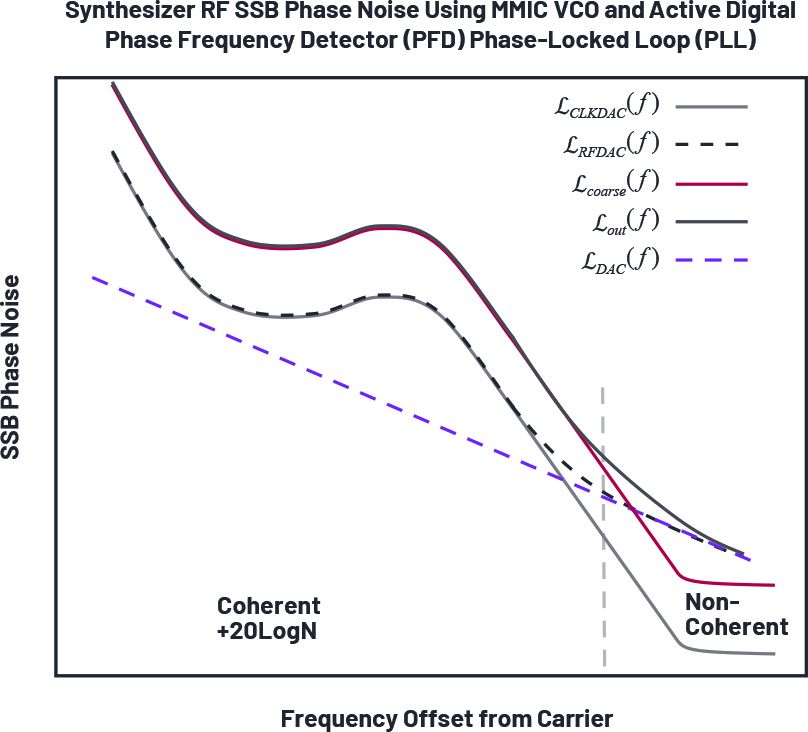

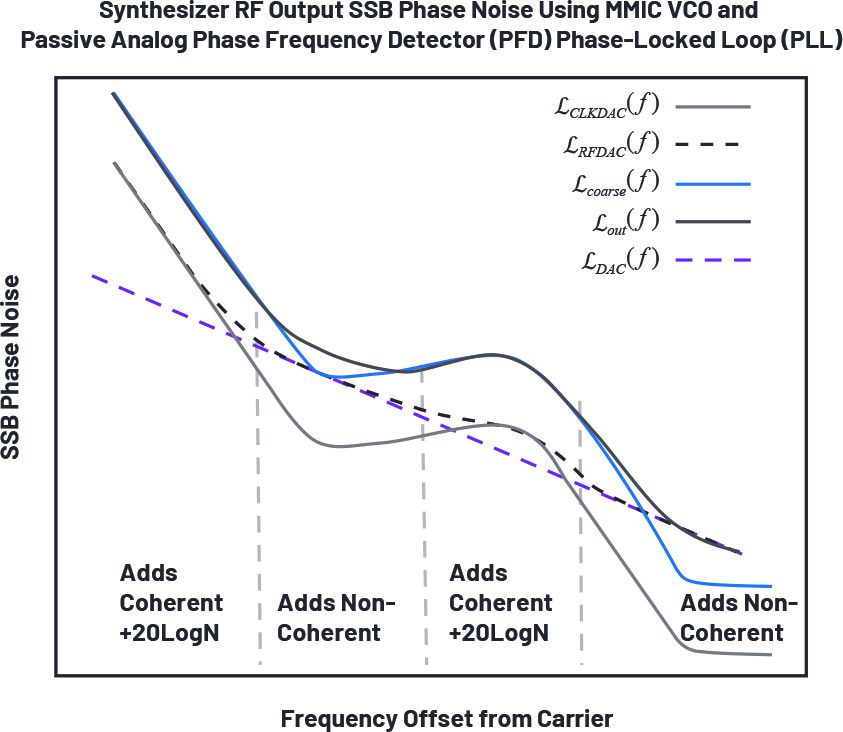

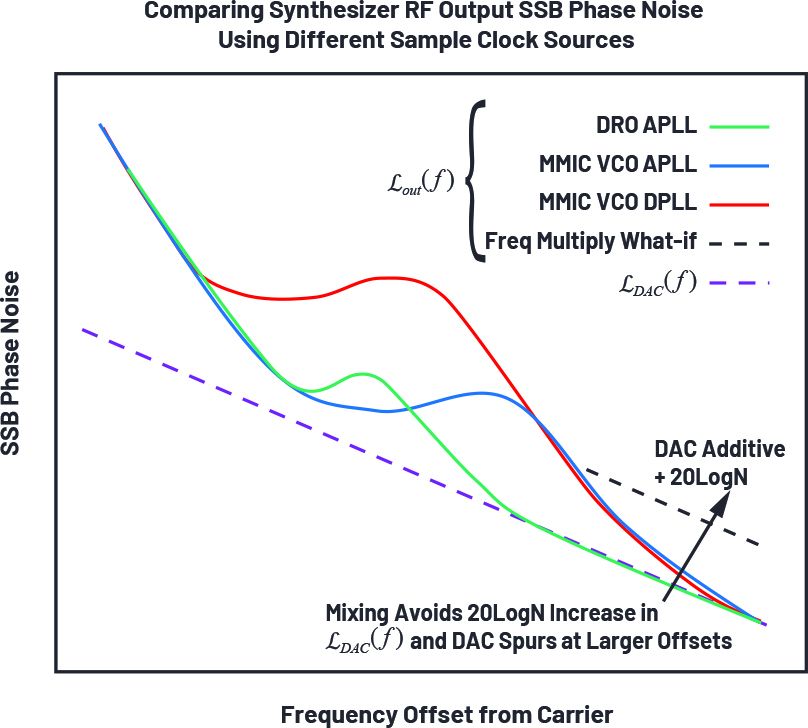

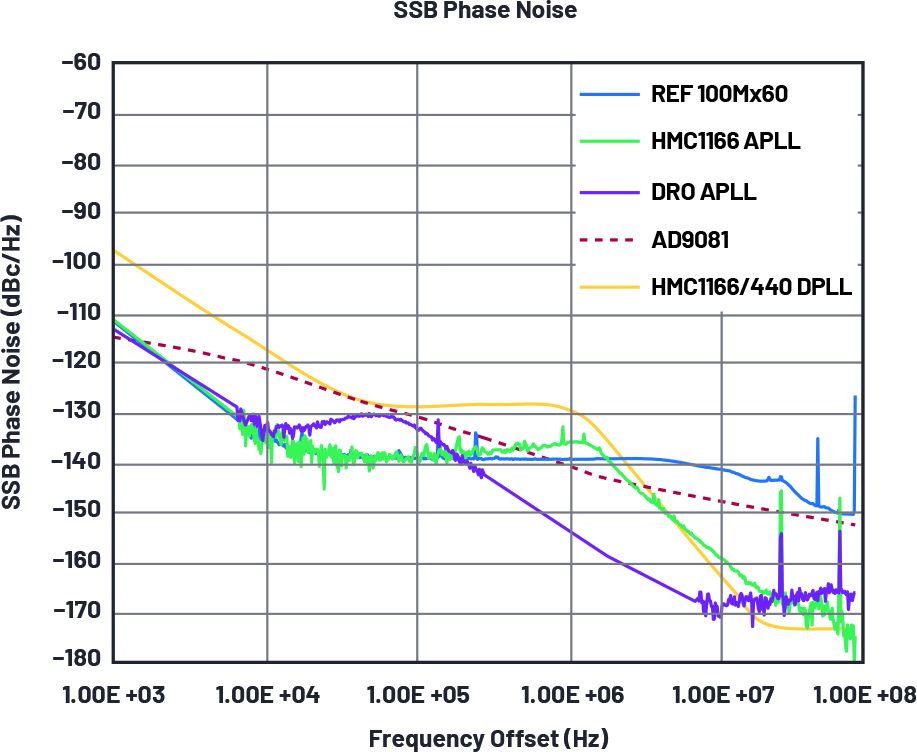

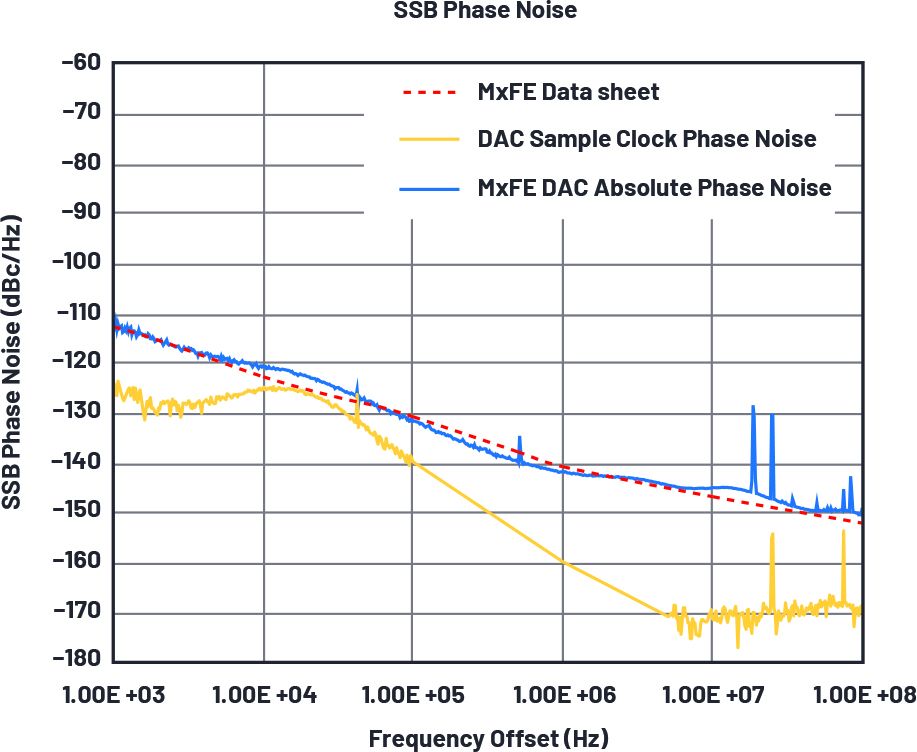

圖7至圖10示出了由此產(chǎn)生的DAC輸出信號(hào)相位噪聲L射頻發(fā)展委員會(huì)(f) 適用于表 1 中概述的三種時(shí)鐘實(shí)現(xiàn)方案。測(cè)得的相位噪聲值如圖18至圖20所示。圖7顯示,高性能DRO RF振蕩器和模擬鎖相環(huán)(DRO APLL)在狹窄區(qū)域內(nèi)推動(dòng)DAC殘余噪聲,但在DAC噪聲之下在很大程度上可以被認(rèn)為是“不可見的”。這提供了比圖8所示的傳統(tǒng)MMIC VCO DPLL采樣時(shí)鐘更好的性能,后者在非常寬的失調(diào)范圍內(nèi)占主導(dǎo)地位,浪費(fèi)了DAC相位噪聲能力,盡管提供了最佳的SWaP-C和易用性。SWaP-C和性能的最佳平衡可能是圖9中的MMIC VCO APLL,它在一段良好的關(guān)鍵失調(diào)范圍內(nèi)保持DAC相位噪聲能力,但由于MMIC VCO相位噪聲低于DRO,因此性能會(huì)降低到較高的失調(diào)。圖10顯示了時(shí)鐘源選項(xiàng)相對(duì)于DAC加性相位噪聲的復(fù)合疊加。

應(yīng)該注意的是,即使在DRO之間,SSB相位噪聲也有很大差異。這里使用的選項(xiàng)是一個(gè)大約大理石大小的小型SWaP-C DRO。存在更高性能的DRO,可以將曲線完全推低到DAC殘余噪聲以下。但是,DRO 相位噪聲電平與 SWaP-C 之間存在直接關(guān)聯(lián),也就是說,該解決方案將比彈珠大得多,僅 DRO 組件就可能要花費(fèi)數(shù)千美元!

圖7.DAC 射頻輸出 SSB 相位噪聲,使用 DRO 鎖定和模擬 PD。

圖8.DAC 射頻輸出 SSB 相位噪聲,使用 MMIC VCO 鎖定,有源 PFD 鎖定。

圖9.DAC射頻輸出SSB相位噪聲使用MMIC VCO鎖定和模擬PD。

圖 10.DAC射頻輸出SSB相位噪聲比較三種方法。

微波合成器實(shí)現(xiàn)

到目前為止,我們已經(jīng)考慮了相對(duì)于DAC加性相位噪聲電位的采樣時(shí)鐘源的實(shí)現(xiàn)選項(xiàng)。現(xiàn)在我們將研究調(diào)諧生成器的實(shí)現(xiàn)。設(shè)計(jì)人員根據(jù)多種DAC和ADC目標(biāo)(包括奈奎斯特區(qū)、瞬時(shí)帶寬和數(shù)據(jù)有效載荷等)選擇數(shù)據(jù)轉(zhuǎn)換器采樣時(shí)鐘頻率。一個(gè)有趣的難題是如何有效地規(guī)劃從可用的采樣時(shí)鐘及其次諧波、N諧波和/N兄弟中生成一組固定音調(diào)的頻率。這些固定音調(diào)是粗頻集,與DAC輸出的精細(xì)頻率集混合。

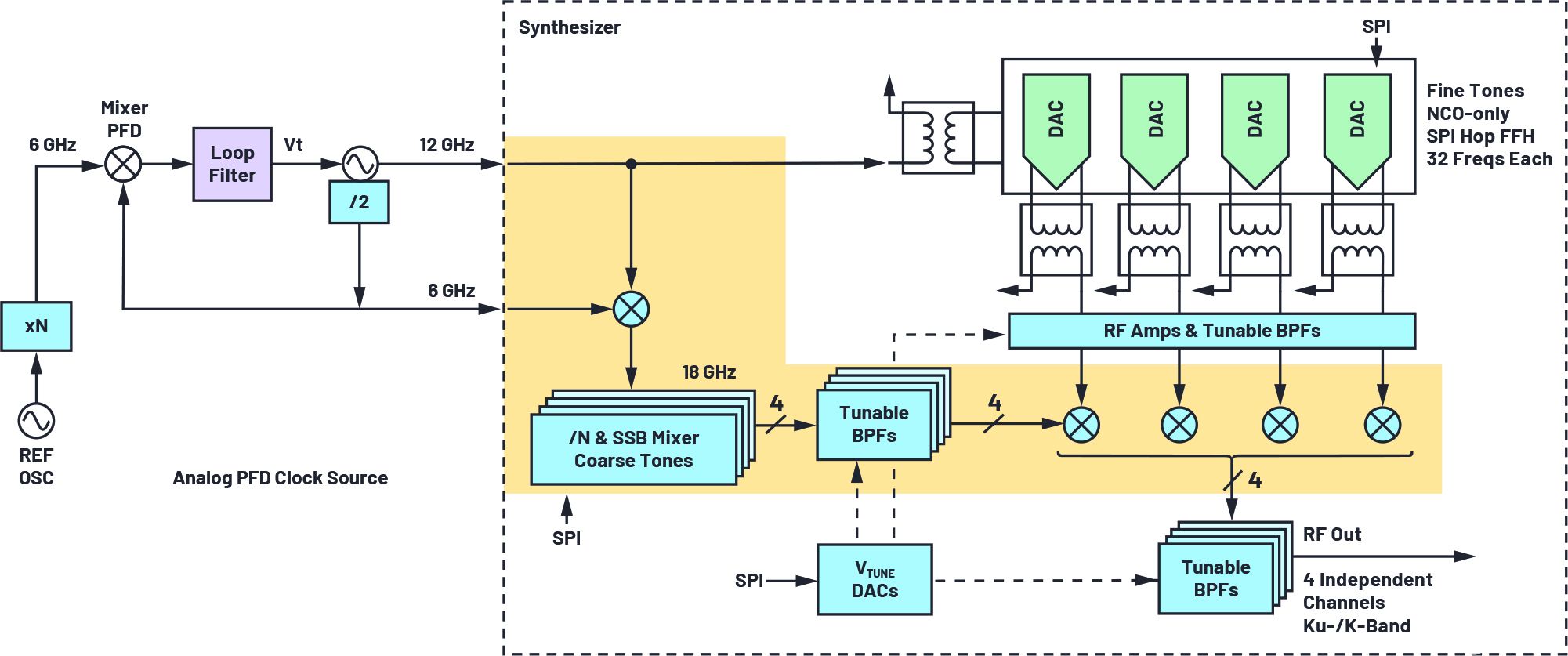

圖11是粗/細(xì)混合方案的框圖。在本例中,我們使用MxFE RF ADC AD9081/AD9082,采樣時(shí)鐘為12 GSPS,來自VCO的VCO,該VCO也以6 GHz輸出RF/2。這些音調(diào)是“免費(fèi)”的,因?yàn)槟枰鼈儊頌镈AC提供時(shí)鐘,因此將粗調(diào)發(fā)生器建立在它們周圍是非常有意義的。結(jié)果表明,將可編程分頻器饋送到單邊帶混頻器方案的18 GHz會(huì)產(chǎn)生一組粗頻率,當(dāng)與DAC輸出混合時(shí),可以覆蓋大多數(shù)Ku和K頻段的合成。可調(diào)諧帶通濾波器對(duì)于衰減許多混頻和DAC雜散至關(guān)重要。精密DAC將SPI控制轉(zhuǎn)換為低噪聲模擬控制信號(hào),調(diào)諧可調(diào)諧濾波器(例如ADV7125)。?

圖 11.推薦使用模擬PD源的基于DAC的粗/細(xì)混頻器合成器。

當(dāng)然,這種混頻方案聽起來有點(diǎn)復(fù)雜,一個(gè)蠻力更簡單的選擇是頻率乘以DAC輸出而不是混頻。倍頻很有吸引力,因?yàn)樗唵吻襍WaP-C更低,因?yàn)閳D11中的橙色突出顯示功能塊被圖12b中的乘法器功能塊取代。倍頻的問題,以及為什么我們?cè)谶@里不認(rèn)真考慮它作為一種選擇,是20LogN DAC本底噪聲和DAC雜散退化。直接RF DAC輸出具有出色的附加相位噪聲和雜散性(通常DAC產(chǎn)生的雜散遠(yuǎn)低于60 dBc)。但是,要將3 GHz至6 GHz DAC RF輸出轉(zhuǎn)換為Ku波段,至少需要乘以4,即DAC雜散和相位噪聲下降12 dB。從任務(wù)的角度來看,這種12 dB的降級(jí)很有可能使DAC雜散和噪聲從合規(guī)變?yōu)椴缓弦?guī)。

圖 12.(a) 性能較低的替代方案:集成數(shù)字PLL采樣時(shí)鐘。(b) 性能較低的替代辦法:乘數(shù)塊。

粗/細(xì)混頻器方法增加的復(fù)雜性值得麻煩,因?yàn)樗苊饬薉AC的倍增,因此DAC雜散和相位噪聲電平以1:1轉(zhuǎn)換為上變頻RF輸出(不增加12 dB!

圖13至圖16說明了粗略和精細(xì)的SSB相位噪聲如何結(jié)合,在所需的上變頻微波頻率下產(chǎn)生最終的SSB相位噪聲。測(cè)量的相位噪聲值稍后如圖18至圖20所示。倍頻與將信號(hào)與自身副本混合相同。同樣,混合不同頻率的相干信號(hào)具有與乘法相同的20LogN相位噪聲影響。換句話說,在圖13至圖16中,在標(biāo)注為“相干”的偏移區(qū)域中,采用混合與乘法方法沒有相位噪聲優(yōu)勢(shì)。在將灰度所示的采樣時(shí)鐘上變頻為更高的LO頻率時(shí),整個(gè)相位噪聲曲線被簡單地向上轉(zhuǎn)換20LogN。粗/細(xì)混音的主要?jiǎng)訖C(jī)是當(dāng)相位噪聲肩接近本底噪聲時(shí),在較大的偏移下獲得的好處。由于在這些偏移處,LO粗音相位噪聲遠(yuǎn)低于DAC加性噪聲水平,因此它基本上沒有任何貢獻(xiàn),您只能看到DAC相位噪聲1:1轉(zhuǎn)換為上變頻微波信號(hào)。圖16比較了每種方法的最終頻率合成器相位噪聲,并注釋了混頻與乘法的遠(yuǎn)失調(diào)優(yōu)勢(shì)。

圖 13.微波合成器SSB相位噪聲使用DRO鎖定與模擬PD。

圖 14.微波合成器SSB相位噪聲使用MMIC VCO鎖定,有源PFD鎖定。

圖 15.微波合成器SSB相位噪聲使用MMIC VCO鎖定與模擬PD。

圖 16.微波合成器SSB相位噪聲比較的三種方法。

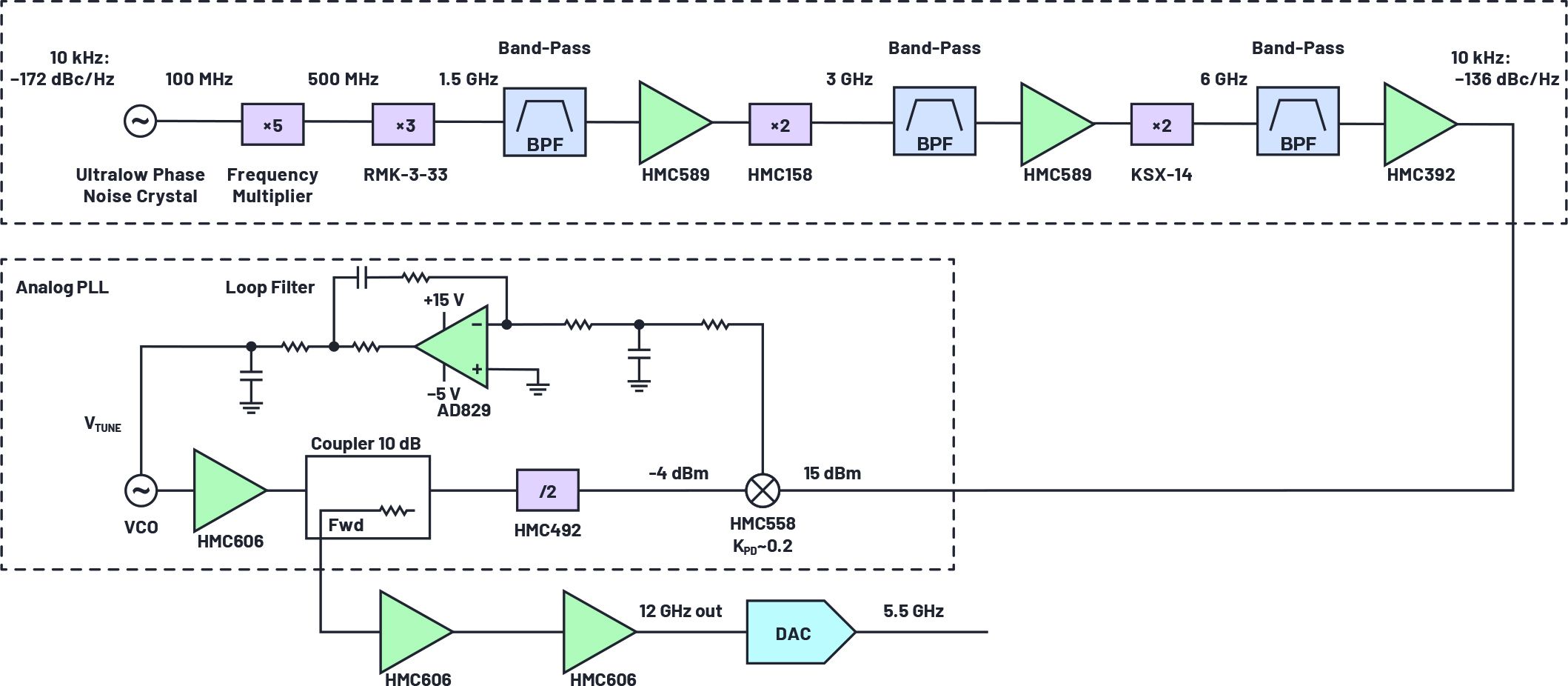

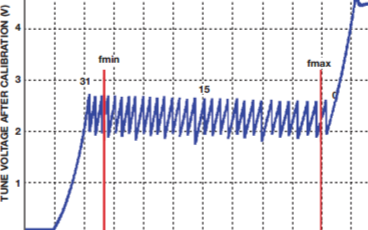

圖17是實(shí)驗(yàn)室中用于獲取圖18所示的SSB相位噪聲的元件鏈。超低噪聲100 MHz晶體振蕩器乘以60。圖18中產(chǎn)生的6 GHz參考相位噪聲的底限為–137 dBc/Hz。作為健全性檢查,將100 MHz晶體本底噪聲加上乘法鏈的加性相位噪聲置于–173 dBc,這是有道理的。基準(zhǔn)電壓源6 GHz信號(hào)饋送HMC558雙平衡混頻器的LO端口,該混頻器用作模擬PD。 (請(qǐng)注意,混頻器的IF端口必須直流耦合。PD 常數(shù) (K帕金森)來計(jì)算運(yùn)算放大器有源濾波器值。這是使用機(jī)械延遲塊和電壓表通過實(shí)驗(yàn)測(cè)量的。實(shí)驗(yàn)設(shè)置在RF振蕩器點(diǎn)測(cè)量了DRO和MMIC VCO(HMC1166)。因?yàn)?KVCO兩者之間有很大不同,需要不同的環(huán)路濾波器值。使用HMC606時(shí),放大器不會(huì)增加殘余相位噪聲。

圖 17.評(píng)估電路。

圖 18.測(cè)量的SSB相位噪聲比較了采樣時(shí)鐘場景、DAC加法和基準(zhǔn)電壓源。所有走線歸一化為測(cè)得的DAC輸出頻率5.5 GHz。

如前所述,根據(jù)–137 dBc/Hz的倍增參考底電平選擇6 GHz作為PD比較頻率。環(huán)內(nèi)相位噪聲將升高20Log10 (12/6 GHz) = 6 dB,表示為N=2。在此參考本底噪聲電平下,相反支路的運(yùn)算放大器、分頻器和放大器殘余噪聲完全低于基準(zhǔn)基準(zhǔn),因此它們不會(huì)產(chǎn)生影響。如果改為選擇3 GHz PD頻率,則參考底值為–143 dBc/Hz(與6 GHz方案相比,改進(jìn)了6 dB)和N=4(與6 GHz情景相比,降低了6 dB),因此參考絕對(duì)相位噪聲對(duì)最終相位噪聲的影響隨著頻率的放大或縮小而受到洗刷。但是,環(huán)內(nèi)分頻器、放大器和運(yùn)算放大器的加性噪聲現(xiàn)在必須有效提高6 dB,才能在3 GHz時(shí)保持無貢獻(xiàn)者。隨著PD頻率的降低,您將達(dá)到這種加性噪聲占主導(dǎo)地位的點(diǎn)。反過來,將PD頻率提高到12 GHz可以消除環(huán)內(nèi)分頻器的附加噪聲(良好),并且可能是可行的。RF放大器的附加噪聲會(huì)隨著頻率的增加而增加,但在12 GHz時(shí)可能很好。 K帕金森需要在 12 GHz 下重新測(cè)量。本文未評(píng)估 12 GHz PD 設(shè)置,但此設(shè)置可能工作正常。

如果在產(chǎn)品中實(shí)現(xiàn),則需要鎖采集電路。這沒有被證明。V調(diào)整需要“預(yù)充電”以將VCO頻率控制得足夠接近基準(zhǔn)電壓源,以便可以捕獲鎖定。

在圖19中,使用帶有模擬PLL和AD829 o的HMC1166測(cè)得的相位噪聲結(jié)果令人印象深刻。P 放大器有源環(huán)路濾波器。使用相同的HMC1166 VCO,我們演示了使用模擬PLL的~15 dB改進(jìn),而基于HMC440的PD采用1 GHz方案則提高了~1 dB。最重要的是,時(shí)鐘主導(dǎo)相位噪聲的失調(diào)被限制在200 kHz至2 MHz,DAC加性相位噪聲的最壞情況降級(jí)為~10 dB。與此形成對(duì)比的是HMC440方案,在HMC440實(shí)現(xiàn)中,時(shí)鐘在20 kHz至2 MHz之間占據(jù)了額外的十倍,DAC加性噪聲的最壞情況會(huì)降低17 dB。在閉合失調(diào)時(shí),VCO APLL跟蹤參考相位噪聲,在中間失調(diào)處有來自環(huán)路濾波器的一點(diǎn)峰化。這個(gè)大約 500 kHz 的區(qū)域可能會(huì)隨著進(jìn)一步的迭代而得到改善。在建模中顯示出有希望的結(jié)果的建議技術(shù)是減少KVCO的VCO。上述方案使用現(xiàn)成的 COTS 組件,并且以低成本相當(dāng)容易演示。

圖 19.使用VCO (HMC1166)使用模擬PLL鎖定測(cè)得的DAC輸出SSB相位噪聲。所有走線歸一化為測(cè)得的DAC輸出頻率5.5 GHz。

真正令人興奮的性能來自圖 20 中的 DRO 場景,盡管 SWaP-C 更高。考慮到DRO APLL的性能,我們幾乎將其降低到足以在DAC相位噪聲下不可見。DAC RF輸出相位噪聲在CLK峰值接近DAC相位噪聲的10 kHz區(qū)域確實(shí)上升了幾dB。環(huán)路帶寬非常窄,以便獲得到極低DRO相位噪聲的最佳轉(zhuǎn)換點(diǎn)。DRO APLL的峰值被懷疑是運(yùn)算放大器噪聲。總體而言,我們認(rèn)為目標(biāo)在幾dB內(nèi)實(shí)現(xiàn),可以推薦使用模擬PLL鎖定的12 GHz DRO,用于需要MxFE器件全相位噪聲能力的最低相位噪聲合成器。

圖 20.使用模擬PLL鎖定的DRO測(cè)量的DAC輸出SSB相位噪聲。所有走線歸一化為測(cè)得的DAC輸出頻率5.5 GHz。其他優(yōu)點(diǎn)。

使用基于 DAC 的混頻器頻率合成器的其他優(yōu)勢(shì)

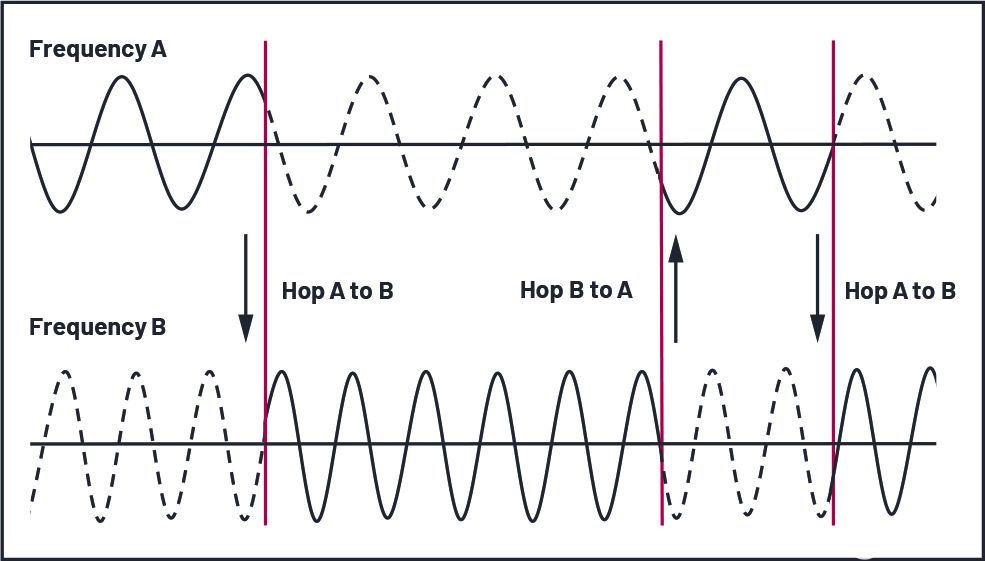

除了相位噪聲優(yōu)勢(shì)外,基于 MxFE DAC 的粗/細(xì)混頻器頻率合成器在僅快速跳頻 (FFH) NCO 模式下能夠?qū)崿F(xiàn) ~300 ns 的捷變跳頻。在32個(gè)獨(dú)立的NCO之間跳頻時(shí),頻率跳相位相干性保持不變,如圖21所示。此外,該合成器不僅限于敏捷音調(diào)生成。DAC提供了通過JESD204B/JESD204C數(shù)據(jù)鏈路實(shí)現(xiàn)任意調(diào)制的靈活性。

圖 21.跳頻相位相干性。

結(jié)論

ADI公司最新一代高速DAC(例如AD9162、AD9164、AD9172、AD9174、AD9081、AD9082)具有出色的相位噪聲,使SWaP-C在下一代低相位噪聲、快速跳頻、捷變RF/微波頻率合成器中具有優(yōu)勢(shì)。固定DAC采樣時(shí)鐘必須具有非常低的SSB相位噪聲,這超出了主流寬帶VCO-PLL的能力。與傳統(tǒng)的基于PFD的有源PLL頻率合成器相比,模擬PD可提供10 dB至20 dB的環(huán)內(nèi)相位噪聲性能改進(jìn)。為了滿足最苛刻的相位噪聲系統(tǒng)要求,建議的固定時(shí)鐘實(shí)現(xiàn)方案是使用模擬PLL鎖定的DRO。提供了基于DAC的粗/細(xì)混頻器頻率合成器示例、測(cè)量的相位噪聲結(jié)果和應(yīng)用電路。

-

ADI

+關(guān)注

關(guān)注

146文章

45859瀏覽量

251217 -

振蕩器

+關(guān)注

關(guān)注

28文章

3845瀏覽量

139266 -

dac

+關(guān)注

關(guān)注

43文章

2309瀏覽量

191367 -

諧振器

+關(guān)注

關(guān)注

4文章

1132瀏覽量

65992

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

低相位噪聲電壓控制振蕩器(VCO)和穩(wěn)定基準(zhǔn)電壓構(gòu)成的頻率合成器

DAC相位噪聲測(cè)量改進(jìn)以支持超低相位噪聲DDS應(yīng)用

用于微波無線電的高性能SiGe PLL與低相位噪聲GaAs VCO配對(duì)

TI推出LMX2581業(yè)界最低相位噪聲的頻率合成器

K波段低相位噪聲頻率綜合器的設(shè)計(jì)與實(shí)現(xiàn)_鄭永華

業(yè)界最低相位噪聲頻率合成器LMX2581的特性優(yōu)勢(shì)是什么

面向 RF 應(yīng)用的低相位噪聲頻率合成器

面向 RF 應(yīng)用的低相位噪聲頻率合成器演示介紹

如何實(shí)現(xiàn)低BER(誤碼率)、低雜散輸出和低相位噪聲的系統(tǒng)級(jí)目標(biāo)

AN-419: 用于完整的直接數(shù)字頻率合成器AD9850的分立、低相位噪聲、125MH晶振

CN-0369:低相位噪聲的轉(zhuǎn)換鎖相環(huán)頻率合成器

ADF4196:低相位噪聲、快速建立、6 GHz PLL頻率合成器數(shù)據(jù)表

ADF4193:低相位噪聲、快速建立PLL頻率合成器數(shù)據(jù)表

改進(jìn)DAC相位噪聲測(cè)量以支持超低相位噪聲DDS應(yīng)用

基于DAC的低相位噪聲頻率合成適用于快速跳頻寬帶微波應(yīng)用

基于DAC的低相位噪聲頻率合成適用于快速跳頻寬帶微波應(yīng)用

評(píng)論