本文介紹在嵌入式系統編程中使用直接內存訪問 (DMA) 的用例、優點和缺點。本文介紹了 DMA 如何與外設和內存模塊交互,以提高 CPU 的運行效率。本文還將向讀者介紹不同的DMA總線接入架構,以及每種架構的優點。

嵌入式系統的一項常見任務是管理外部輸入。管理輸入會給處理器帶來大量不必要的計算壓力,導致處于有功功率模式的時間更長,響應時間變慢。為了優化功耗、保持對事件的快速響應以及管理大型連續數據傳輸,具有直接存儲器訪問 (DMA) 功能的微控制器可以提供最佳解決方案。

直接內存訪問 (DMA)

在涉及外設的系統應用中,微處理器在很多方面都可能成為瓶頸。例如,在管理不斷發送數據的ADC時,處理器可能會經常中斷,以至于難以完成其他任務。DMA 是一種移動數據并最大限度地減少處理器參與大型或快速數據事務的方法。您可以將 DMA 控制器視為一個協處理器,其唯一目的是與內存和外設進行交互。這使得主處理器能夠成功地管理貪婪的外設,專注于另一項任務,甚至在后臺進行數據交易時進入睡眠狀態并節省電力。例如,在 Arm 架構上,DMA 模塊可以在 LP2(睡眠)或 LP3(運行)模式下運行。這在需要延長電池壽命的應用中具有明顯的優勢,例如可穿戴傳感器集線器和智能手表。?

優點和缺點

DMA在許多數字系統中都很有用,有時甚至需要它來管理大量的總線流量。它已被用于網卡,圖形卡,甚至一些原始的IBM PC。話雖如此,將DMA整合到設計中確實有一些權衡。

| 使用 DMA 的優勢 | |

| 中央處理器時間 | DMA 最大限度地減少了對處理器執行和中斷的需求, 減少數據事務所需的 CPU 時間。 |

| 功耗 | 如果 DMA 允許處理器在 DMA 傳輸期間休眠,則使用 DMA 可以產生最小化功耗的機會。 |

| 并行操作 | 根據系統總線的體系結構細節,處理器可能能夠在發生外設事務時執行其他操作。 |

|

使用 DMA 的優勢 |

|

| 成本 | 將系統與 DMA 合并需要 DMA 控制器,這可能會使系統更加昂貴。 |

| 復雜性 | 雖然 DMA 可以降低中斷頻率,但它會增加應用程序固件的大小和復雜性。 |

| 平臺依賴性 | DMA 控制器在制造商之間和制造商內部具有不同的內部架構,并且根據其本機總線訪問方案可能具有不同的行為。 |

| 緩存不連貫性 | DMA 事務可以通過寫入內存層次結構的緩存層而導致邏輯錯誤。這可以通過使用緩存一致的系統體系結構或在 DMA 完成后使緩存存儲失效來解決。 |

總線訪問和 CPU 周期

雖然DMA控制器在節能或加速嵌入式系統方面非常有效,但它們的實現并沒有高度標準化。有多種方案可以確保不會與 CPU 同時授予內部總線訪問。總線訪問方案的目標主要是避免對相同內存位置的并發訪問,這可能導致緩存不一致和邏輯錯誤。單個DMA控制器通常配置為采用這些方案之一,因為使用每種方案可能需要不同的硬件或固件控制。大多數 DMA 控制器使用的總線訪問方案是突發、周期竊取和透明 DMA。

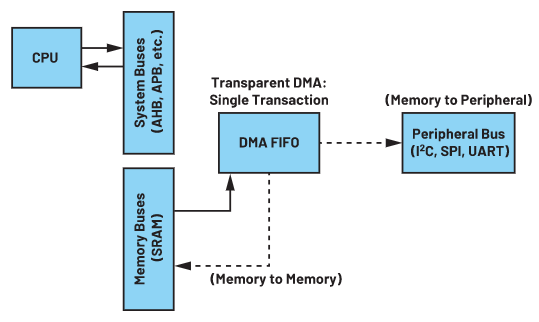

透明 DMA 一次只能執行一個操作,但它還必須等待處理器執行指令,從而訪問所需的數據或地址總線。需要額外的邏輯來驗證此訪問限制,這種類型的 DMA 通常是最慢的。透明 DMA 在需要額外處理且不需要訪問內存總線的應用中可能是有利的。在這種情況下,優點是消除了對CPU的限制,因為處理器不必完全停止運行。

| DMA 的類型 | 優點 | 缺點 |

| 突發 DMA | 最快的 DMA 類型 | CPU 空閑時間相對較長 |

| 周期竊取 DMA | CPU 不會長時間閑置 連續時期 | 比突發 DMA 慢 |

| 透明 DMA | 無需限制 CPU 使用量 | 最慢形式的 DMA |

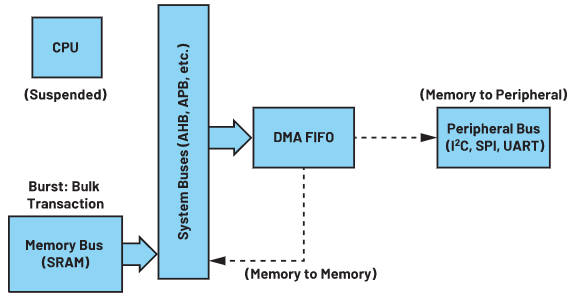

圖1.DMA 操作期間突發 DMA 的體系結構圖。

突發 DMA 通過不頻繁的大突發發生,其中 DMA 控制器向目標緩沖區發送緩沖區可以容納的盡可能多的數據。DMA 控制器在很短的時間內阻止 CPU 操作以移動大量內存,然后將總線讓回主 CPU,重復直到傳輸完成。突發 DMA 通常被認為是最快的類型。

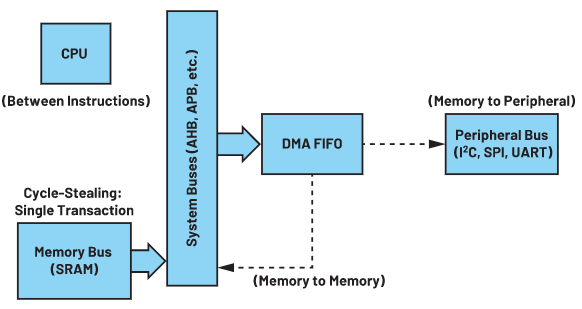

圖2.DMA 操作期間的周期竊取 DMA 發生在兩個 CPU 周期之間。

相反,單字節傳輸或周期竊取 DMA 從 CPU 獲取提示,并且僅在 CPU 指令之間執行操作。它在兩個 CPU 周期之間插入單個操作,因此實際上是在“竊取”CPU 時間。由于一次執行一個操作的限制,它通常比突發 DMA 慢。

圖3.DMA 操作期間的透明 DMA 發生在處理器處理不訪問數據或地址總線的任務時。

突發 DMA 架構示例

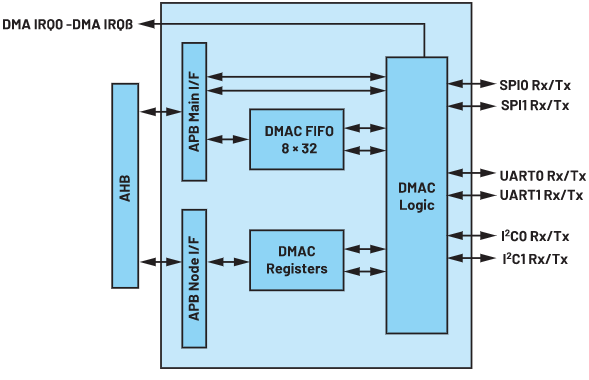

圖4.MAX32660上DMA控制器的結構圖

在MAX32660上可以找到突發DMA控制器的示例(見圖4)。上部路徑對應于數據流,下部路徑表示高級高性能總線 (AHB) 和 DMA 邏輯之間的控制/狀態流。DMA 控制器可以充當 AHB 與內存或外設模塊之間的緩沖接口,具體取決于其配置方式。DMA 邏輯位于 DMA 緩沖區和每個外設之間,用于在事務期間獨立管理每個唯一的外設總線。DMA 操作一次最多可以移動 32 個字節,前提是源/目標緩沖區可以包含這么多數據。緩沖區最多可容納 16 MB,并可配置為發送或接收 I2C, SPI, I2S和UART以及內部存儲器傳輸。DMA 控件的編程可能因協議而異,但外設事務僅由 DMA 控制器管理。仲裁器模塊控制四個 DMA 通道和 CPU 之間的總線訪問限制,根據優先級系統授予請求。

現代 DMA 選項

總之,DMA是現代嵌入式系統的關鍵功能,這些系統管理大量傳感器,需要高吞吐量、高效率和低功耗運行。它的行為類似于專用于內存和外設總線事務的協處理器。

對于許多應用來說,使用 DMA 對于最大限度地降低功耗和減輕處理器負載至關重要。例如,健康和可穿戴設備處理大量數據吞吐量,但它們還必須盡可能多地節省電池電量,同時處理敏感數據。ADI公司在微控制器上提供快速突發DMA架構,這些微控制器非常適合低功耗可穿戴設計,如MAX32660和MAX32670。此外,MAX32666等DARWIN Arm微控制器專為集成藍牙5的可穿戴和物聯網應用而設計。這些器件具有兩個 8 通道突發 DMA 控制器,集成了對基于事件的事務的支持。它們甚至具有一流的安全硬件,帶有安全引導加載程序和信任保護單元 (TPU),用于加速 ECDSA、SHA-2 和 AES 加密。從早期的IBM PC到網卡,再到現在的安全、低功耗可穿戴和物聯網設備,DMA是現代數字系統的基本特征。

審核編輯:郭婷

-

控制器

+關注

關注

112文章

16444瀏覽量

179150 -

cpu

+關注

關注

68文章

10901瀏覽量

212745 -

微處理器

+關注

關注

11文章

2274瀏覽量

82694

發布評論請先 登錄

相關推薦

如何使用DMA加速低功耗可穿戴設備中的外設監控

如何使用DMA加速低功耗可穿戴設備中的外設監控

評論