Altium Designer走差分線出現網格是什么原因?

答:如圖1所示,在AD軟件中走差分線出現網格主要是差分線的未耦合長度沒有滿足差分規則所導致的,未耦合長度指的是差分線中不滿足差分間距的長度。

圖 1 差分走線出現網格走線

當出現這種錯誤時,首先打開規則管理器查看規則所設置的未耦合長度為多少,如圖2所示。因為在走差分時首尾兩端或者在差分線進行打孔換層時是有一段差分線允許不滿足耦合間距的,但這個長度不能過長,推薦設置為50mil,如圖2所示。

圖2 差分耦合長度設置

若檢查規則之后,發現差分線未耦合長度大于所設置的規則值或者差分線中間部分出現網格報錯,此時都需要調整差分線或重新進行差分走線,以滿足差分規則。

投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207Altium Designer 軟件的自定義快捷鍵

Altium Designer創建異形銅皮

AD設置絲印到阻焊的間距,并分析絲印重疊對阻焊的影響

Altium Designer智能粘貼命令的使用教程

Altium Designer智能粘貼命令的使用教程

點擊“閱讀原文”查看更多干貨文章

原文標題:Altium Designer走差分線出現網格是什么原因?

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:Altium Designer走差分線出現網格是什么原因?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

相關推薦

電子發燒友網站提供《Altium Designer15.0軟件設計方法和安裝.pdf》資料免費下載

發表于 01-22 17:22

?0次下載

電子發燒友網站提供《Altium Designer多頁原理圖繪制基礎.pdf》資料免費下載

發表于 01-22 17:11

?1次下載

電子發燒友網站提供《Altium Designer15.0單頁原理圖繪制基礎.pdf》資料免費下載

發表于 01-22 17:09

?0次下載

電子發燒友網站提供《Altium Designer15.0設計環境.pdf》資料免費下載

發表于 01-22 16:56

?0次下載

電子發燒友網站提供《Altium Designer 15.0自定義元件設計.pdf》資料免費下載

發表于 01-21 15:04

?0次下載

關于布局布線DAC5675A器件,由于該器件是高速器件,在PCB方面需要向您請教:

1、差分輸入端差分線長、線距是否有特殊要求?

2、差分時鐘走

發表于 01-14 06:41

數據采集網關出現斷網可能是什么原因?如何排查?

![的頭像]() 發表于

發表于 11-30 13:43

?312次閱讀

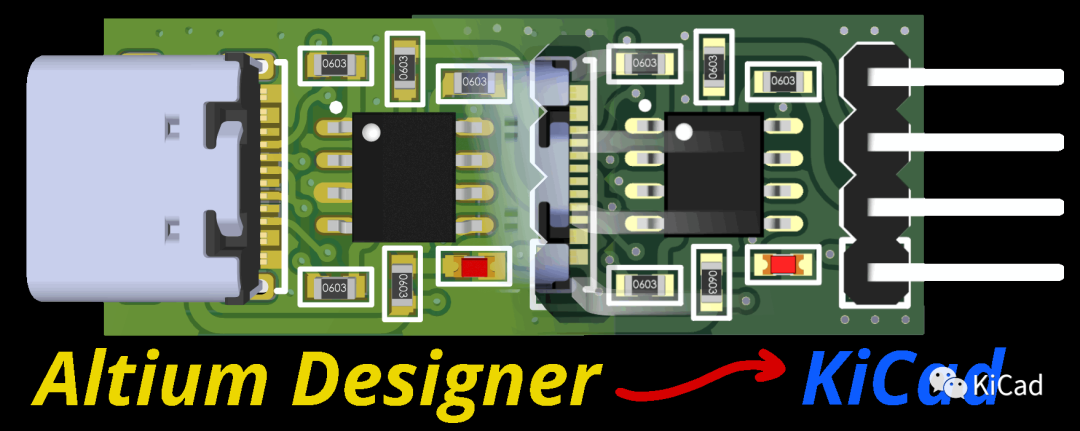

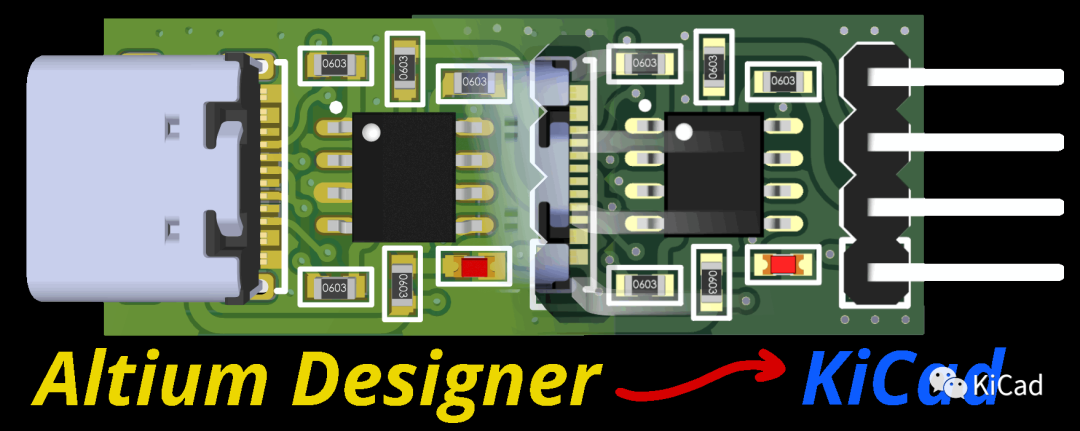

“ ?KiCad可以支持直接導入Altium Designer的原理圖及PCB文件。與其它導入器不同,KiCad導入器可以直接導入源生的二進制文件(*.schdoc及*.pcbdoc),而不需要像

![的頭像]() 發表于

發表于 11-12 12:21

?1504次閱讀

想知道如何在Altium Designer中快速定位器件嘛?

![的頭像]() 發表于

發表于 10-12 09:28

?4246次閱讀

以下是關于Altium Designer原理圖生成方法的步驟: 準備工作 在開始繪制原理圖之前,需要進行一些準備工作,包括: 1.1 安裝Altium Designer軟件:首先,確保

![的頭像]() 發表于

發表于 09-02 16:25

?941次閱讀

Altium Designer 24.7.2 發布時間:2024年7月23日 Altium Designer 24.7.2?離線包 15天免費試用

![的頭像]() 發表于

發表于 08-05 14:58

?2702次閱讀

Altium-Designer-16-自帶元件庫

發表于 07-22 12:01

?1次下載

電子發燒友網站提供《Altium Designer 6.0初學教程.pdf》資料免費下載

發表于 07-12 11:47

?0次下載

電子發燒友網站提供《高速差分線路接收器數據表.pdf》資料免費下載

發表于 06-26 10:52

?0次下載

隨著信息技術的飛速發展,高速信號傳輸已成為現代通信和數據處理中不可或缺的一環。在高速信號傳輸中,差分線技術因其獨特的優勢而得到廣泛應用。本文將從差分線的基本原理、抗干擾能力、帶寬容量、

![的頭像]() 發表于

發表于 05-16 16:31

?904次閱讀

Altium Designer走差分線出現網格是什么原因?

Altium Designer走差分線出現網格是什么原因?

評論