作者:趙歡 ,朱 倩 ,唐 衡

引 言

隨著 FPGA 數(shù)字信號(hào)處理系統(tǒng)復(fù)雜度不斷提高,F(xiàn)PGA 信號(hào)處理系統(tǒng)的功能驗(yàn)證已經(jīng)成為影響產(chǎn)品上市時(shí)間和成本的關(guān)鍵[1]。盡管在驗(yàn)證領(lǐng)域已經(jīng)發(fā)展出多種自動(dòng)測(cè)試方法,但是針對(duì)信號(hào)處理算法進(jìn)行驗(yàn)證時(shí),仍然需要手動(dòng)編寫代碼搭建仿真平臺(tái)[2],生成仿真激勵(lì),效率較低。信號(hào)處理系統(tǒng)往往包含大量復(fù)雜的算法[3],對(duì)于驗(yàn)證人員編寫代碼的經(jīng)驗(yàn)及技能要求較高。

針對(duì)這一情況,本文提出了一種基于 Simulink 與IES 聯(lián)合搭建的功能驗(yàn)證平臺(tái)。使用 Simulink 的 HDLCoder自動(dòng)生成代碼完成仿真平臺(tái)中的信號(hào)處理算法部分。首先,利用 Matlab強(qiáng)大的分析、計(jì)算和可視化功能,使用 Simulink 對(duì)算法進(jìn)行建模仿真[4],當(dāng)仿真結(jié)果達(dá)到設(shè)計(jì)要求后,再使用該模型直接生成 HDL 代碼[5],從而大幅提高了驗(yàn)證平臺(tái)開發(fā)效率,避免了對(duì)復(fù)雜信號(hào)處理驗(yàn)證模型的硬件語言設(shè)計(jì),提升了平臺(tái)的復(fù)用性和仿真平臺(tái)搭建效率。同時(shí),由于無需手動(dòng)編寫代碼,也避免了人為引入的錯(cuò)誤,提升了驗(yàn)證平臺(tái)的可靠性。

1 SMA 基帶信號(hào)處理

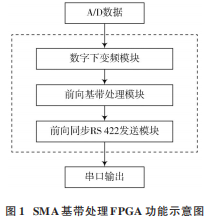

本文驗(yàn)證的SMA基帶信號(hào)處理FPGA,是SMA(S?BandMultiple Address)測(cè)控終端系統(tǒng)的重要組成部分[6],主要完成前向鏈路中的中頻信號(hào)解調(diào)、解擴(kuò),將解調(diào)結(jié)果通過 RS 422 接口輸出至管理單元。該 FPGA 的主要功能

模塊包括:

1)數(shù)字下變頻模塊:輸入 A/D 信號(hào)的采樣,將輸入中頻信號(hào)下變頻到基帶。

2)前向基帶處理模塊:生成解調(diào)所需的 GOLD 碼;實(shí)現(xiàn)頻率捕獲和偽碼捕獲;在捕獲的基礎(chǔ)上實(shí)現(xiàn)信號(hào)跟蹤并對(duì)相關(guān)積分結(jié)果進(jìn)行自動(dòng)增益控制;解擴(kuò)和位同步。

3)前向同步 RS 422 發(fā)送模塊:通過 RS 422 接口輸出解調(diào)數(shù)據(jù)。功能示意圖如圖 1所示。

2 聯(lián)合仿真平臺(tái)

2.1 驗(yàn)證平臺(tái)概述

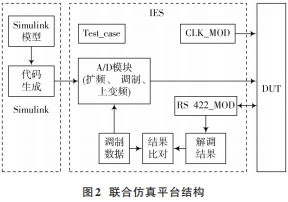

本平臺(tái)主要用于驗(yàn)證 SMA 信號(hào)處理 FPGA 的解調(diào)功能和算法性能,確認(rèn)該 FPGA 是否能夠正確解調(diào)規(guī)定調(diào)制格式的輸入信號(hào),并確認(rèn)是否滿足接收載噪比、捕獲時(shí)間、捕獲頻偏范圍、跟蹤多普勒變化率等性能要求。本平臺(tái)采用 IES 和 Simulink 聯(lián)合的仿真方法,在被測(cè)設(shè)計(jì)外圍搭建基于 System Verilog 和 Verilog 混合編程的仿真平臺(tái)。使用 Simulink 搭建信號(hào)處理模型,使用System Verilog搭建其他外圍接口模型。主要包括:

1)使用 Simulink 搭建信號(hào)處理模型,將調(diào)制數(shù)據(jù)進(jìn)行擴(kuò)頻、調(diào)制、成型濾波、上變頻后通過 A/D 接口輸入至 DUT,然后自動(dòng)生成 Verilog代碼用于仿真。

2)RS 422 接口模型,使用 System Verilog 搭建,接收 DUT 輸出的解調(diào)數(shù)據(jù)并發(fā)送至 scoreboard 用于數(shù)據(jù)比對(duì)。

3)時(shí)鐘模型,使用 System Verilog 搭建,為測(cè)試環(huán)境和 DUT提供工作時(shí)鐘。

4)數(shù)據(jù)比對(duì)模塊,基于System Verilog的scoreboard,自動(dòng)比對(duì)測(cè)試環(huán)境發(fā)送的調(diào)制數(shù)據(jù)和 DUT 輸出的解調(diào)結(jié)果,測(cè)試是否存在誤碼。

5)Test_case,用例控制模塊,使用 System Verilog 生成不同的Test_case 以驗(yàn)證被測(cè)設(shè)計(jì)在不同輸入條件下是否滿足算法性能要求。

除了驗(yàn)證解調(diào)數(shù)據(jù)正確性以外,在 Simulink 中搭建信號(hào)處理模型時(shí),將上變頻模塊的載波頻率和碼NCO的碼速率控制字設(shè)置為外部輸入可控,通過 Test_case靈活控制不同用例,測(cè)試 DUT 在不同輸入載波頻率下的捕獲和跟蹤性能是否滿足要求。聯(lián)合仿真平臺(tái)如圖2所示。

2.2 Simulink信號(hào)源建模

根據(jù)對(duì)被測(cè)設(shè)計(jì)的分析,A/D 信號(hào)源模塊的主要技術(shù)指標(biāo)包括:A/D 接口輸入信號(hào)位寬為 12 bits,A/D 采樣頻率為 100 MHz。擴(kuò)頻模式為直接序列擴(kuò)頻模式,擴(kuò)頻碼為 GOLD 碼,碼長為 1 023,碼速率為 3.069 Mc/s,G1生 成 多 項(xiàng) 式 為 x10 + x8 + x7 + x4 + x2 + x + 1 ,初 相 為1101111100,G2 生 成 多 項(xiàng) 式 為 x10 + x7 + 1 ,初 相 為1001001000。需要對(duì)擴(kuò)頻后的序列進(jìn)行成型濾波,濾波器選擇成型系數(shù)為 0.6的平方根升余弦濾波器。應(yīng)將濾波后的信號(hào)調(diào)制至中頻,中頻為 30 MHz,并且為了驗(yàn)證性能需求,載波多普勒、碼多普勒、載噪比需要根據(jù)用例要求靈活控制。

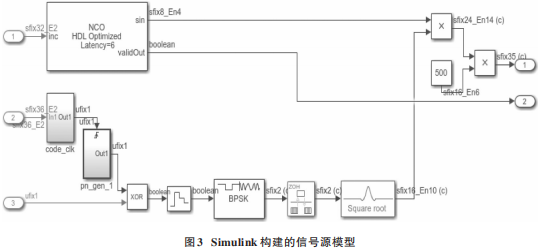

依據(jù)上述要求,設(shè)計(jì)了 A/D 信號(hào)源模型如圖 3 所示,整個(gè)模型由擴(kuò)頻碼時(shí)鐘模塊、GOLD 碼發(fā)生器模塊、BPSK 調(diào)制模塊、成型濾波器模塊和上變頻模塊構(gòu)成。

1)擴(kuò)頻碼時(shí)鐘模塊 code_clk:擴(kuò)頻碼時(shí)鐘模塊使用NCO 模型產(chǎn)生正弦波輸出,然后使用比較器將正弦波轉(zhuǎn)換成方波,作為 GOLD 碼發(fā)生器模塊的 Trigger 信號(hào)。為了能夠根據(jù)用例設(shè)置靈活控制碼鐘頻率,將 NCO 頻率控制字設(shè)置為外部輸入模式(Input Port)。

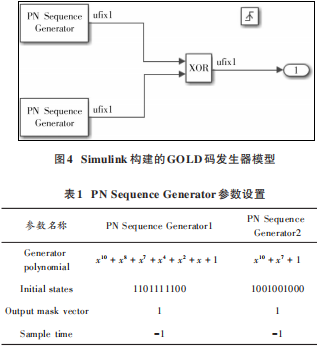

2)GOLD 碼發(fā)生器模塊 pn_gen_1:GOLD 碼發(fā)生器模 塊 由 2 個(gè) PN Sequence Generator 構(gòu) 成 ,將 2 個(gè) PNSequence Generator 的輸出異或后得到 GOLD 碼[7],模型結(jié)構(gòu)如圖 4 所示,2 個(gè) PN Sequence Generator 的參數(shù)設(shè)置見表 1。

3)BPSK 調(diào)制模塊:使用 BPSK 模型對(duì)擴(kuò)頻后的結(jié)果進(jìn)行 BPSK 調(diào)制。

4)成型濾波器模塊:成型濾波器模塊用于消除碼間串?dāng)_,本文中使用 Raised Cosine Transmit Filte模型實(shí)現(xiàn),設(shè)置濾波器類型為平方根升余弦濾波器,滾降系數(shù)為 0.6。

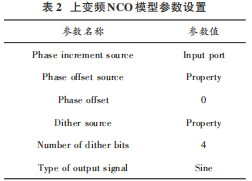

5)上變頻模塊:上變頻模塊使用 NCO HDL模型實(shí)現(xiàn),為了能夠根據(jù)用例設(shè)置靈活控制載波頻率,將載波NCO 頻率控制字設(shè)置為外部輸入模式(Input Port),其他參數(shù)設(shè)置見表2。設(shè)置載波 NCO 輸入頻率為90 kHz~30 MHz時(shí),該 NCO 輸出信號(hào)的頻譜如圖 5所示。

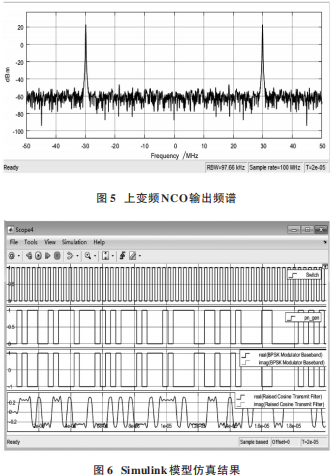

信號(hào)源模型仿真結(jié)果如圖 6 所示,圖中信號(hào)波形從上到下分別為:擴(kuò)頻碼時(shí)鐘、擴(kuò)頻碼序列、BPSK 調(diào)制輸出、成型濾波器輸出。

需要注意的是:為了能夠自動(dòng)生成代碼,構(gòu)建仿真模型必須使用 hdllib 內(nèi)的模型,hdllib 是支持生成 HDL代碼的模型庫[8],并且需要將模型的輸入設(shè)置為定點(diǎn)輸入,這樣模型自動(dòng)成為定點(diǎn)模型,生成代碼時(shí)即生成定點(diǎn)代碼[9?10]。

2.3 Simulink模型的 HDL代碼直接生成

搭建 Simulink 模型并完成仿真后,就可以直接在HDL Coder中生成 HDL 代碼[11]。Simulink 使用高層次綜合合成技術(shù),將硬件可實(shí)現(xiàn)的 Simulink 模型編譯為可讀、可追溯且可模型化的 VHDL 或 Verilog HDL 代碼,此代碼經(jīng)過優(yōu)化可以跨任意 FPGA、ASIC 或 SoC 硬件進(jìn)行移植[12?13]。代碼生成的過程如下:

1)將需要生成代碼的部分封裝為一個(gè)子系統(tǒng)。

2)檢查模型是否可綜合:選中子系統(tǒng)后右鍵選擇HDL Code→check subsystem compatibility,如果檢查通過,可繼續(xù)生成代碼;如果失敗,則需要進(jìn)行模塊替換。

3)參數(shù)設(shè)置,可以設(shè)置生成的語言類型、復(fù)位信號(hào)極性等。

4)設(shè)置完成后,右鍵點(diǎn)擊需要生成的子系統(tǒng),選擇HDL CODE→Generate HDL for subsystem,最 終 生 成代碼。

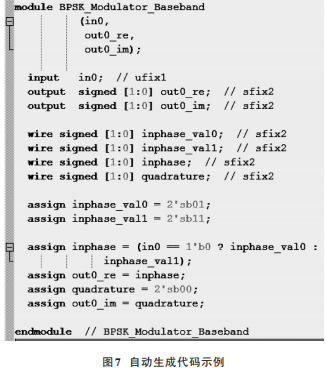

其中一個(gè)自動(dòng)生成模塊——BPSK 調(diào)制模塊代碼如圖 7 所示,可以看出最終生成代碼有較好的可讀性,便于仿真調(diào)試和修改。

3 仿真結(jié)果與分析

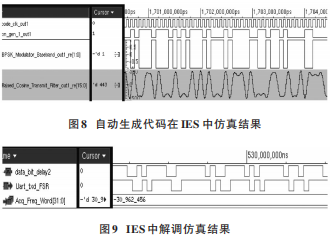

以載噪比 Eb N0=10 dB、初始多普勒偏差 90 kHz、多普勒變化率 1 kHz/s的測(cè)試用例為例,IES仿真結(jié)果如圖 8和圖 9所示。

圖 8 中,仿真波形從上到下依次為碼發(fā)生器時(shí)鐘、擴(kuò)頻碼時(shí)鐘、擴(kuò)頻碼序列、BPSK調(diào)制輸出、成型濾波器輸出。圖 9 中,data_bit_delay2 是仿真平臺(tái)發(fā)送的調(diào)制數(shù)據(jù),Uart_txd_FSR 是 DUT 輸出的解調(diào)數(shù)據(jù),通過比對(duì)可 以 確 認(rèn) ,輸 出 解 調(diào) 數(shù) 據(jù) 與 發(fā) 送 的 調(diào) 制 數(shù) 據(jù) 一 致。Acq_Freq_Word為捕獲得到的載波頻率,被測(cè) FPGA 內(nèi)部 NCO 時(shí)鐘為 12.5 MHz,計(jì)算可得捕獲得到的頻率為( -30 962 456 × 12.5 × 106) 232 =-90.112 Hz。

綜上可以確認(rèn)被測(cè)FPGA能夠在載噪比Eb N0=10 dB、初始多普勒偏差-90 kHz 時(shí)成功捕獲,并且跟蹤、解擴(kuò)、解調(diào)數(shù)據(jù),驗(yàn)證了設(shè)計(jì)功能的正確性和性能指標(biāo)。

4 結(jié) 語

本文提出了一種基于 Simulink與 IES聯(lián)合搭建的功能驗(yàn)證平臺(tái),給出了聯(lián)合仿真實(shí)例,成功對(duì) SMA 信號(hào)處理 FPGA 進(jìn)行了功能和性能驗(yàn)證。該仿真平臺(tái)利用了Matlab 豐富的信號(hào)處理算法模型,生成了驗(yàn)證平臺(tái)中的關(guān)鍵算法模塊代碼,極大地降低了驗(yàn)證平臺(tái)的開發(fā)難度,提升了仿真平臺(tái)的開發(fā)效率,提高了平臺(tái)的復(fù)用性。同時(shí),避免了手動(dòng)編寫代碼而引入的錯(cuò)誤,提升了環(huán)境的可靠性,對(duì)其他類似復(fù)雜信號(hào)處理類 FPGA 設(shè)計(jì)的驗(yàn)證具有極大的參考價(jià)值。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603608 -

代碼

+關(guān)注

關(guān)注

30文章

4790瀏覽量

68649

原文標(biāo)題:論文速覽 | 基于Simulink代碼生成的 FPGA 信號(hào)處理系統(tǒng)仿真驗(yàn)證平臺(tái)

文章出處:【微信號(hào):現(xiàn)代電子技術(shù),微信公眾號(hào):現(xiàn)代電子技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Simulink與 Simscape的結(jié)合使用

Simulink與 MATLAB 的結(jié)合使用 Simulink中的信號(hào)處理方法

Simulink模型仿真與分析技巧

Matlab/Simulink/Stateflow建模開發(fā)及仿真測(cè)試

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大規(guī)模電力電子系統(tǒng)仿真

解決方案丨EasyGo新能源系統(tǒng)實(shí)時(shí)仿真應(yīng)用

新的 MathWorks 硬件支持包支持從 MATLAB 和 Simulink 模型到高通 Hexagon 神經(jīng)處理單元架構(gòu)的自動(dòng)化代碼生成

EasyGo實(shí)時(shí)仿真丨PCS儲(chǔ)能變流器控制仿真應(yīng)用

信號(hào)采集與處理系統(tǒng)通常由哪些模塊組成

EasyGo使用筆記丨分布式光伏集群并網(wǎng)控制硬件在環(huán)仿真應(yīng)用

基于MATLAB的信號(hào)處理系統(tǒng)與分析

Vivado 使用Simulink設(shè)計(jì)FIR濾波器

Simulink自動(dòng)生成代碼現(xiàn)階段的學(xué)習(xí)筆記

基于Simulink代碼生成的FPGA信號(hào)處理系統(tǒng)仿真驗(yàn)證平臺(tái)

基于Simulink代碼生成的FPGA信號(hào)處理系統(tǒng)仿真驗(yàn)證平臺(tái)

評(píng)論