本文來源電子發燒友社區,作者:李先生, 帖子地址:https://bbs.elecfans.com/jishu_2308801_1_1.html

前言

過程

總結

總結

前言

簡單起見,本次基于WSL和Ubuntu安裝交叉編譯工具。并未使用VMWARE加載鏡像。

WSL安裝UBUNTU過程可以搜搜網上資料,不再贅述。

打開WSL終端

下載代碼

git clonehttps://github.com/eembc/coremark.git

cd coremark/

vi simple/core_portme.h

修改

#define COMPILER_FLAGS

FLAGS_STR /* "Please put compiler flags here (e.g. -o3)" */

#endif

為

#define COMPILER_FLAGS

"-O3" /* "Please put compiler flags here (e.g. -o3)" */

#endif

如果-O0編譯則改為”-O0”

typedef ee_u32 ee_ptr_int;

改為

typedef unsigned long ee_ptr_int;

編譯

arm-linux-gnueabihf-gcc -o coremarko0core_list_join.c core_main.c core_matrix.c core_state.c core_util.c simple/core_portme.c -DPERFORMANCE_RUN=1 -DITERATIONS=100000 -Isimple -I. -O0

arm-linux-gnueabihf-gcc -o coremarko3core_list_join.c core_main.c core_matrix.c core_state.c core_util.c simple/core_portme.c -DPERFORMANCE_RUN=1 -DITERATIONS=100000 -Isimple -I. -O3

導入到windows下

cp coremarko0 coremarko3 /mnt/d

然后通過串口rz導入到開發板

添加可執行權限

chmod +x coremarko0 coremarko3

運行

./coremarko0

./coremarko3

結果如下,可以看到優化不同差距較大

[root@EASY-EAI-NANO:/]# ./coremarko0

CoreMark Size : 666

Total ticks : 117300564

Total time (secs): 117.300564

Iterations/Sec : 852.510820

Iterations : 100000

Compiler version : GCC9.4.0

Compiler flags : -O0

Memory location: STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xd340

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 852.510820 / GCC9.4.0 -O0 / STACK

[root@EASY-EAI-NANO:/]# ./coremarko3

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 23419440

Total time (secs): 23.419440

Iterations/Sec : 4269.956925

Iterations : 100000

Compiler version : GCC9.4.0

Compiler flags : -O0

Memory location: STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xd340

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 4269.956925 / GCC9.4.0 -O0 / STACK

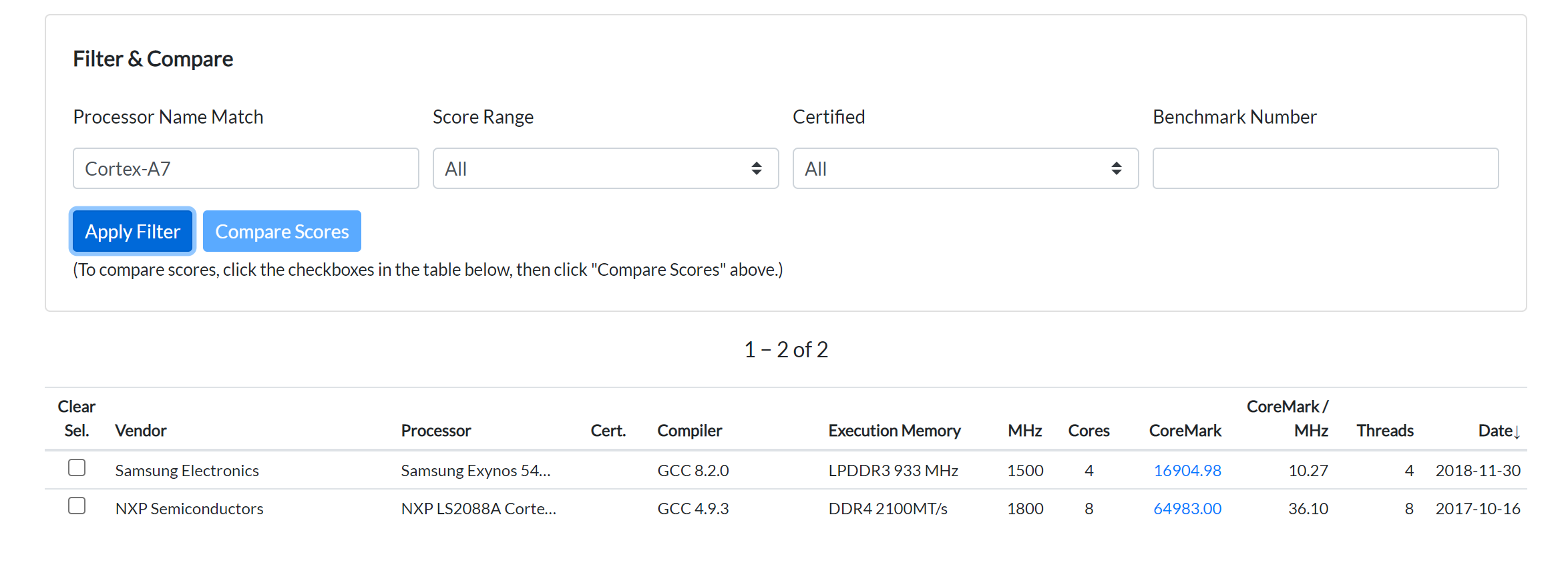

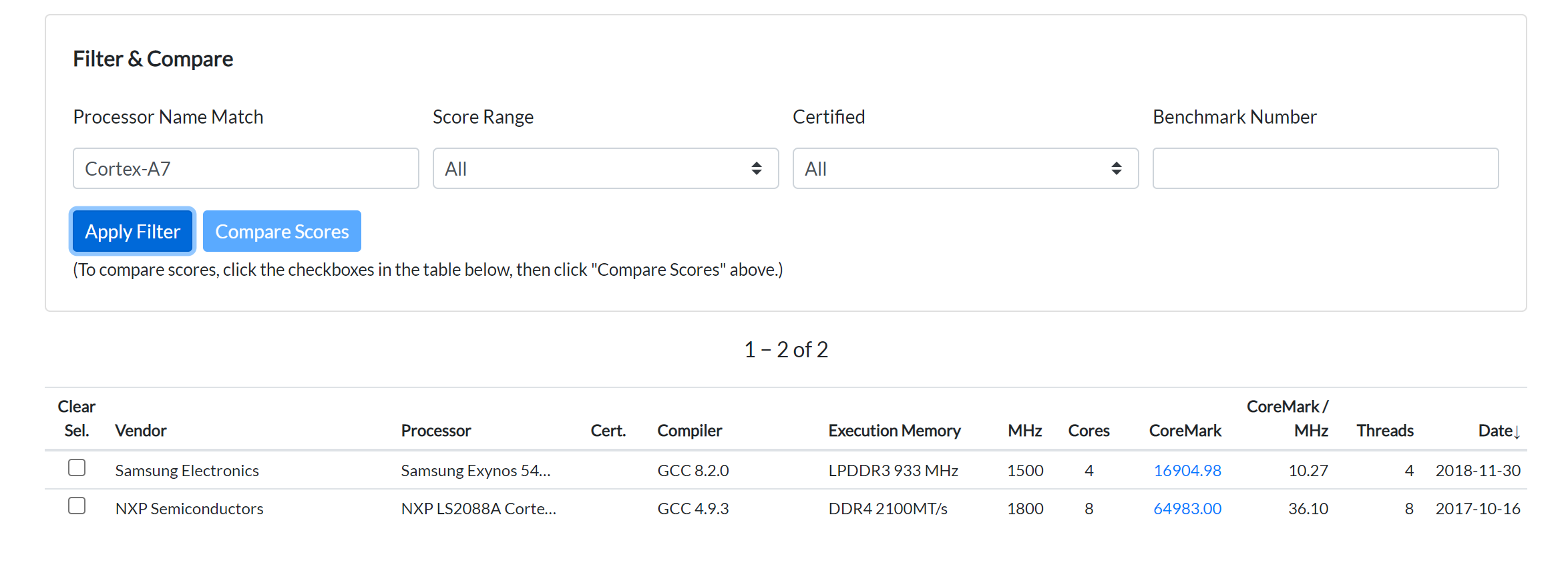

從https://www.eembc.org/coremark/scores.php

搜索Cortex-A7可以對比同型號CPU的得分。

Cortex-A7 1.5GHz 4核

4269.956925x4=17,079.8277和三星的Samsung Exynos 542216904.98配置差不多得分高一點。

說明CPU本身性能達到了一線水準。

快速體驗了C開發,進行了跑分測試,跑分比同配置的Samsung Exynos 5422還要高一點,說明CPU本身性能達到了一線水準。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

靈眸

+關注

關注

0文章

19瀏覽量

3237 -

開發板試用

+關注

關注

3文章

301瀏覽量

2194

發布評論請先 登錄

相關推薦

三星電子1c nm內存開發良率里程碑推遲

據韓媒報道,三星電子已將其1c nm DRAM內存開發的良率里程碑時間推遲了半年。原本,三星計劃在2024年底將1c nm制程DRAM的良率

三星1c nm DRAM開發良率里程碑延期

據韓媒MoneyToday報道,三星電子已將其1c nm(1-cyano nanometer)DRAM內存開發的良率里程碑時間從原定的2024年底推遲至2025年6月。這一變動可能對三星

NVIDIA發布小巧高性價比的Jetson Orin Nano Super開發者套件

NVIDIA近期推出了一款全新的生成式AI超級計算機——Jetson Orin Nano Super開發者套件。這款開發者套件以其小巧的尺寸

是德科技助力三星電子驗證FiRa 2.0安全測距測試用例

是德科技(Keysight Technologies,Inc.)成功助力三星電子,在其Exynos Connect U100芯片組上驗證了FiRa 2.0安全測試用例。此次驗證得益于是德科技提供的超寬帶 (UWB)測試解決方案,該方案符合物理層一致性測試的各項要求。

潤和軟件星閃派物聯網開發套件資料+答疑帖

星閃派物聯網開發套件具有豐富的通信接口、開放性、模塊化、集成化等多個亮點;可基于星閃派物聯網開發套件開發實現設備的遠程監控和控制、數據的實時

發表于 09-29 10:24

【新品上線】星閃派物聯網開發套件免費試用

星閃派物聯網開發套件具有豐富的通信接口、開放性、模塊化、集成化等多個亮點;可基于星閃派物聯網開發套件開發實現設備的遠程監控和控制、數據的實時

發表于 08-16 09:34

三星高通聯手開發XR芯片,劍指蘋果市場

三星電子與高通公司攜手,共同推進XR(擴展現實)技術的邊界,宣布將開發專用于XR設備的高性能芯片。這一戰略舉措標志著三星在XR市場邁出了重要一步,同時也預示著與蘋果在該領域的競爭將進一

【xG24 Matter開發套件試用體驗】1-基本情況介紹

)。

說是開發套件其實就是一塊開發板,好在開發板帶板載 SEGGER J-Link 調試器,功能接口已經包含,其余接口也都引出到端子上,方便使用。

實物如圖:

USB接口是TYPE-C

發表于 07-17 12:39

LitePoint與三星電子合作支持FiRa 2.0物理層安全測距測試用例

先進無線測試解決方案提供商LitePoint與三星電子宣布緊密合作,支持FiRa 2.0物理層(PHY)一致性測試規范內定義的新安全測試用例。

三星將于2026年終止與超微合作

近日,有消息稱三星電子與超微(AMD)在高帶寬存儲器(HBM)等領域的合作正隨著AI半導體市場的蓬勃發展而日益深化。然而,業界也傳出新的動向,據臺灣電子時報報道,三星計劃在2026年邁出重要一步,即

三星電子采納新思科技Synopsys.ai EDA套件,完成GAA制程驗證

據新思科技介紹,他們的 Synopsys.ai EDA 套件專為 CPU 高效運行而設計,為三星的 GAA 節點帶來了卓越的 PPA(性能、功耗和面積)表現。

三星研發CXL混合存儲模組,實現閃存與CPU數據直傳

據三星展示的圖片顯示,此模組可以通過CXL接口在閃存部分及CPU之間進行I/O塊傳輸,也可以運用DRAM緩存和CXL接口達到64字節的內存I/O傳輸。

【LicheeRV-Nano開發套件試用體驗】基礎開發環境

一、開發環境分類

注意,雖然是開發程序,但是這塊處理器涉及到TPU,且官方的基本環境以及教程沒出完,導致這塊處理器的開發SDK其實是分化的。

發表于 03-18 00:12

評論