時鐘樹綜合,通常我們也叫做CTS。時鐘樹綜合就是建立一個時鐘網(wǎng)絡(luò),使時鐘信號能夠傳遞到各個時序器件。CTS是布局之后相當(dāng)重要的一個步驟,如何評價一個時鐘樹的好壞,這個問題可以每個人心中都有不同的答案。

通常各個公司已經(jīng)約定俗成了一套評價時鐘樹的方法,我們也稱為clock tree metrics。包括以下幾點(diǎn):時鐘的傳播延遲(Latency),時鐘偏差(Skew),時鐘轉(zhuǎn)換時間(transition),時鐘不確定性( uncertainty),時鐘的級數(shù)(level)……

這些metrics保證了時鐘的完成性,如何在這些metrics中尋找一個最佳方案,也就保證了時鐘樹的好壞。

時鐘的傳播延遲(Latency)

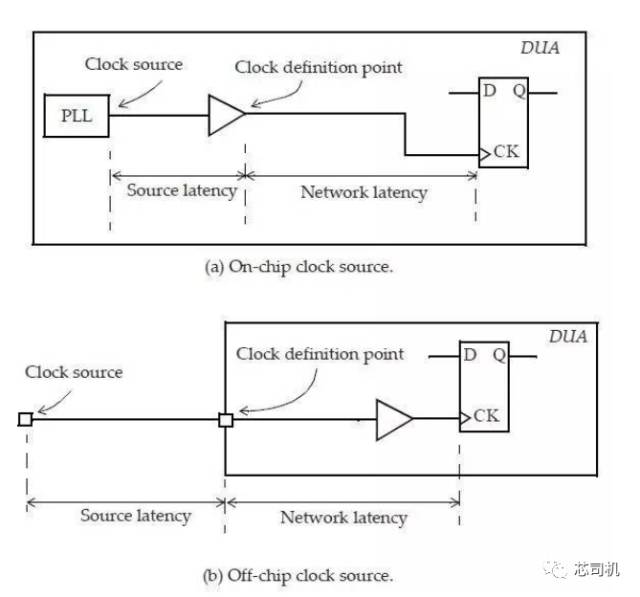

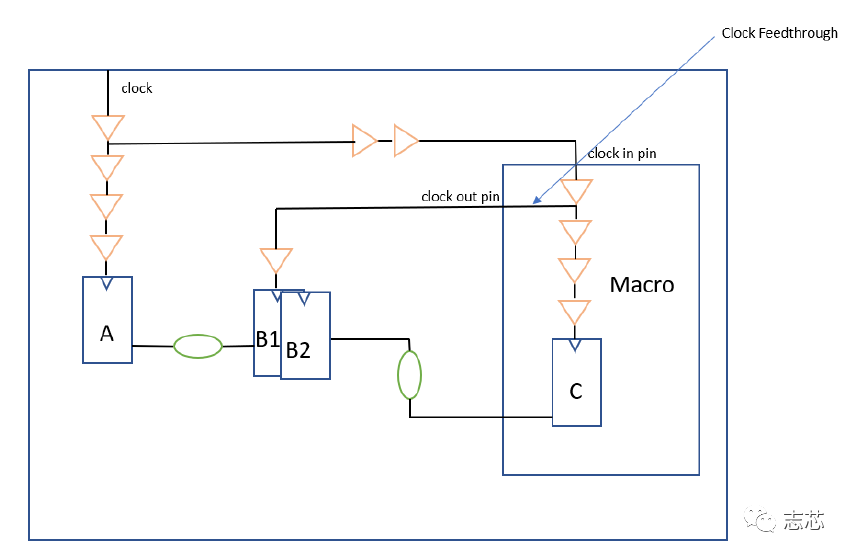

時鐘傳播延遲Latency,通常也被稱為插入延遲(insertion delay)。主要指從Clock源到時序組件Clock輸入端的延遲時間。它可以分為兩個部分,時鐘源插入延遲(source latency)和時鐘網(wǎng)絡(luò)延遲(network latency)

source latency:主要指從clock source端到clock定義端的延遲,即是時鐘源(例如PLL)到當(dāng)前芯片時鐘根節(jié)點(diǎn)(clock root pin)之間的延遲。

network latency:主要指從clock定義端到時序器件的clock pin端的延遲。

以下兩張圖分別定義了片上(on chip)和片外(off chip)中clock latency的描述

那latency值有什么用呢?其實這相當(dāng)于一個target值,CTS的engine會根據(jù)你設(shè)置的latency值來插入buffer(當(dāng)然只是對network latency操作),做出一個接近于你設(shè)定的值,可能多一點(diǎn),也可能少一點(diǎn)。latency值的大小直接影響著clock skew的計算和固定。因為我們的時鐘樹是以平衡為目的,假設(shè)你對一個root和sink設(shè)置了1ns的latency值,那么對另外的幾個sink來說,就算你沒有給定latency值,CTS為了得到較小的skew,也會將另外的幾個sink做成1ns的latency。過大的latency值會受到OCV和PVT等因素的影響較大(因為有time derate的存在)。

時鐘的偏差(skew)

時鐘偏差(skew),這是CTS中相當(dāng)重要的一個概念。在CTS中,由于時鐘到每個寄存器的路徑延遲不一樣,造成信號到達(dá) clock pin 的時間也不一樣,寄存器也不會同時翻轉(zhuǎn)。Skew 的定義就是最長路徑延遲減去最短路徑延遲的值。一直以來,Skew都是衡量時鐘樹性能的重要參數(shù),CTS的目的就是為了減小skew。

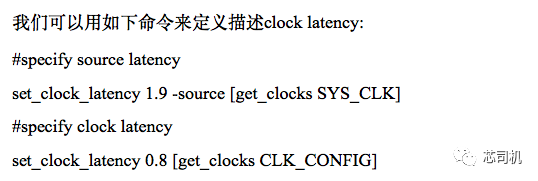

Skew的類型分為很多種,根據(jù)clock和datapath的方向,skew可以分為positive skew和negative skew。如下圖所示:

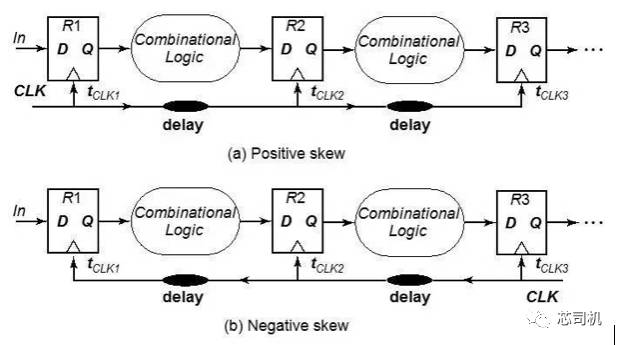

對于positive skew,clock和data path在相同方向上。反之對negative skew來說,clock和data path在相反方向上。那它們對我們的design有什么影響呢?我們來看一下setup和hold的計算公式(這個公司大家應(yīng)該很熟悉吧):

我們可以得到以下結(jié)果

對于positive skew來說,它可以減少T的時間,相當(dāng)于提升芯片的performace。但是它的hold時間會變得更加難以滿足

對于negative skew來說,它的hold時間更加容易滿足,取而代之的是,它會降低芯片的性能。

還有另外一種skew的分類方法,是我們更為常見的,根據(jù)時鐘域以及路徑關(guān)系, skew 可以分為 global skew , local skew , interclock skew。

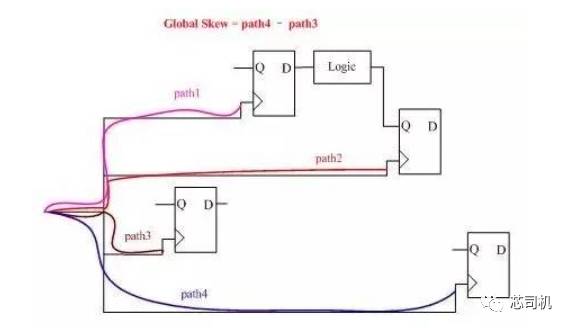

Global skew 是指,同一時鐘域,任意兩個路徑的最大 skew ,如下圖所示。CTS時,工具更關(guān)注的是global skew, 會盡可能地將global skew做小

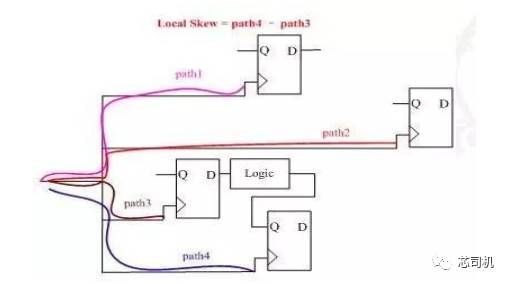

Local skew是指,同一時鐘域,任意兩個有邏輯關(guān)聯(lián)關(guān)系的路徑最大skew,如下圖所示,我們在分析timing的時候,更多地是關(guān)注local skew

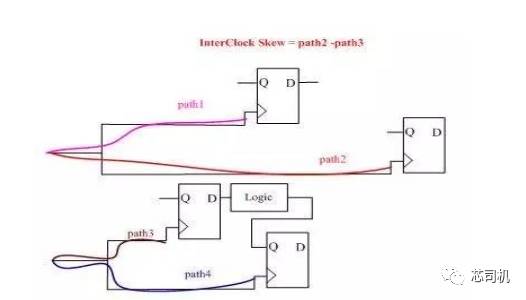

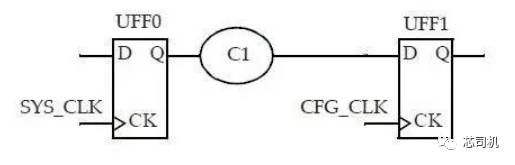

interClock skew 是指,不同時鐘域之間路徑的最大 skew,如下圖所示:

另外還有一種比較特使的skew就是現(xiàn)如今用得較多的useful skew,它也是ccopt這么紅火的一個特色。大概說一下useful skew的概念。

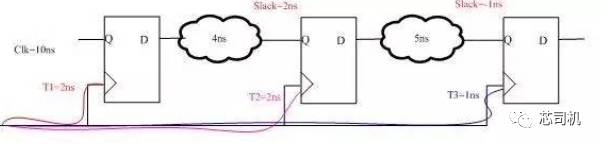

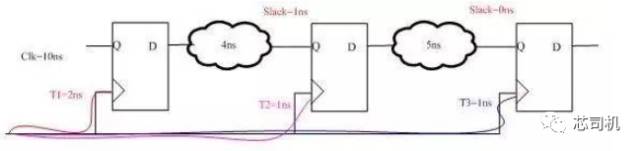

如下圖:時鐘周期為 10ns ,各時鐘路徑延遲如下:可以看到有一條路徑的 slack 為-1ns ,說明這條路徑違規(guī)。可以看到與這條路徑相關(guān)的 skew 是 T3-T2= -1ns 。

下面我們利用 useful skew 向前面一個 slack 比較充裕的路徑(slack=2ns)借點(diǎn) time ,來修正現(xiàn)在這條路徑。如下圖:

這就是 useful skew 的作用,可以向前,或者向后借time來修正 violation。

時鐘轉(zhuǎn)換時間(transition time)

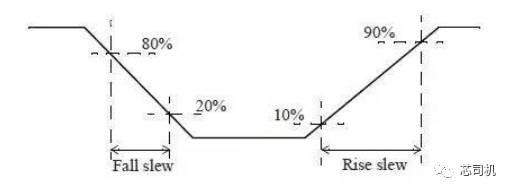

時鐘轉(zhuǎn)換時間clock transition time ,也稱為clock slew。通常是指電壓從10%VDD上升到90%VDD所需要的時間,或者是從90%VDD下降到10%VDD所需要的時間,上升和下降時間過長意味著電路的速度很慢。如下圖所示

在sdc中,用以下命令來限制slew大小

set_max_transition 0.1 -clock_path[all_clocks]

對CTS來說,這也是一個target值,當(dāng)你設(shè)定了一個slew target后,CTS engine會通過插入buffer或者upsize等操作,盡可能地去滿足整個target值。當(dāng)然,slew也不是越小越好,過小的slew會導(dǎo)致CTS階段在clock path上插入過多的buffer,從而影響到skew的balance以及功耗和面積。

時鐘不確定性(clock uncertainty)

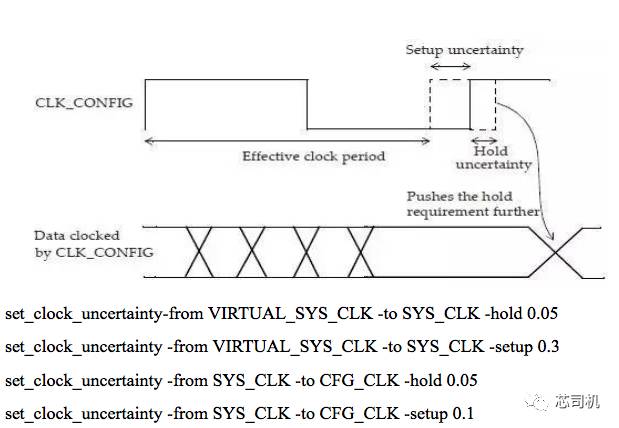

定義了Clock信號到時序器件的Clock端可能早到或晚到的時間。主要是用來降低時鐘抖動jitter對有效時鐘周期的影響。值得注意的是,在setup check中,clock uncertainty是代表著降低了時鐘的有效周期;而在hold check中,clock uncertainty是代表著hold check所需要滿足的額外margin。

來看下面一條reg2reg path. 對照著如下時鐘波形圖。可以寫出下面的約束。

在pre-CTS的時候,我們將時鐘的不確定性設(shè)定為target的skew和jitter值之和來模擬真實的時鐘;而post-CTS之后,時鐘樹propagate delay已經(jīng)確定,skew真實存在,所以uncertainty就是時鐘的真實抖動值。因此preCTS的target skew不能設(shè)置的太大或者太小,這樣會造成preCTS和postCTS的correlation不好。總結(jié)一下:

在pre-CTS中,

setup的clock uncertainty = jitter + clock tree skew

hold的clock uncertainty = clock tree skew

在post-CTS中,

setup的clock uncertainty = jitter

hold的clock uncertainty = 0

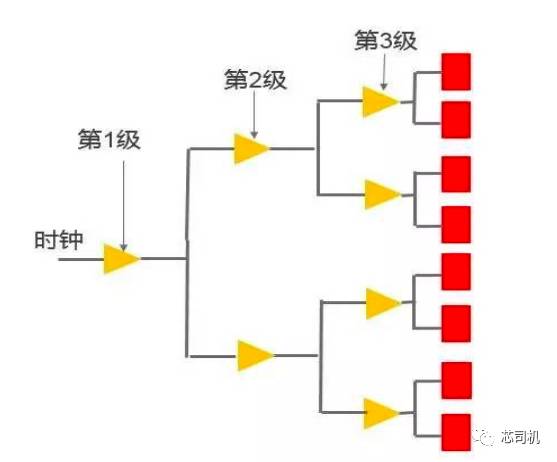

時鐘樹級數(shù)

時鐘樹其實是由buffer一級一級串行級聯(lián)下去組成,每一個分結(jié)點(diǎn)就化分成一級,如下圖所示

通常來說,我們期望時鐘樹的級數(shù)越少越好,因為這樣tree上的common path最長,受到OCV和PVT因素的影響也最小,時鐘的性能也最好。但是,這樣情況下tree很難去生長完成,并且會導(dǎo)致過多的fanout,導(dǎo)致負(fù)載過大,延遲變差。因此這也是一個trade off 的過程。

評價時鐘樹質(zhì)量,可以看主干分岔點(diǎn)是否過早、關(guān)鍵寄存器的級數(shù)是否最少且Size合理、Leaf寄存器分組是否合理,當(dāng)然skew,area,power也是很重要的啦~

-

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131673 -

時鐘樹

+關(guān)注

關(guān)注

0文章

55瀏覽量

10786 -

時鐘網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

16瀏覽量

6580

原文標(biāo)題:如何評價時鐘樹的好壞?

文章出處:【微信號:芯司機(jī),微信公眾號:芯司機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

時鐘樹優(yōu)化與有用時鐘延遲

數(shù)字IC設(shè)計中的分段時鐘樹綜合

音頻質(zhì)量客觀評價中同步方法的研究與實現(xiàn)

STM32F407系統(tǒng)時鐘配置時鐘樹方法

前后端協(xié)同的時鐘樹設(shè)計方法

基于視覺感興趣區(qū)的圖像質(zhì)量評價方法

圖像質(zhì)量評價方法研究進(jìn)展

時鐘網(wǎng)格與時鐘樹設(shè)計方法對比研究

基于視差圖圖像質(zhì)量評價

LUCT工具主要特性及不確定性時鐘樹設(shè)計方法和算法的介紹

色彩復(fù)原圖像的質(zhì)量評價方法

基于深度學(xué)習(xí)的視頻質(zhì)量評價方法及模型研究

評價時鐘樹質(zhì)量的方法

評價時鐘樹質(zhì)量的方法

評論