多年來,NEC CMOS 微控制器集成了各種 EMC 技術,雖然片上電容和倍頻時鐘發生器是有效的,但對PCB 的設計方面卻沒有任何措施,這里是首次闡述。進一步講,應用筆記僅著重于 PCB 設計技術,只有少數 NEC EMC 的片上措施在這里列出,但這些都是有效 EMC 措施,并且都應該在選擇階段考慮的。

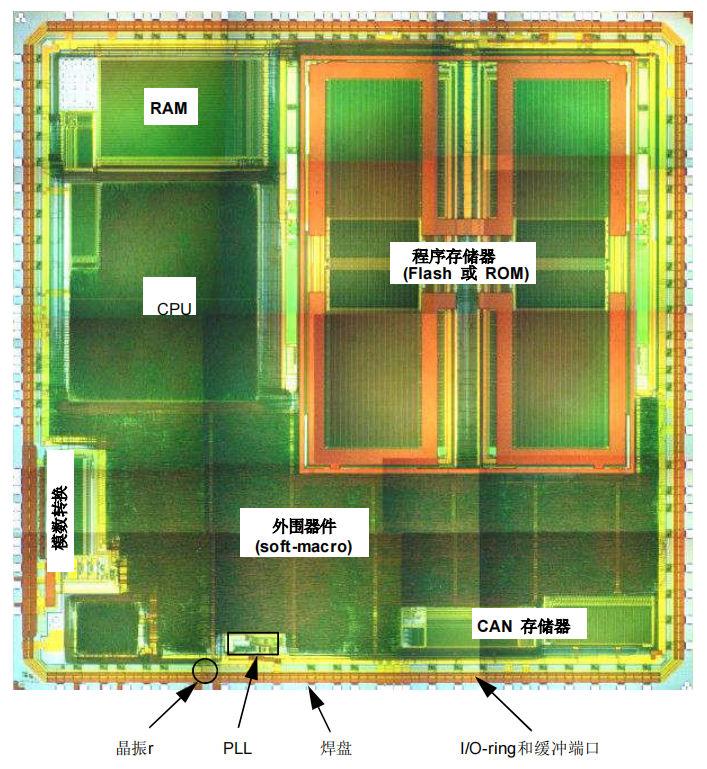

EME 優化退耦目標是通過一個或更多的去耦電容提供一個最高所需高頻電流。高頻電流存放在片上的開關電路中環路越多和電容越低對其它供電電路影響較大。為優化連接線路的阻抗,通常電容盡可能接近微控制器的供電引腳。 為減少電流環路輻射,應當減少環路面積。僅用 PCB 設計技術難以實現最大程度的改善。因此,我們的一貫對策是將部分去耦電容放到芯片內部從而減少連接阻抗,并且適當的考慮電流回路面積,這些片上電容太小以至不能提供整個芯片去耦,所以 PCB 上的電容仍是必要的,然而,對于較高的頻率范圍,它們可以很好地減少輻射。

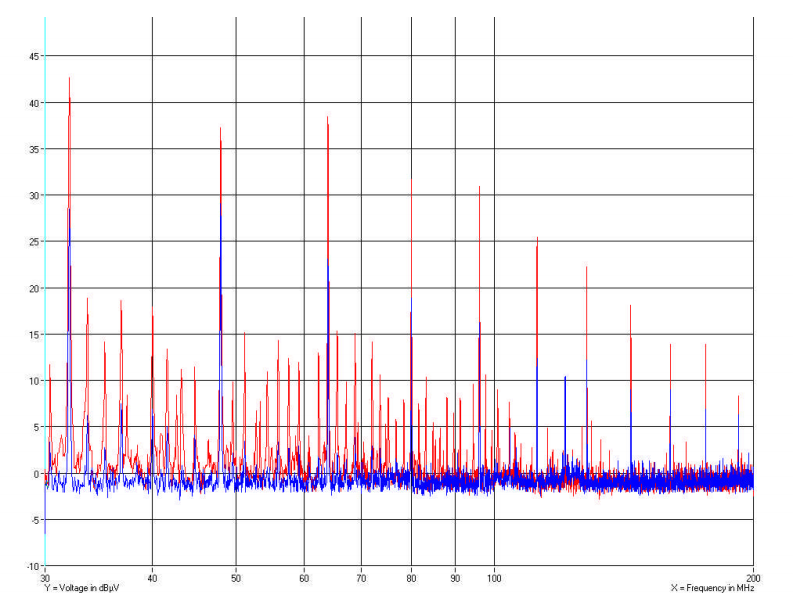

測量結果如圖 4-1,對"同一"微控制器有無片上電容的結果作一下對比。紅色曲線呈現無電容情況下的輻射效果,而藍色曲線是帶有片上電容情況下的輻射效果,有電容時,在很寬的頻率范圍內改善了約 15dB,不僅沒有增加芯片尺寸,而且也沒有增加額外的費用。

審核編輯:湯梓紅

-

微控制器

+關注

關注

48文章

7646瀏覽量

151869 -

NEC

+關注

關注

0文章

238瀏覽量

99158 -

EME

+關注

關注

0文章

9瀏覽量

21787

發布評論請先 登錄

相關推薦

片上系統微控制器推動便攜式醫療設備創新

ADI 新款精密模擬微控制器集成了片上數據轉換器,可簡化光模

恩智浦推出首款內嵌易用型片上CANopen驅動微控制器

EE-178:ADSP-TS101S TigerSHARC?片上SDRAM控制器

基于硬件損耗均衡算法的片上norflash控制器設計

瑞薩推出SH7216系列32-位片上Flash存儲器MCU

NEC微控制器的片上EMC措施——片上電容

NEC微控制器的片上EMC措施——片上電容

評論