SERDES的優(yōu)勢(shì)

引腳數(shù)量和通道優(yōu)勢(shì)

SERDES最明顯的優(yōu)勢(shì)是具備更少的引腳數(shù)量和線纜/通道數(shù)量。對(duì)于早期的SERDES,這意味著數(shù)據(jù)可以通過(guò)同軸電纜或光纖發(fā)送。

對(duì)于現(xiàn)代的SERDES來(lái)說(shuō),另一個(gè)優(yōu)勢(shì)是能夠通過(guò)一對(duì)差分對(duì)信號(hào)引腳(而不是8、16、32或N個(gè)數(shù)據(jù)引腳和一個(gè)時(shí)鐘引腳)發(fā)送數(shù)據(jù)。在串行傳輸這個(gè)方面得益于更小的數(shù)據(jù)包和更密集的pcb而節(jié)省了成本。具體取決于晶片成本、封裝成本、PCB成本和PCB擁塞等因素。

距離優(yōu)勢(shì)

在過(guò)去的十年里,SERDES在PCB和基板上遠(yuǎn)距離傳輸?shù)哪芰σ呀?jīng)幫助它們應(yīng)用在許多新的領(lǐng)域中。

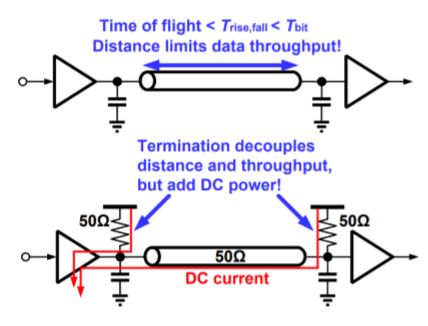

圖1通過(guò)端接并行總線來(lái)極大地提高傳輸距離、功耗效率

從簡(jiǎn)單的微波設(shè)計(jì)中,當(dāng)傳輸線的傳輸時(shí)間小于上升/下降時(shí)間時(shí),看起來(lái)像是一個(gè)“集總元件”。對(duì)于一個(gè)GPIOs(通用輸入輸出)的并行接口,上升/下降時(shí)間通常在幾納秒以上。這使得非端接并行接口得以在典型PCB上以30cm的距離正常工作。端接并行總線將增加傳輸距離,但是,它會(huì)增加大量的功耗,并使功效急劇下降(如圖1)。

SERDES接口通常通過(guò)兩端(TX,RX)的受控阻抗傳輸線傳輸。這可以讓數(shù)據(jù)快速的傳輸且不需要考慮反射損耗。當(dāng)然,為了快速、串行地傳輸數(shù)據(jù),需要增加很多額外的復(fù)雜設(shè)計(jì)—串行器、解串器、TXPLLs(發(fā)送)、RXCDRs(接收)、前饋均衡(FFE)、接收均衡等等。

注:

串行器的作用:在傳遞和保存對(duì)象時(shí)快,保證對(duì)象的完整性和可傳遞性。對(duì)象轉(zhuǎn)換為有序字節(jié)流,以便在網(wǎng)絡(luò)上傳輸或者保存在本地文件中;

解串器的作用:根據(jù)字節(jié)流中保存的對(duì)象狀態(tài)及描述信息,通過(guò)解串重建對(duì)象;

總結(jié):核心作用就是對(duì)象狀態(tài)的保存和重建。

功耗優(yōu)勢(shì)

直到最近,SERDES相對(duì)于并行數(shù)據(jù)總線在功耗上的優(yōu)勢(shì)才得以顯現(xiàn)。理想的并行總線所消耗的能量是發(fā)送(TX)和接收(RX)電容和跡線(trace)電容充放電時(shí)產(chǎn)生的。FR4(覆銅板)上的跡線(trace)電容在傳輸距離為10,20或100厘米時(shí)會(huì)變得非常大,這一點(diǎn)需要特別注意。

根據(jù)基本原理,我們知道LVCMOS鏈路的功耗是~C×V2×f。就數(shù)據(jù)而言,頻率則是總比特率的二分之一乘以傳輸密度。傳輸?shù)目倲?shù)據(jù)量和功耗、線路數(shù)量無(wú)關(guān)——線路越多,每條線路傳輸?shù)臄?shù)據(jù)量就越少。對(duì)于1Gb/s的線路,10厘米到1米距離可能需要8-16條線路。對(duì)于10Gb/s的線路,1m的距離可能需要120條線路!這是非常不切實(shí)際的。

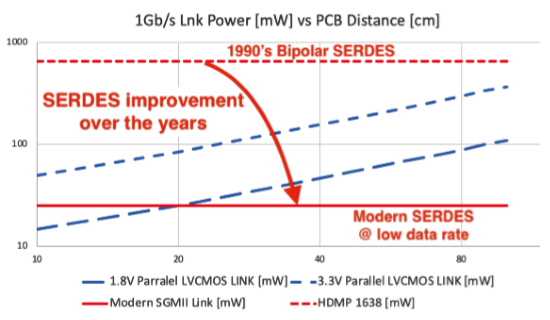

圖2:不同電壓下并行LVCMOS鏈路和1990年代及現(xiàn)代SERDES在功耗方面的對(duì)比

圖2顯示了不同電壓下并行LVCMOS鏈路和1990年代以及現(xiàn)代SERDES在功耗方面的對(duì)比。可以明顯的看出,現(xiàn)代SERDES在長(zhǎng)距離上具有功耗上的優(yōu)勢(shì),但是這個(gè)優(yōu)勢(shì)并不明顯。

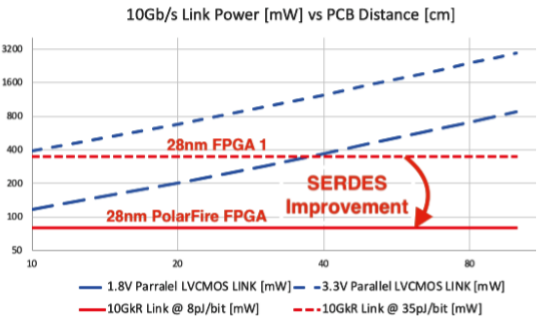

當(dāng)數(shù)據(jù)速率越高時(shí),SERDES在功耗上的優(yōu)勢(shì)就越明顯。圖3顯示了在2010年代中期到后期,不同電壓下并行LVCMOS鏈路的功耗與不同28nmSERDES功耗的對(duì)比。可以看出,現(xiàn)代的SERDES在幾乎所有的距離上都保持著功耗上的優(yōu)勢(shì)。對(duì)于一個(gè)功耗經(jīng)過(guò)優(yōu)化后的SERDES,在所有距離上,功耗優(yōu)勢(shì)都是巨大的。

當(dāng)然,隨著工藝技術(shù)的進(jìn)步,SERDES的功耗上的優(yōu)勢(shì)將會(huì)繼續(xù)擴(kuò)大。

圖3:不同電壓下并行LVCMOS鏈路的功耗與不同28nmSERDES功耗的對(duì)比

對(duì)SERDES演變的看法

我的職業(yè)生涯開(kāi)始于惠普SERDESASICs的開(kāi)發(fā)團(tuán)隊(duì)。HDMP-1638是我參與開(kāi)發(fā)的首批產(chǎn)品之一。由于安捷倫從惠普剝離,該ASIC的logo為“安捷倫”,而非“惠普”。

由于這個(gè)芯片在當(dāng)時(shí)十分具有競(jìng)爭(zhēng)力,且銷售很好,對(duì)于20到25年前的工業(yè)SERDES來(lái)說(shuō),它都是一個(gè)benchmark。該芯片設(shè)計(jì)為雙極型(bipolar)工藝,它以1.25Gbps的線路速率來(lái)支持千兆以太網(wǎng)(802.3z)和1000Base-XGb/s的光纖以太網(wǎng)。

HDMP-1638的功耗約為1W,其中包括一個(gè)外部并行接口——畢竟是SERDES芯片!該芯片的功耗(不包括并行接口)估計(jì)為650mW,或大約500pJ/bit。稍后我們將繼續(xù)說(shuō)一說(shuō)它與現(xiàn)代SERDES在功效(pJ/bit)方面的比較。

注:pJ/bit-發(fā)送每bit信息的能量消耗。

自2006年以來(lái),我一直在SiliconCreations公司幫助開(kāi)發(fā)高級(jí)節(jié)點(diǎn)的低功耗SERDES。近年來(lái),SiliconCreations一直在開(kāi)發(fā)高達(dá)32Gb/s傳輸速率的SERDES,并將功效降低到2.5pJ/bit。拿這些SERDES和20年前的相比:

1.速度增加了25倍

2.功效提高了200倍

工藝、電壓調(diào)節(jié)以及設(shè)計(jì)方面的巨大進(jìn)步促成了如此明顯的性能提升。

SERDES面臨的挑戰(zhàn)

如前一節(jié)所述,SERDES在功耗、引腳數(shù)量和傳輸距離方面具有很大的優(yōu)勢(shì)。SERDES的缺點(diǎn)是則是其復(fù)雜性和成本。

復(fù)雜性在較低的數(shù)據(jù)傳輸速率上,至少需要TXPLL、RXCDR、TXdriver和RXfront。每一個(gè)都是復(fù)雜的模擬子系統(tǒng)。設(shè)計(jì)這些模塊和整個(gè)SERDES系統(tǒng)需要一個(gè)熟練的模擬/混合信號(hào)設(shè)計(jì)團(tuán)隊(duì)來(lái)完成。這些模塊(連同復(fù)雜的數(shù)字控制)包括:

TXPLL:這個(gè)模塊需要用25-100MHz的參考時(shí)鐘(具備1ps以下的長(zhǎng)時(shí)抖動(dòng))產(chǎn)生一個(gè)數(shù)GHz級(jí)的時(shí)鐘。

RXCDR:這個(gè)模塊是一個(gè)復(fù)雜的控制回路,用于跟蹤傳入數(shù)據(jù)的平均相位,而不管鏈路上的任何噪聲、失真或串?dāng)_。這通常是通過(guò)復(fù)雜的相位旋轉(zhuǎn)器或CDR驅(qū)動(dòng)的鎖相環(huán)來(lái)完成的。

TXdriver:這個(gè)模塊把序列化數(shù)據(jù)轉(zhuǎn)化為一個(gè)典型的50?差分信號(hào)。

RX均衡器:此模塊用連續(xù)時(shí)間均衡器和DFE(判決反饋均衡器)來(lái)均衡高速通道效應(yīng)。通常需要一個(gè)自動(dòng)增益(AGC)電路來(lái)促進(jìn)均衡效果。RX均衡器通常以狀態(tài)機(jī)邏輯或軟件的形式來(lái)實(shí)現(xiàn)自動(dòng)校準(zhǔn)。

高速串行器和解串器邏輯:上面列出的所有模塊都需要一個(gè)經(jīng)驗(yàn)豐富的設(shè)計(jì)團(tuán)隊(duì)花費(fèi)相當(dāng)多的設(shè)計(jì)時(shí)間(需多人開(kāi)發(fā)數(shù)年)。隨著數(shù)據(jù)速率(Gb/s)的提高和對(duì)效率(pJ/bit)的要求的增加,SERDES的復(fù)雜性和成本也隨之增加。對(duì)著可靠性需求的增加,必須進(jìn)行越來(lái)越多的老化和電遷移模擬和分析,這又進(jìn)一步增加了成本。

本文聚焦于PAM2/NRZSERDES,而PAM4提供了每個(gè)引腳具有更高帶寬的替代方案,但通常的代價(jià)是在PAM2/NRZ系統(tǒng)上進(jìn)一步增加芯片面積、功耗和復(fù)雜性。

幸運(yùn)的是,SERDES已經(jīng)作為IP模塊被廣泛的使用。因此,做系統(tǒng)的公司可以從主要的IP提供商那獲取設(shè)計(jì)許可證(license)。通過(guò)這種方式,設(shè)計(jì)復(fù)雜度可由專門的設(shè)計(jì)團(tuán)隊(duì)來(lái)分?jǐn)偅邪l(fā)成本也可以在多個(gè)芯片、項(xiàng)目甚至行業(yè)之間共享,從而幫助降低成本。

成本

SERDES的主要費(fèi)用來(lái)自設(shè)計(jì)(許多設(shè)計(jì)者花費(fèi)了許多年)和驗(yàn)證,除此之外,芯片面積和PCB大小也是十分重要的影響因素。

PMA層的SERDES驗(yàn)證通常由一個(gè)設(shè)計(jì)子團(tuán)隊(duì)處理。在系統(tǒng)層,驗(yàn)證可能相當(dāng)復(fù)雜,特別是對(duì)于像PCIe這樣的標(biāo)準(zhǔn)。

注:SerDes主要由物理介質(zhì)相關(guān)(PMD:PMD-PhysicalMediaDependent)子層、物理媒介附加(PMA:physicalmediumattachment)子層和物理編碼子層(PCS:PhysicalCodingSublayer )所組成。PMD是負(fù)責(zé)串行信號(hào)傳輸?shù)?a target="_blank">電氣塊,PMA負(fù)責(zé)串行化/解串化,PCS負(fù)責(zé)數(shù)據(jù)流的編碼/解碼。在PCS的上面是上層功能。針對(duì)FPGA的SERDES,PCS提供了ASIC塊和FPGA之間的接口邊界。

對(duì)于復(fù)雜的串行標(biāo)準(zhǔn)和測(cè)試程序(比如SystemVerilog),需要從物理層(包括PMA和PCS)、數(shù)據(jù)鏈路層、業(yè)務(wù)層和設(shè)備層去驗(yàn)證系統(tǒng)。涵蓋這些層的驗(yàn)證通常需要檢查協(xié)議、模式、錯(cuò)誤注入和恢復(fù)等方面。驗(yàn)證通常也需要很多個(gè)月的時(shí)間,并且經(jīng)常涉及到第三方來(lái)驗(yàn)證IP。

在晶片價(jià)格上,SERDES和并行接口不好比較。根據(jù)工藝節(jié)點(diǎn)的不同,一個(gè)SERDES每條線路大約占用0.15到0.5mm2的空間。一個(gè)并行接口可以比這個(gè)小得多,但是需要更多的I/O口。因此,晶片成本取決于芯片對(duì)I/O和對(duì)引腳的需求如何平衡。

在封裝和PCB方面,SERDES允許減少引腳和跡線總數(shù)。因此,這樣的封裝和PCB設(shè)計(jì)的尺寸將更小,成本更低。但是,由于高速受控阻抗的復(fù)雜性,SERDES的封裝和PCB設(shè)計(jì)將十分困難,因此,在這方面比使用相對(duì)速度較低的并行接口更昂貴。

總結(jié)

在過(guò)去的20年里,SERDES已經(jīng)從光纖和網(wǎng)絡(luò)電路轉(zhuǎn)變?yōu)槲覀兩磉叧R?jiàn)的電路,從手機(jī)到筆記本電腦,從電視到數(shù)據(jù)中心等等。

PCIe大約是在2002年引入的,那時(shí)的線速率是2.5Gb/s。從那時(shí)起,設(shè)計(jì)的改進(jìn)和CMOS工藝的提高使得線路速率提高了約20倍(從2.5Gb/s到50Gb/s),功率效率(pJ/bit)提高了約200倍。

SERDES(Serializer-Deserializer)是串行器和解串器的簡(jiǎn)稱。串行器(Serializer)也稱為SerDes發(fā)送端(TX),(deserializer)也稱為接收端(RX)。

PLL模塊、TX發(fā)送模塊、RX接收模塊。

串行器把并行信號(hào)轉(zhuǎn)化為串行信號(hào),解串器把串行信號(hào)轉(zhuǎn)化為并行信號(hào)。

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7134瀏覽量

89398 -

引腳

+關(guān)注

關(guān)注

16文章

1219瀏覽量

50785 -

SerDes

+關(guān)注

關(guān)注

6文章

201瀏覽量

34999

原文標(biāo)題:SerDes的好處在哪里(下)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SerDes技術(shù)優(yōu)勢(shì)明顯,解決車內(nèi)高速傳輸難題

ASP4644在FPGA SERDES供電中的應(yīng)用

請(qǐng)問(wèn)6678中的srio的serdes和以太網(wǎng)的serdes是共用還是各自有自己的serdes?

SERDES接口電路設(shè)計(jì)

SERDES傳輸和引腳關(guān)聯(lián)

請(qǐng)問(wèn)單個(gè)SERDES Quad可以同時(shí)運(yùn)行4個(gè)接收通道嗎?

SerDes是怎么工作的

基于FPGA芯片的SERDES接口電路設(shè)計(jì)

如何使用FPGA實(shí)現(xiàn)SERDES協(xié)議

SERDES的優(yōu)勢(shì) SERDES演變的看法

SerDes收發(fā)器內(nèi)部的電路物理層結(jié)構(gòu)設(shè)計(jì)分析

什么是SerDes?SerDes的應(yīng)用場(chǎng)景又是什么呢?

SerDes是怎么設(shè)計(jì)的?(一)

SerDes:串行和并行通信有何區(qū)別?

SERDES的引腳數(shù)量和通道優(yōu)勢(shì)

SERDES的引腳數(shù)量和通道優(yōu)勢(shì)

評(píng)論