對于嵌入式系統設計人員來說,最令人沮喪的情況之一發生在當他們完成許多設計里程碑后,他們發現最初選擇的嵌入式設備不符合當前的設計要求。在開發周期過程中,會出現需求變化和其他不可預見的挑戰,尤其是在新產品設計中。

已開發出片上系統 (SoC) 設備,尤其是混合信號 SoC 設備,以克服這些困難。雖然不同的 SoC 公司有不同的方式來描述他們的 SoC,但歸根結底,SoC 本質上是一個微控制器(無論是低功耗 8 位還是高功率 32 位),具有大量集成的模擬和/或數字外圍設備。此外,SoC 設備引入了自定義、配置和編程這些資源的能力。

可配置性使客戶能夠靈活地決定如何將比較器和運算放大器等外設路由到引腳。這些組件的靜態引腳位置與傳統的固定功能微控制器不同。使用設備上的一系列寄存器,客戶可以根據他們的特定應用需求配置設備。此外,混合信號 SoC 設備還可能包含在不同級別上可編程的數字資源,從基本的可配置邏輯到更大的可編程邏輯設備 (PLD) 資源,可以使用諸如 Verilog 之類的硬件描述語言進行配置。使用這些可編程數字資源,開發人員可以輕松創建狀態機和其他復雜電路,例如在硬件中對數字信號執行 FFT。

雖然具有這種高水平的可配置性允許開發人員適應開發過程中可能發生的設計更改,但仍有一些情況會達到所選 SoC 的限制。這些限制可能是由于設計要求超出了部件的能力,或者是由于需要在器件芯片上實現沒有固定功能組件的特性或特定功能。通過利用使混合信號 SoC 如此有用的可配置性和靈活路由,開發人員可以克服設備架構本身可能存在的許多缺點。探索其中的幾個設計挑戰和幾個關于 SoC 設備如何克服這些問題的實際示例可以提供洞察力。

克服模擬 SoC 挑戰

克服模擬設計挑戰可能是嵌入式混合信號開發中最困難的事情之一。與被認為更“通用”且更像構建塊的數字外圍設備不同,模擬外圍設備的功能“相當固定”,因為它們本質上是一個組件系統,而不是構建塊。工程師將可以使用模擬外設,例如模數轉換器 (ADC)、比較器和數模轉換器 (DAC),所有這些都可以配置到某種級別。

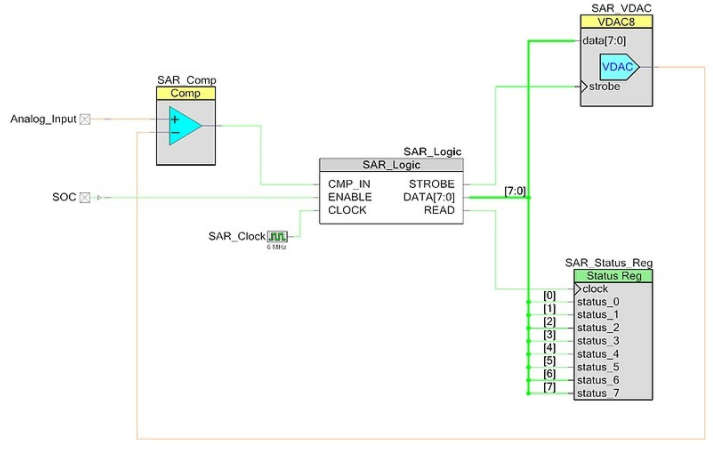

一個普遍面臨的設計挑戰是設計中需要額外的 ADC。如果客戶不想多路復用 ADC 輸入或想要實現特定類型的 ADC,例如僅包含 Delta Sigma ADC 的設備中的逐次逼近寄存器 (SAR) ADC,則可能會遇到這種情況。要了解 SoC 如何從自身內部克服這一點,讓我們從設計中需要 SAR ADC 的角度來看這個問題。構建 SAR ADC 所需的組件是比較器、DAC、狀態寄存器和一些可編程數字邏輯。所有這些都是可以在 SoC 設備上找到的組件。當這些組件以類似于圖 1 所示的方式排列時,可以創建功能性 SAR ADC。

圖 1:使用可用資源實施 SAR

通過讀取存儲在狀態寄存器中的內容來收集 8 位輸出。各種數字功能,例如算術運算和位移,使用 Verilog 在硬件中完成。這種資源組合創造了以前不存在于 8 位 118 KSps 設備中的功能。作為一個額外的好處,只要有更多的比較器、DAC 和數字邏輯,就可以提供額外的 SAR ADC。

許多混合信號 SoC 設備還包含專用比較器和運算放大器。當這些資源耗盡時,或者在設備從一開始就沒有包含這些外圍設備的情況下,可以做什么?模擬電路,例如比較器、有源濾波器、可編程增益放大器和跨阻放大器,都由一個運算放大器組成,該運算放大器使用各種電阻器和/或電容器來創建特定功能。一些混合信號 SoC 包含所謂的開關電容 (SC) 外設。SC 外圍設備圍繞低噪聲、低偏移運算放大器構建,周圍環繞著模擬多路復用器,周圍環繞著電容器和開關組。如果開關處于靜態打開或關閉狀態,則結果是一個電容器連接到電路。此外,如果開關以特定頻率交替打開和關閉,則開關電容器開始表現得像一個無損電阻器。

包含開關電容器的器件,例如 Cypress Semiconductor 的 PSoC 系列器件,使用寄存器配置來控制開關電容器拓撲中的開關,以產生各種電路,從最基本的運算放大器到更高級的電路,例如混合器、積分器或粘性和保持。

克服數字 SoC 挑戰

開發人員面臨著 SoC 架構的重大數字設計挑戰。考慮到傳統的微控制器,它將包含一些固定功能的數字外設,例如脈沖寬度調制器 (PWM) 和定時器。SoC 設備包含數字邏輯,例如可編程邏輯設備、算術邏輯單元 (ALU) 和狀態/控制電阻器。使用諸如 Verilog 之類的硬件描述語言,可以將這些硬件資源配置為協同工作以創建許多可能的功能組件。

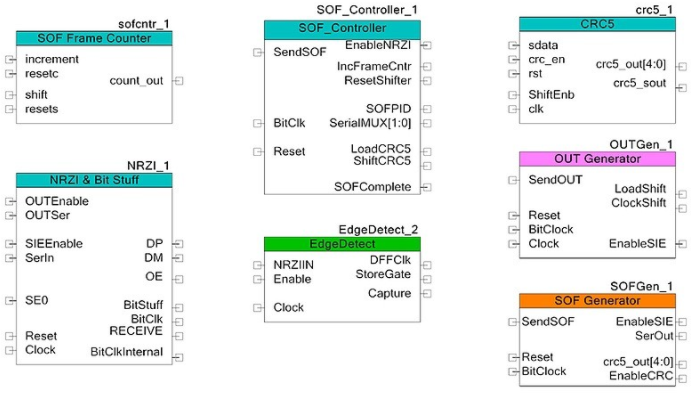

考慮一個包含外圍 USB 接口的 SoC 設備。在設計周期的后期,我們決定還支持主機 USB 功能以實現諸如允許連接 USB 閃存驅動器以進行數據記錄或現場可編程固件更新等功能。問題是正在使用的設備不包含實現主機功能所需的硬件。然而,使用可配置的數字資源,SoC 設備可以克服這種數字設計限制。

要了解需要合并的內容,請考慮處理 USB 通信需要什么。有差分信號,然后是 SOF 生成、不歸零反轉 (NRZI) 編碼/解碼、循環冗余校驗 (CRC) 計算、位填充和 IN/OUT 數據包解析。如果設計人員閱讀 USB 規范,他們會發現所需的一切實際上都可以在 PLD 中實現,并借助一些附加組件。通過一些廣泛的 Verilog 編碼來利用前面描述的數字資源,可以制作用于主機 USB 通信的各個組件,如圖 2 所示。這里,所示的每個塊代表具有各種數字輸入和輸出的 Verilog 實現。通過將這些組件與一些粘合邏輯連接在一起,

圖 2:使用可編程硬件實現 USB 主機

這種可配置性意味著,如果為包含例如兩個 PWM、兩個比較器、兩個 DAC 和一個 Delta Sigma ADC 的設計選擇混合信號 SoC,則這些外設并不是其硬件功能的終點。可以重新利用和修改資源,以將資源擴展到與最初可能需要的功能不同的功能。這樣,工程師無需遷移到新的嵌入式設備,就可以增加產品的價值并減少新產品設計的開發時間;該決定通常會導致新的固件開發和 PCB 布局,從而導致時間和金錢的損失。通過調用在早期電氣工程課程中學到的技能以及混合信號 SoC 設備的靈活性

審核編輯:郭婷

-

pcb

+關注

關注

4324文章

23156瀏覽量

399225 -

adc

+關注

關注

99文章

6532瀏覽量

545420 -

soc

+關注

關注

38文章

4196瀏覽量

218782

發布評論請先 登錄

相關推薦

Qorvo推出車規級UWB SoC芯片QPF5100Q,憑借可配置軟件推動創新

LMK1D1208I I2C可配置低附加抖動LVDS緩沖器數據表

具有可配置輸出電壓和3態輸出的八進制雙電源總線收發器SN74LVCC4245A-EP 數據表

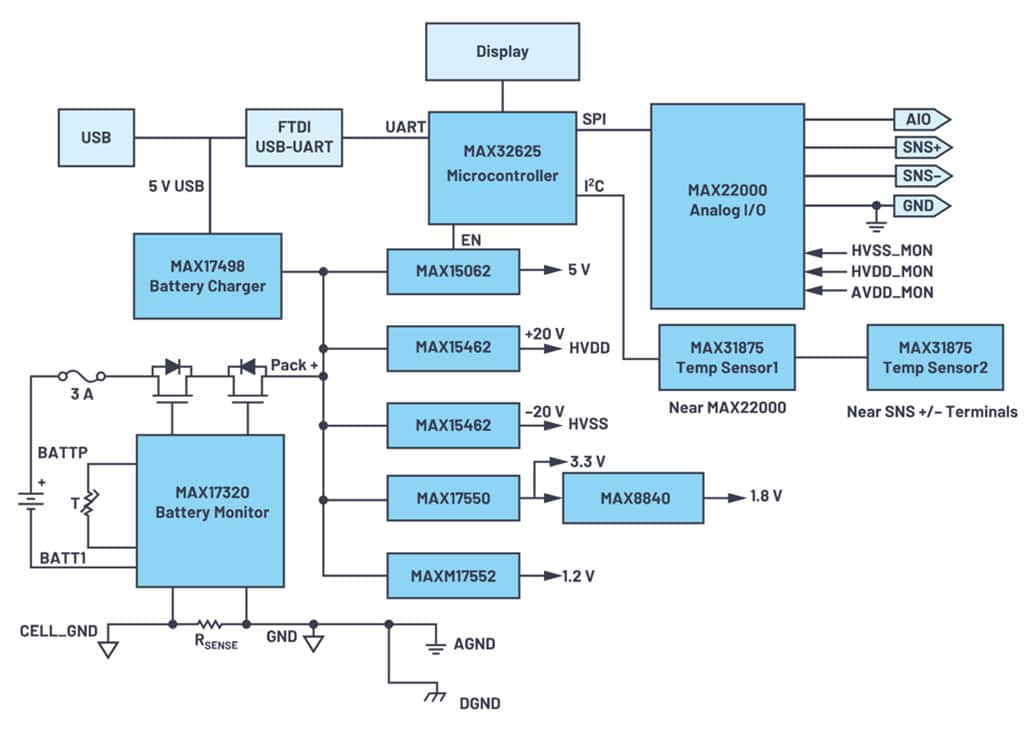

軟件可配置模擬 I/O 的設計理念

嵌入式系統的外設器件選擇

具有可配置輸出電壓和三態輸出的八路雙電源總線收發器SN74LVCC4245A數據表

通過2D/3D異質結構精確控制鐵電材料弛豫時間

高性能2.4G SOC無線收發芯片 XL2401D 產品介紹

TPS650864可配置多軌PMU適用于多核處理器、FPGA和系統的TPS650861可配置多軌PMU數據表

可配置的A/D外設克服了SoC器件的缺點

可配置的A/D外設克服了SoC器件的缺點

評論