物聯(lián)網(wǎng)跨越多個應(yīng)用領(lǐng)域,設(shè)計團隊的要求可能因最終應(yīng)用領(lǐng)域而異。雖然功率、性能和成本是電子元件硅設(shè)計中要滿足的標準優(yōu)先事項,但汽車和航空航天/國防等應(yīng)用領(lǐng)域?qū)踩蕴砑拥皆O(shè)計優(yōu)先事項列表中,而在其他領(lǐng)域,安全性是關(guān)鍵或現(xiàn)場可升級性需要被考慮。

驗證、原型設(shè)計和軟件開發(fā)是跨這些領(lǐng)域和設(shè)計要求的共同主題。為了允許嵌入式軟件開發(fā),經(jīng)典的早期驗證技術(shù)(如模擬)通常被認為太慢,而使用 QEMU 等虛擬平臺的抽象有時被認為不夠準確。

長期以來,基于 FPGA 的原型設(shè)計一直是硅前軟件開發(fā)的首選平臺。與它的老大哥硬件仿真相比,在 Cadence Palladium Z1 企業(yè)仿真平臺等工具中,它的執(zhí)行性能從 MHz 級擴展到 10 兆赫茲甚至 100 兆赫范圍,而且成本更低,允許將其復(fù)制給軟件團隊的更多成員。

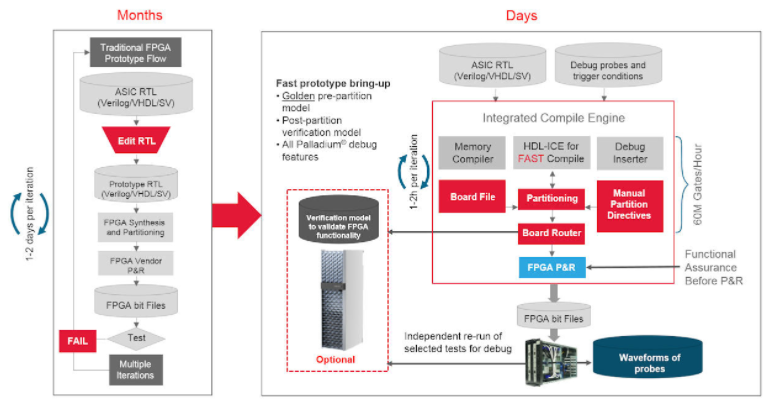

傳統(tǒng)上,基于 FPGA 的原型的障礙一直是它的啟動過程,有時需要幾個月的時間才能提供給軟件開發(fā)人員。原因是需要將 ASIC 設(shè)計從其實際的硅目標技術(shù)重新映射到 FPGA 提供的結(jié)構(gòu)中,這需要重新映射部分設(shè)計。

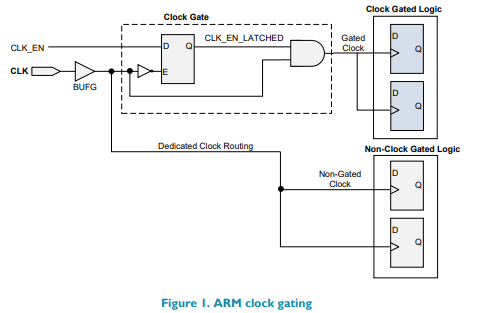

首先,ASIC 中的存儲器需要映射到 FPGA 中可用的資源中,或者映射到包含特定附加存儲器(如 DDR)的子卡中。處理 ASIC 的時鐘可能是一場噩夢,在 PCB 和 FPGA 上更復(fù)雜的設(shè)計中需要同步 10 多個時鐘。跨多個 FPGA 對設(shè)計進行分區(qū)絕非易事,而且通常需要使用低壓差分信號 (LVDS) 技術(shù)在同一引腳上多路復(fù)用多個信號。

[Palladium Z1 和 Protium S1 平臺的 Cadence 多結(jié)構(gòu)編譯流程。]

傳統(tǒng)上,較大的公司擁有原型設(shè)計團隊,專門負責設(shè)計團隊正在開發(fā)的 RTL 版本并將其映射到 FPGA 中。然而,隨著設(shè)計復(fù)雜性的增加,執(zhí)行上述所有任務(wù)變得越來越困難,而軟件開發(fā)人員則不耐煩地在團隊上空盤旋以訪問它。

借助基于 Protium S1 FPGA 的原型設(shè)計平臺,Cadence 重新審視了原型設(shè)計,并專注于將原型設(shè)計時間從數(shù)月縮短至數(shù)周甚至數(shù)天。它通過在 Palladium Z1 仿真和基于 Protium S1 FPGA 的原型設(shè)計之間實現(xiàn)一致性,以及重新使用一些仿真前端進行原型設(shè)計來做到這一點。

復(fù)雜的手動內(nèi)存建模已使用仿真中已知的內(nèi)存模型自動化;編譯流程負責 FPGA 之間的分區(qū)和時鐘同步。可以在仿真中驗證要映射到 FPGA 架構(gòu)的網(wǎng)表,從而節(jié)省寶貴的布局布線時間。一旦在基于 FPGA 的原型設(shè)計中以比仿真快約 5 倍的速度識別出缺陷,就可以將相同的設(shè)計推回仿真,以利用那里提供的更好的調(diào)試功能。

作為還包括形式驗證、仿真和仿真的 Cadence 驗證套件的一部分,基于 FPGA 的原型設(shè)計剛剛通過自動化進行了重新發(fā)明,并可供更廣泛的物聯(lián)網(wǎng)設(shè)計開發(fā)人員使用。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605215 -

pcb

+關(guān)注

關(guān)注

4324文章

23159瀏覽量

399307 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164188

發(fā)布評論請先 登錄

相關(guān)推薦

驗證中的FPGA原型驗證 FPGA原型設(shè)計面臨的挑戰(zhàn)是什么?

重新審視醫(yī)療處理技術(shù)的未來

怎么采用FPGA原型系統(tǒng)加速物聯(lián)網(wǎng)設(shè)計?

MATLAB和Simulink算法原型如何在FPGA上適配?

FPGA原型驗證的技術(shù)進階之路

將 Virtualizer 虛擬原型和 HAPS 系列基于 FPGA 的原型無縫集成

使用FPGA平臺的處理器ARMCortex原型設(shè)計的說明

消除PCB原型重新旋轉(zhuǎn)5條建議

FPGA原型平臺到底能跑多快呢?

什么是FPGA原型驗證?如何用FPGA對ASIC進行原型驗證

基于FPGA原型設(shè)計的SoC開發(fā)

重新審視基于FPGA的原型設(shè)計

重新審視基于FPGA的原型設(shè)計

評論