1.項(xiàng)目概述

1.1 系統(tǒng)實(shí)現(xiàn)功能介紹

在當(dāng)下,很多應(yīng)用場(chǎng)景都要用到視頻目標(biāo)跟蹤的功能,諸如商業(yè)產(chǎn)品、工程實(shí)踐亦或者軍事技術(shù)中。它們都提出了高幀率、高精度、高魯棒性、低功耗的硬性要求,這在當(dāng)前的技術(shù)實(shí)現(xiàn)上仍然是一個(gè)挑戰(zhàn)。此時(shí)就需要專用硬件加速器進(jìn)行目標(biāo)跟蹤算法的部署,以實(shí)現(xiàn)低功耗、超高幀率以及高精度的需求。

在本設(shè)計(jì)中,采取Cortex-M3軟核掛載大規(guī)模專用硬件加速器,在DIGILENT的NEXYS-VIDEO開(kāi)發(fā)板中通過(guò)FPGA來(lái)部署硬件級(jí)別的多特征融合相關(guān)濾波目標(biāo)跟蹤算法加速器,做到最高每秒1000幀的運(yùn)算速度,若配合高速視頻傳入,可以達(dá)到極高的跟蹤實(shí)時(shí)性。硬件加速器掛載在軟核總線中,可以通過(guò)寄存器值控制硬件加速器,進(jìn)行參數(shù)設(shè)置、回傳坐標(biāo)以及部署智能算法。所設(shè)計(jì)的硬件加速器深度定制,可以調(diào)節(jié)從算法運(yùn)算原理到跟蹤模式、搜索范圍等多維度的參數(shù)。同時(shí)在硬件中前置了智能目標(biāo)檢測(cè)算法,當(dāng)有移動(dòng)的目標(biāo)出現(xiàn)在視野中,可以自動(dòng)實(shí)現(xiàn)捕捉,傳輸初始坐標(biāo)值至跟蹤算法。

同時(shí)本設(shè)計(jì)還將通過(guò)軟核操控云臺(tái)、觸摸屏、8路選擇器,串口,按鍵陣列等外設(shè),進(jìn)行人機(jī)交互,優(yōu)化跟蹤效果,實(shí)現(xiàn)跟蹤可視化、易操作化以及智能跟蹤化。系統(tǒng)通過(guò)云臺(tái)來(lái)使得目標(biāo)始終在視頻中央?yún)^(qū)域,從而進(jìn)行持續(xù)的目標(biāo)鎖定。系統(tǒng)還可以通過(guò)四線電阻觸摸屏進(jìn)行初始信息的標(biāo)定、切換任務(wù)。同時(shí)通過(guò)HDMI屏幕顯示目標(biāo)的實(shí)時(shí)位置,為系統(tǒng)操作員提供更直觀的目標(biāo)信息。

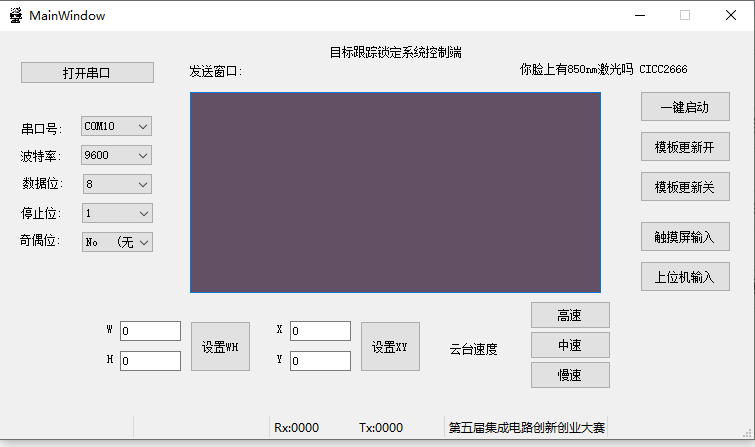

軟核與硬件加速器通過(guò)總線寄存器控制,而軟核與PC端則通過(guò)串口上位機(jī)通信,本組基于QT5.9編寫(xiě)專用控制端上位機(jī),通過(guò)上位機(jī)可以更輕松的操控整套系統(tǒng),方便的輸入XYWH等參數(shù),設(shè)置跟蹤模式等等功能。

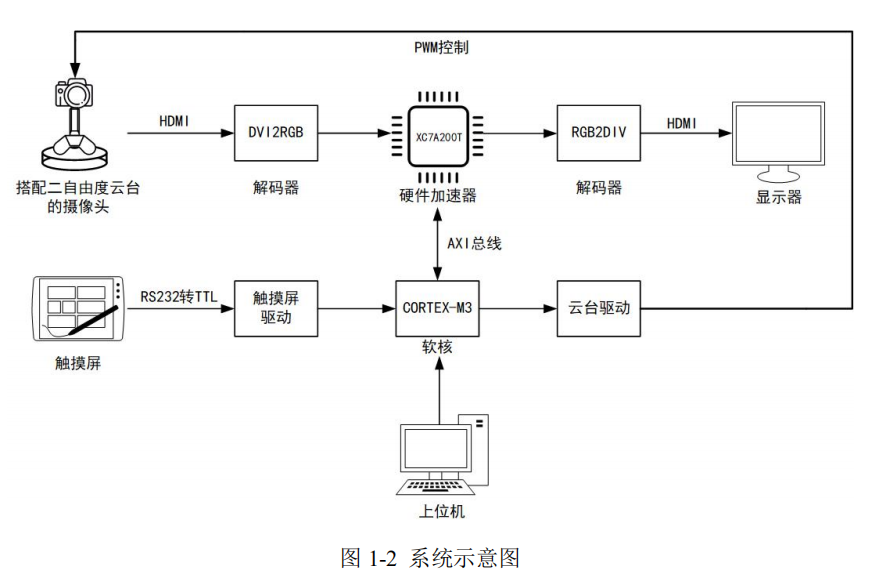

在本項(xiàng)目輸入輸出環(huán)路為:觸摸屏和上位機(jī)作為輸入設(shè)備,也可以通過(guò)智能目標(biāo)檢測(cè)功能自動(dòng)輸入坐標(biāo),上位機(jī)通過(guò)Uart串口進(jìn)行系統(tǒng)參數(shù)及狀態(tài)指令的傳輸。通過(guò)在FPGA內(nèi)部編寫(xiě)觸摸屏的硬件驅(qū)動(dòng)來(lái)實(shí)現(xiàn)觸摸屏坐標(biāo)的解析傳遞。上位機(jī)與軟核相連,軟核的應(yīng)用程序中編寫(xiě)與上位機(jī)相適配的程序,對(duì)跟蹤器進(jìn)行完全的控制,輸出設(shè)備為HDMI顯示屏和二維云臺(tái)。在HDMI顯示屏中輸出目標(biāo)跟蹤框,同時(shí)FPGA控制二維云臺(tái)進(jìn)行目標(biāo)的鎖定。閉環(huán)系統(tǒng)示意圖如圖1-2所示:

1.2 方案設(shè)計(jì)

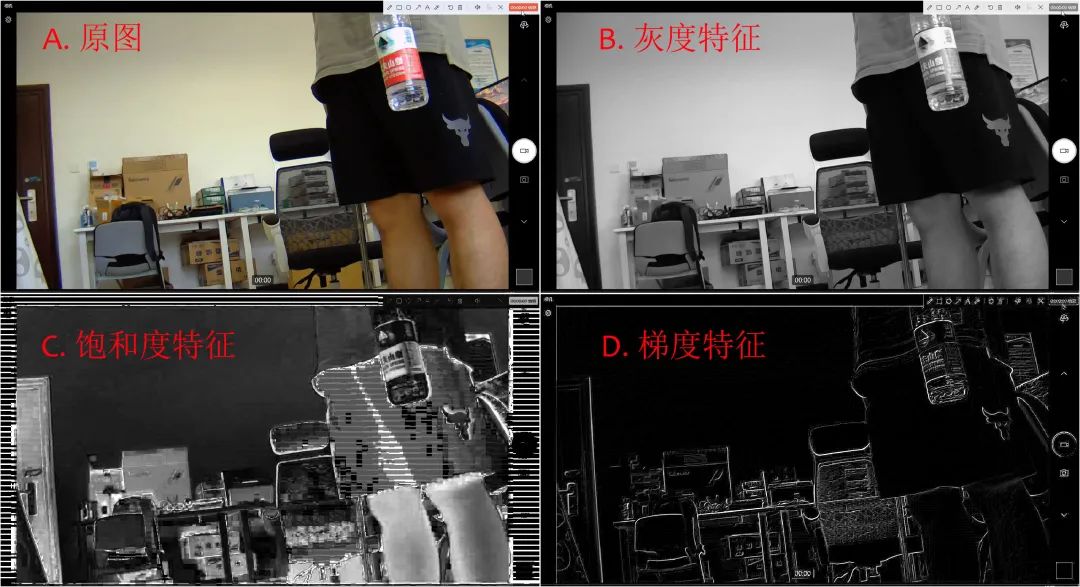

本設(shè)計(jì)綜合考慮多種圖像特征,選用灰度、飽和度和HoG三種特征融合進(jìn)行相關(guān)濾波,它們?nèi)叩膬?yōu)缺點(diǎn)形成互補(bǔ)。

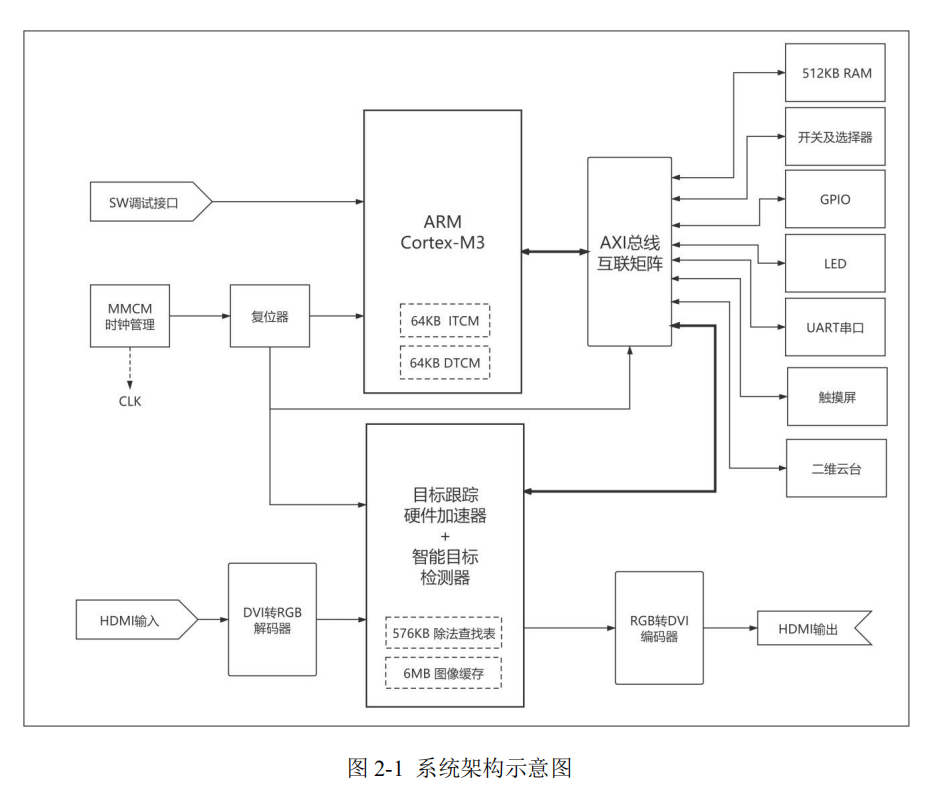

我們采用CORTEX-M3加硬件加速器聯(lián)合設(shè)計(jì),系統(tǒng)架構(gòu)圖如下所示:

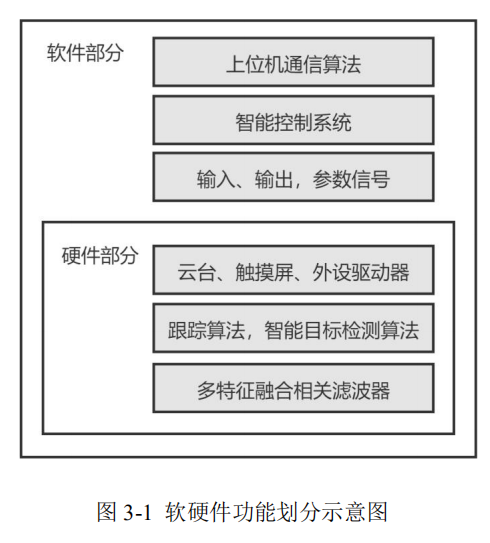

本項(xiàng)目采用Cortex-M3軟核做控制部分,大規(guī)模專用硬件加速器做濾波跟蹤計(jì)算和智能目標(biāo)檢測(cè)部分,視頻輸入輸出通過(guò)HDMI直接進(jìn)入硬件加速器,繞過(guò)軟核實(shí)現(xiàn)更快的數(shù)據(jù)處理速度。整個(gè)項(xiàng)目的軟硬件功能劃分如圖所示:

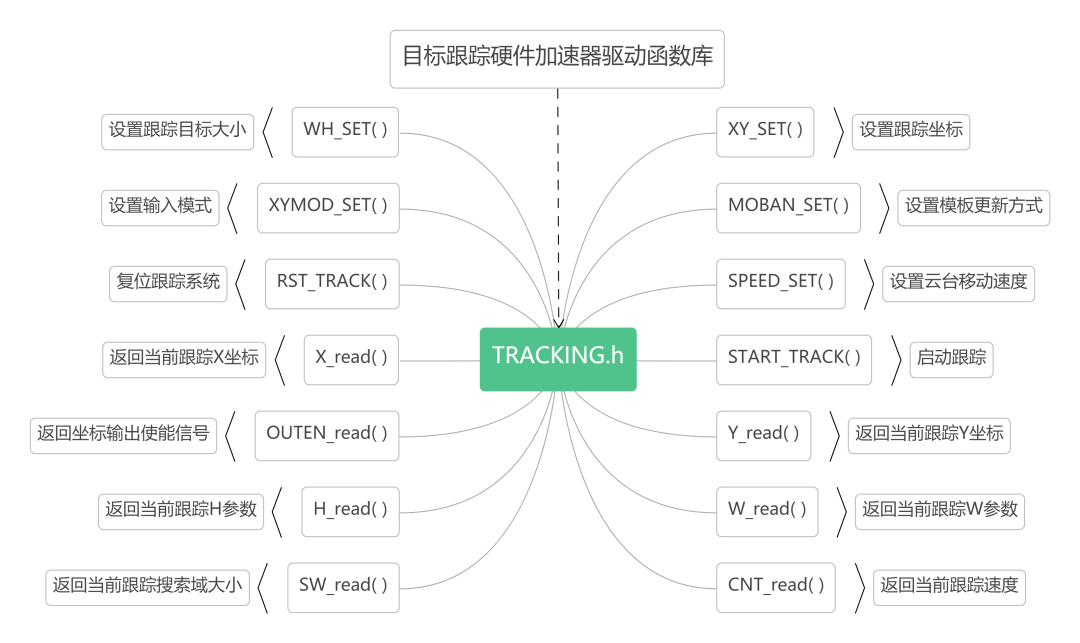

在軟核中,可以通過(guò)調(diào)用我們編寫(xiě)的TRACKING.h庫(kù)函數(shù),使用為硬件加速器所寫(xiě)的驅(qū)動(dòng)函數(shù),實(shí)現(xiàn)硬件加速器跟蹤算法的配置和運(yùn)行,進(jìn)行個(gè)性化算法配置。其中TRACKING.h庫(kù)函數(shù)中所擁有的驅(qū)動(dòng)函數(shù)如圖所示。

我們?cè)O(shè)計(jì)了控制端上位機(jī),上位機(jī)為目標(biāo)跟蹤鎖定系統(tǒng)控制端,由QT5軟件編寫(xiě)完成。

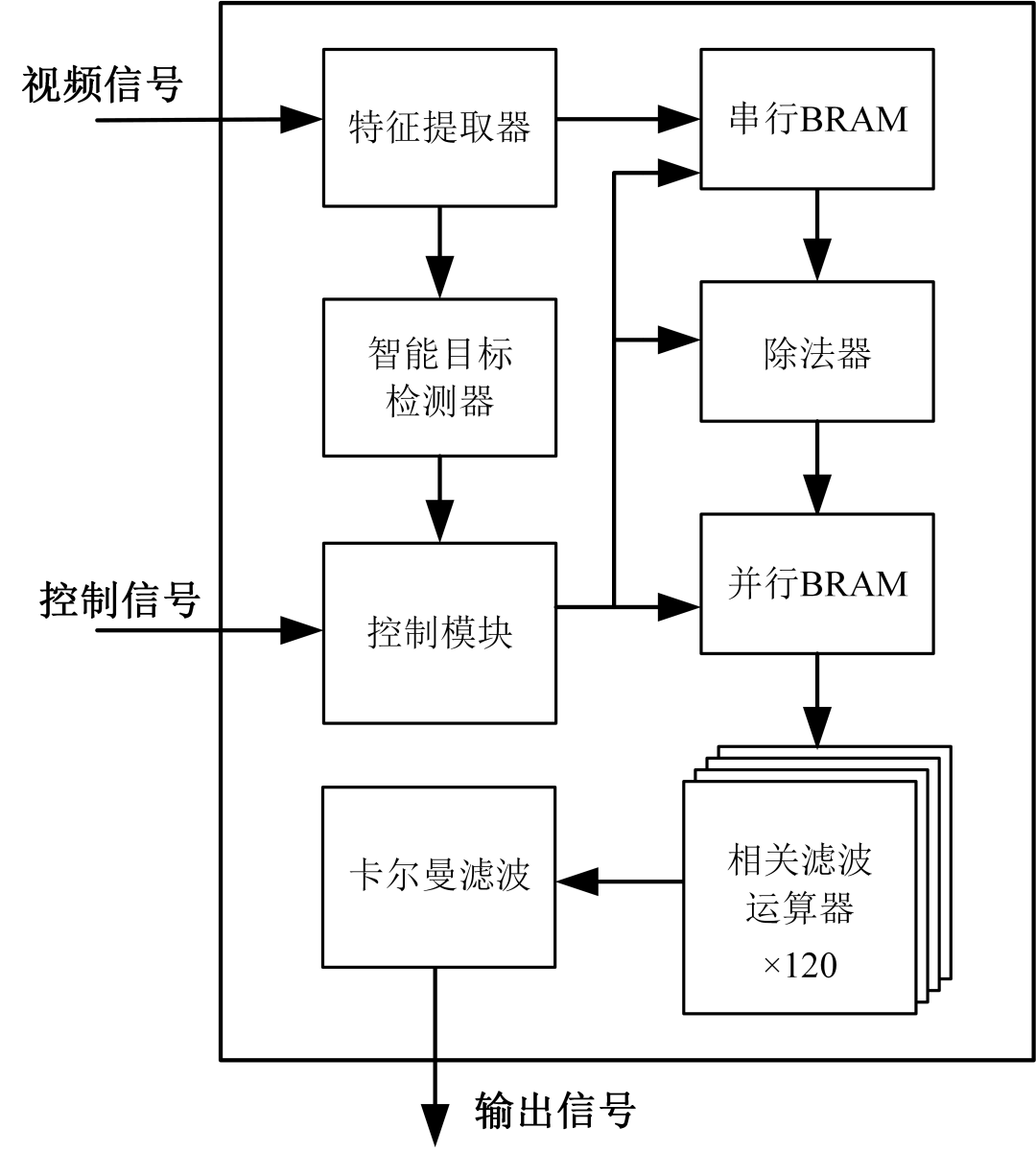

在硬件加速器中,使用多個(gè)模塊共同配合完成工作,其模塊圖如下所示:

2.測(cè)試結(jié)果

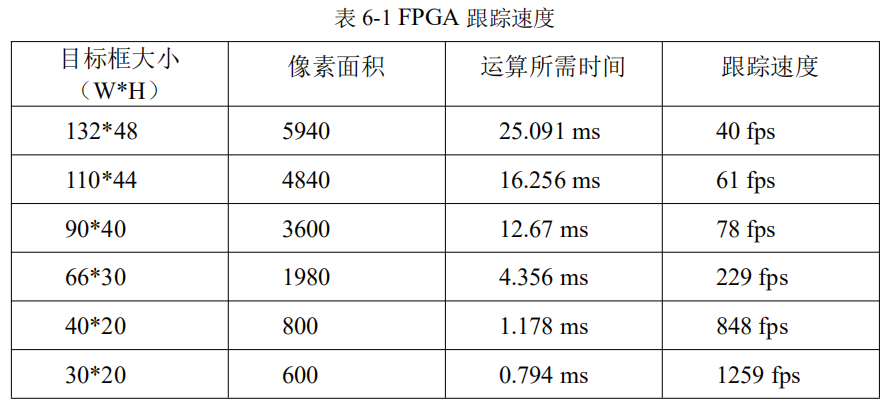

算法運(yùn)行在 40MHz,通過(guò) FPGA 內(nèi)部 32 位計(jì)數(shù)器實(shí)測(cè)的濾波循環(huán)速度

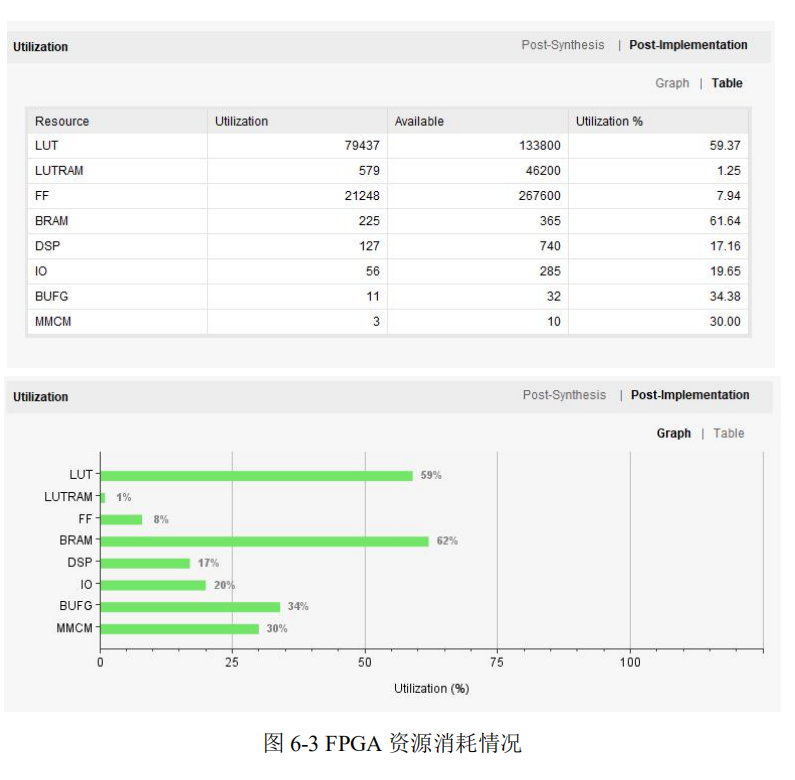

本項(xiàng)目在 NEXYS-VIDEO 開(kāi)發(fā)板中部署,所需的 FPGA 資源如下圖所示:

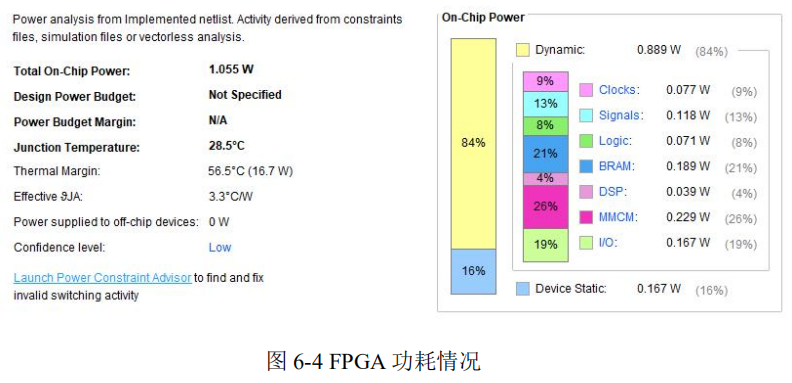

所占用的功耗較低,如下圖所示:

3. 總結(jié)與展望

本組使用FPGA硬件加速器 +Cortex-M3軟核所實(shí)現(xiàn)的基于灰度、飽和度和HoG特征融合的相關(guān)濾波跟蹤算法,運(yùn)行穩(wěn)定,幀率較高,魯棒性強(qiáng),功率消耗低,配合攝像頭可以在多個(gè)應(yīng)用場(chǎng)景使用。例如機(jī)場(chǎng)檢測(cè),工地監(jiān)測(cè),無(wú)人機(jī)機(jī)載跟蹤等等。同時(shí)使用灰度特征、飽和度特征和HoG特征,對(duì)攝像頭要求較低,對(duì)像素要求較低。在常規(guī)目標(biāo)跟蹤中精度很好,超常規(guī)算法。

由于多特征融合互補(bǔ),加卡爾曼濾波軌跡預(yù)測(cè),在復(fù)雜環(huán)境中,即使一個(gè)特征受到干擾失效,也能成功通過(guò)融合響應(yīng)跟蹤到目標(biāo)位置。即使兩個(gè)特征同時(shí)受到干擾失效,比如80%以上大面積遮擋,卡爾曼濾波器也能輸出預(yù)測(cè)位置,抗干擾能力較強(qiáng)。

在系統(tǒng)中使用二維云臺(tái)和觸摸屏外設(shè),同時(shí)使用智能目標(biāo)檢測(cè)算法,實(shí)現(xiàn)了目標(biāo)跟蹤和鎖定的功能,可以很方便的觀察目標(biāo)跟蹤的情況。即可以通過(guò)觸摸屏,快捷實(shí)現(xiàn)跟蹤選點(diǎn),更可以通過(guò)智能目標(biāo)檢測(cè)算法智能自動(dòng)捕捉,人機(jī)交互方便易用。自主編寫(xiě)的上位機(jī)控制系統(tǒng)和可移植驅(qū)動(dòng)函數(shù)庫(kù),使項(xiàng)目更適應(yīng)專業(yè)的應(yīng)用場(chǎng)景,而不拘泥于常規(guī)應(yīng)用。

同時(shí)設(shè)計(jì)的系統(tǒng)僅需BRAM緩存,不需要DDR3內(nèi)存進(jìn)行緩存,整體使用純Verilog代碼編寫(xiě),對(duì)外設(shè)要求較低。同時(shí)可以通過(guò)軟核AXI總線擴(kuò)展所需的應(yīng)用。硬件加速器中參數(shù)全部引出,且設(shè)計(jì)了應(yīng)用函數(shù)庫(kù),大大降低嵌入式開(kāi)發(fā)所需的工作,很方便的移植到不同平臺(tái)。

最后,由于硬件加速器的設(shè)計(jì)工作全部自主完成,根據(jù)邏輯分模塊編寫(xiě),所以能很方便的進(jìn)行改進(jìn)工作,在其他目標(biāo)識(shí)別,視頻跟蹤領(lǐng)域,也可以對(duì)硬件加速器進(jìn)行一定的改進(jìn)來(lái)適配不同的場(chǎng)景,可塑性強(qiáng)。

4. 參賽體會(huì)

我們組在參加本次集創(chuàng)賽的過(guò)程中,踩過(guò)很多坑,趕過(guò)很多DDL,最后終于一步一步做出想要的系統(tǒng)。如果說(shuō)最值得分享的經(jīng)驗(yàn),就是集創(chuàng)賽是一個(gè)比賽周期漫長(zhǎng)的競(jìng)賽項(xiàng)目,不同于數(shù)模的三天,電賽的一周,集創(chuàng)賽擁有大半年的時(shí)間來(lái)完成題目。有些隊(duì)伍只花費(fèi)一個(gè)月來(lái)完成作品,有些隊(duì)伍花費(fèi)幾個(gè)月,有些隊(duì)伍甚至有前置的技術(shù)鋪墊,這對(duì)每個(gè)隊(duì)來(lái)說(shuō)都是未知的。相對(duì)來(lái)說(shuō),有付出就會(huì)有回報(bào),做的時(shí)間越長(zhǎng),在這道題中的感受就越深,所學(xué)到的東西就越多。

競(jìng)賽是對(duì)自己的提升,將時(shí)間放在集創(chuàng)賽上絕對(duì)是一個(gè)很好的選擇。但與此同時(shí),也要有效率的進(jìn)行比賽,盡可能的少出BUG,三個(gè)人的團(tuán)隊(duì)協(xié)作要密切互補(bǔ),一個(gè)人的單打獨(dú)斗肯定沒(méi)有團(tuán)隊(duì)的力量大。

在集創(chuàng)賽的過(guò)程中,由于參加的項(xiàng)目是FPGA數(shù)字方向,還要求做軟核及上層應(yīng)用程序,所以對(duì)我們參賽隊(duì)伍的要求是很高的,不僅要會(huì)掌握Verilog的編寫(xiě),F(xiàn)PGA的使用,還要掌握嵌入式軟核的交叉編譯工作,CPU的調(diào)試,總線的知識(shí)等等,在我們隊(duì)伍中由于還要使用上位機(jī),我們還學(xué)習(xí)了QT程序開(kāi)發(fā)的內(nèi)容。比賽所涉及的知識(shí)廣度和深度都很大,需要認(rèn)真努力的去學(xué)習(xí)。

審核編輯 :李倩

-

寄存器

+關(guān)注

關(guān)注

31文章

5362瀏覽量

120899 -

加速器

+關(guān)注

關(guān)注

2文章

805瀏覽量

37997 -

Cortex-M3

+關(guān)注

關(guān)注

9文章

270瀏覽量

59537

原文標(biāo)題:【2021集創(chuàng)賽作品分享】第九期 | 基于CORTEX-M3硬件加速的目標(biāo)跟蹤鎖定系統(tǒng)

文章出處:【微信號(hào):Ithingedu,微信公眾號(hào):安芯教育科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Cortex-M3/M4F指令集技術(shù)用戶手冊(cè)

TDA4VM上的硬件加速運(yùn)動(dòng)恢復(fù)結(jié)構(gòu)算法

基于ARM Cortex-M3單片機(jī)研發(fā)的國(guó)產(chǎn)指紋芯片 - P1032BF1

基于 FPGA 的目標(biāo)跟蹤電磁炮系統(tǒng)

PSoC 6 MCUBoot和mbedTLS是否支持加密硬件加速?

求助,關(guān)于cortex-M3的壓棧問(wèn)題求解

新思科技硬件加速解決方案技術(shù)日在成都和西安站成功舉辦

用DE1-SOC進(jìn)行硬件加速的2D N-Body重力模擬器設(shè)計(jì)

STM32F103VE添加DSP庫(kù)報(bào)錯(cuò)ld.exe: cannot find -l-mcpu=cortex-m3是什么原因呢?

Cortex-M3芯片有哪些

Cortex-M3芯片怎么樣

FM3 CY9BFx1xS/T系列Arm Cortex-M3微控制器Cypress

【國(guó)產(chǎn)FPGA+OMAPL138開(kāi)發(fā)板體驗(yàn)】(原創(chuàng))7.硬件加速Sora文生視頻源代碼

音視頻解碼器硬件加速:實(shí)現(xiàn)更流暢的播放效果

強(qiáng)大的Arm? Cortex?-M3內(nèi)核(下)

基于CORTEX-M3硬件加速的目標(biāo)跟蹤鎖定系統(tǒng)

基于CORTEX-M3硬件加速的目標(biāo)跟蹤鎖定系統(tǒng)

評(píng)論