本文探討了物聯網設備的軟件和硬件安全性的同等重要性,并提供了可操作的步驟來保護RISC-V上的嵌入式處理器。

各種形式和規模的技術供應商都喜歡吹捧其產品的安全性。但現實情況是,當今的技術絕對不安全。詳細描述最新攻擊及其受害者的頭條新聞似乎以不斷增加的速度傳播,而且問題似乎隨著時間的推移而增長。

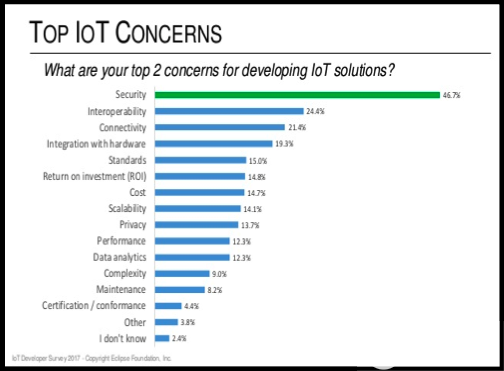

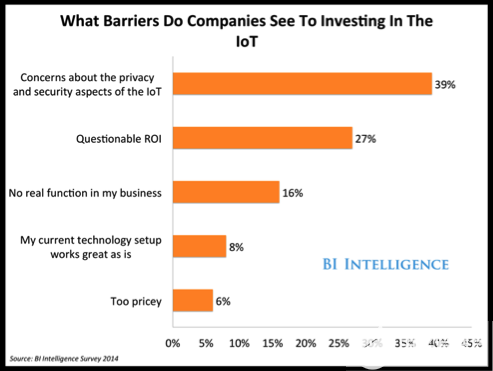

即使是物聯網設備的制造商,盡管有企業營銷言論,似乎也對當前的安全狀態感到焦慮。在Eclipse 基金會最近的一項調查中,46% 的受訪物聯網開發人員表示,在設計物聯網解決方案時,安全是他們最關心的問題。同樣,在2014 年 BI Intelligence 調查中,39% 的受訪者表示,對隱私和安全的擔憂是公司考慮投資物聯網的最大障礙。這兩項研究都表明,技術不安全正在對物聯網的傳播和采用產生負面影響。

圖 1.物聯網開發人員最關心的物聯網問題。

圖 2. 對隱私和安全的擔憂被列為投資的最大障礙。

這種擔憂只會因新聞中每天出現的網絡攻擊而加劇——似乎永無止境的頭條新聞強調了我們連接的設備缺乏安全性所帶來的災難性后果。從對拉斯維加斯賭場的網絡攻擊,攻擊者能夠通過大廳水族館中的無線溫度計成功訪問其安全網絡,到召回超過 800,000個被確定對用戶可能致命的 Abbott 起搏器,再到飛機可以在飛行中被地面攻擊者接管的現實。攻擊者從未有過更多選擇,而我們所謂的防御根本不起作用。

為什么缺乏物聯網安全性?

物聯網是一個以硬件為基礎的空間,但許多物聯網硬件設計團隊會爭辯說,安全是軟件開發團隊的責任。然而,為什么硬件團隊必須擁有安全性有一個簡單的解釋:大多數網絡攻擊利用軟件中的錯誤。因此,添加更多軟件來保護您的硬件顯然不是答案。所有復雜的軟件都有漏洞,只有硬件才能通過消除攻擊者首先利用軟件漏洞的能力來解決這個問題。

保護 RISC-V 上的嵌入式處理器

RISC-V 社區可以使用完整的安全生態系統,任何硬件設計人員都可以采取一些簡單的步驟來確保其物聯網解決方案的安全性。

第 1 步:創建威脅模型并將其包含在您的 SoC 或 ASIC 設計規范中

威脅建模是通過識別資產和漏洞并確定其優先級來優化產品安全性的過程。威脅模型定義了防止或減輕對系統的威脅的對策。它們最常應用于軟件應用程序,但也可用于具有同等效力的硬件系統。I/O Active或BishopFox等安全顧問可以為您的設計提供咨詢服務和安全評估。

第 2 步:在 SoC 或 ASIC 設計流程中實施安全設計流程

硬件漏洞是您無法修補的問題。這種植根于系統底層硬件的漏洞有可能為攻擊者永久打開大門。重要的是要意識到被忽視的硬件安全漏洞超出了反應性軟件更新的范圍。因此,請確保您在設計流程中包含了為安全而設計的心態。如果做得好,這有可能顛覆腳本:沒有漏洞的硬件設計可以為給定的物聯網設備強制執行所有必要的安全性。Tortuga Logic等公司可以協助實施。

第 3 步:研究安全 IP 提供商并確定哪些產品最能滿足您的安全威脅模型中規定的要求

信任根、加密、身份驗證、可信執行環境、安全啟動過程:所有這些解決方案以及更多解決方案都可能需要成為您最終產品的一部分。確保您已對與您的威脅模型相關的 IP 解決方案進行了適當的調查,并將它們的優點和成本與您的需求和資源進行比較。RISC-V 社區中有多家供應商提供安全 IP 解決方案,包括Microsemi、Intrinsix、Silex、Inside Secure和Rambus。

第 4 步:集成 Sentry 協處理器作為主處理器的保鏢

Sentry 協處理器可防止利用軟件漏洞。Dover 的CoreGuard 硅 IP等解決方案 與現有的 RISC-V 處理器集成,以監控主機處理器執行的每條指令,以確保它符合一組安全、安全和隱私規則。如果一條指令違反了現有規則,哨兵處理器會在造成任何損害之前阻止它執行。

第 5 步:集成您的安全 IP 解決方案并與您的 SoC 或 ASIC 的其余部分進行驗證

實施是橡膠上路的地方。發揮您的設計魔力,但請記住,系統的生死取決于其驗證工作。智能硬件的安全性與其驗證過程一樣好。提示:讓您的客戶了解您的驗證流程——不要只是要求他們信任您,而是要向他們表明他們可以信任您。

安全應該存在于硬件和軟件中

對應用程序和操作系統代碼的純軟件保護已成為過去。借助功能強大的基于硬件的 IoT 處理器解決方案,不要浪費任何時間來抵御攻擊者和漏洞。

-

嵌入式處理器

+關注

關注

0文章

255瀏覽量

30774 -

物聯網設備

+關注

關注

1文章

235瀏覽量

19788 -

RISC-V

+關注

關注

45文章

2314瀏覽量

46343

發布評論請先 登錄

相關推薦

UltraSoC宣布提供業界首款RISC-V處理器跟蹤IP產品

學習RISC-V入門 基于RISC-V架構的開源處理器及SoC研究

如何入門RISC-V嵌入式

讀書分享會 | 玄鐵RISC-V處理器入門與實戰電子書免費下載!

UltraSoC宣布提供業界首款RISC-V嵌入式處理器產品

RISC-V是通用RISC處理器還是可定制的處理器?

Codasip RISC-V處理器增加Veridify安全算法 增強嵌入式系統的安全性

如何構建RISC-V嵌入式

IAR Embedded Workbench將支持RISC-V太空級處理器NOEL-V

芯來科技發布超低功耗嵌入式RISC-V處理器CPU IP—NS100系列內核

專家力薦|《嵌入式系統原理與開發——基于RISC-V和Linux系統》新書發售

如何保護RISC-V上的嵌入式處理器

如何保護RISC-V上的嵌入式處理器

評論