沒有任何寄存器邏輯,RTL設(shè)計是不完整的。RTL是寄存器傳輸級或邏輯,用于描述依賴于當(dāng)前輸入和過去輸出的數(shù)字邏輯。

如果所有存儲元件均由相同的源時鐘信號觸發(fā),則稱該設(shè)計為同步設(shè)計。同步設(shè)計的優(yōu)點是總體傳播延遲等于觸發(fā)器或存儲元件的傳播延遲。STA對于同步邏輯分析非常容易,甚至可以通過使用流水線來提高性能。大多數(shù)ASIC/FPGA實現(xiàn)都使用同步邏輯。本節(jié)介紹同步計數(shù)器的設(shè)計。

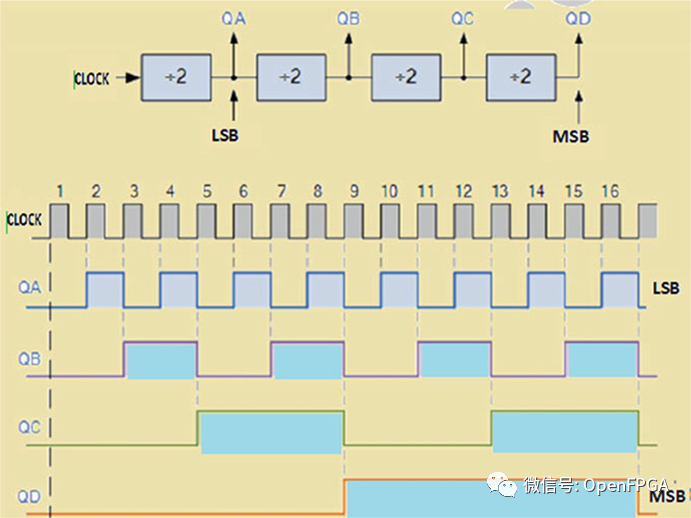

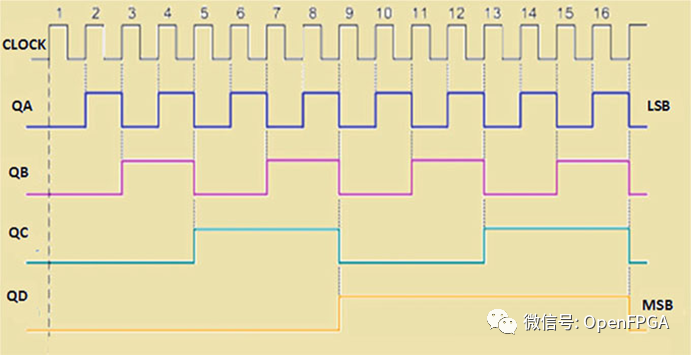

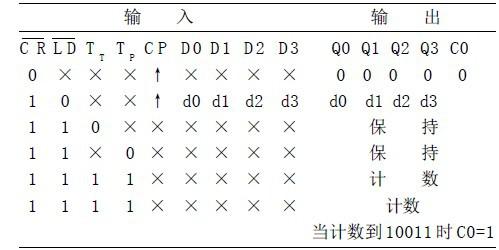

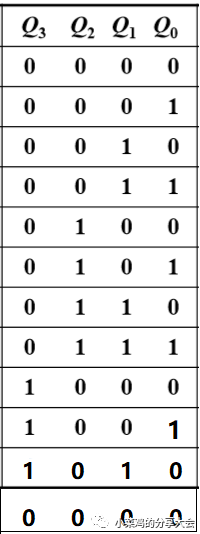

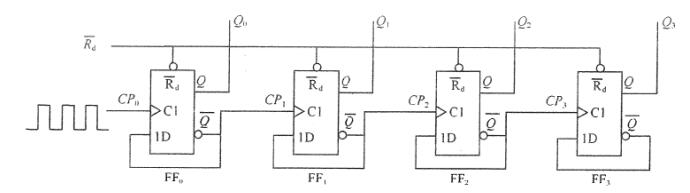

四位二進制計數(shù)器用于從“0000”到“1111”進行計數(shù),四位BCD計數(shù)器用于從“0000”到“1001”進行計數(shù)。圖5.14顯示了四位二進制計數(shù)器,其中每個階段被兩計數(shù)器分割。

圖5.14四位二進制計數(shù)器

如圖5.14所示。計數(shù)器有四條輸出線“QA、QB、QC、QD”,其中“QA”是LSB,“QD”是MSB。“QA”處的輸出在每個時鐘脈沖上切換,因此除以2。“QB”處的輸出每兩個時鐘周期切換一次,因此可被四整除,“QC”處的輸出每四個時鐘周期切換一次,因此輸出被八整除。類似地,“QD”處的輸出每8個周期切換一次,因此“QD”處的輸出除以輸入時鐘時間周期的16。在實際應(yīng)用中,計數(shù)器被用作時鐘分頻器網(wǎng)絡(luò)。在分頻綜合器中使用偶數(shù)計數(shù)器來產(chǎn)生可變頻率輸出。

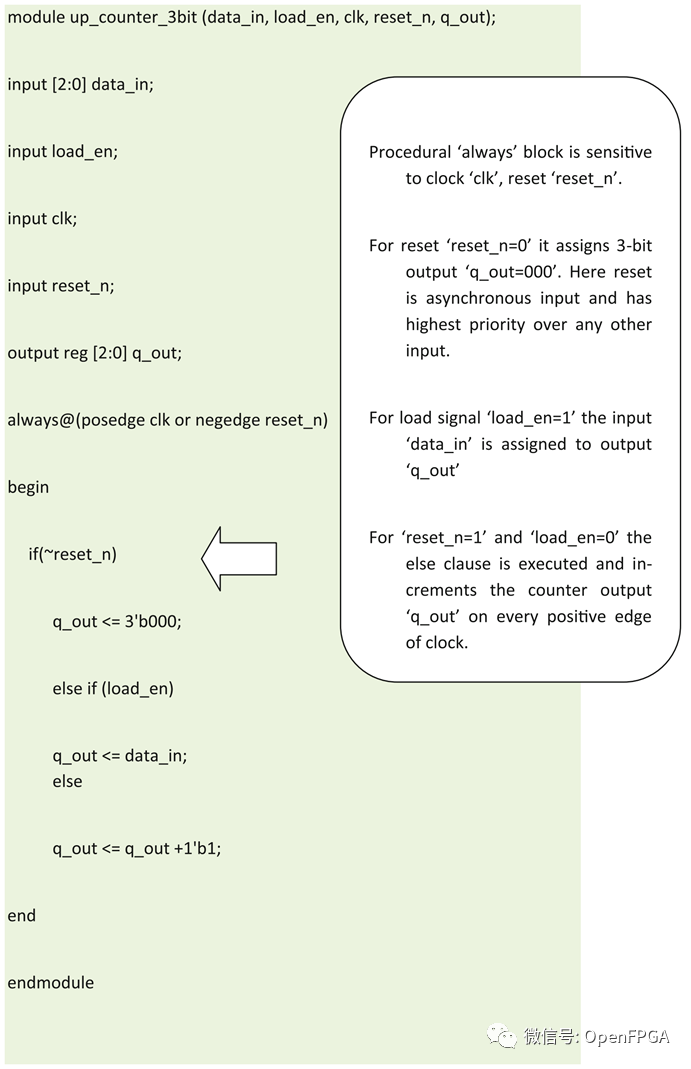

三位遞增計數(shù)器

計數(shù)器用于在時鐘的活動邊緣上生成預(yù)定義和所需的計數(shù)序列。在ASIC/FPGA設(shè)計中,使用可綜合結(jié)構(gòu)為計數(shù)器編寫有效的RTL代碼是至關(guān)重要的。用Verilog描述了三位向上計數(shù)器生成可綜合設(shè)計。計數(shù)器在時鐘的正邊緣從“000”計數(shù)到“111”,在計數(shù)的下一個正邊緣環(huán)回到“000”。示例5.7中描述的計數(shù)器是可預(yù)設(shè)的計數(shù)器,它具有同步激活的高“l(fā)oad_en”輸入,以對所需的三位預(yù)設(shè)值進行采樣。數(shù)據(jù)輸入為三位,表示為“data_in”。

計數(shù)器具有有效的低電平異步“reset_n”輸入,當(dāng)其處于低電平時,輸出到“q_out”上的狀態(tài)為“000”。在正常操作期間,“reset_n”處于高電平狀態(tài)。

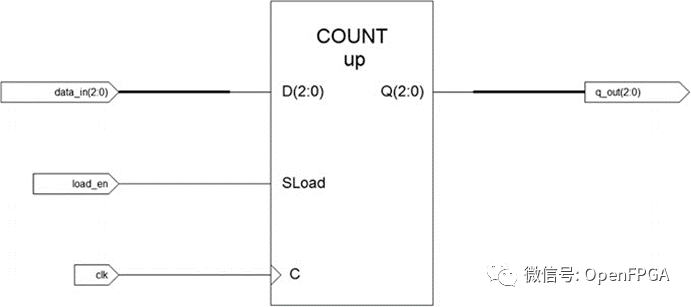

可綜合輸出如圖5.15所示,具有三位數(shù)據(jù)輸入線“data_in”、有源高電平“l(fā)oad_en”和有源低電平復(fù)位輸入“reset_n”。輸出由“q_out”和“clk”觸發(fā)的正邊緣時鐘指示。

示例5.7三位遞增計數(shù)器的Verilog RTL

圖5.15三位遞增計數(shù)器綜合頂層圖

三位遞減計數(shù)器Three-Bit Down Counter

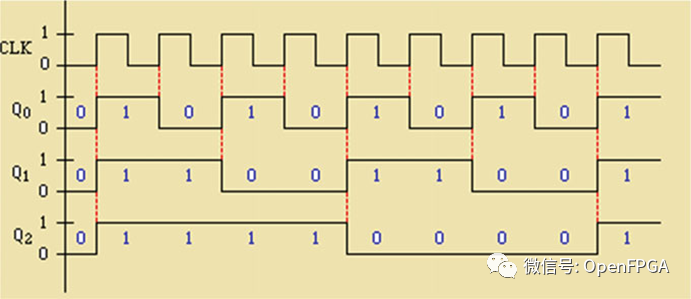

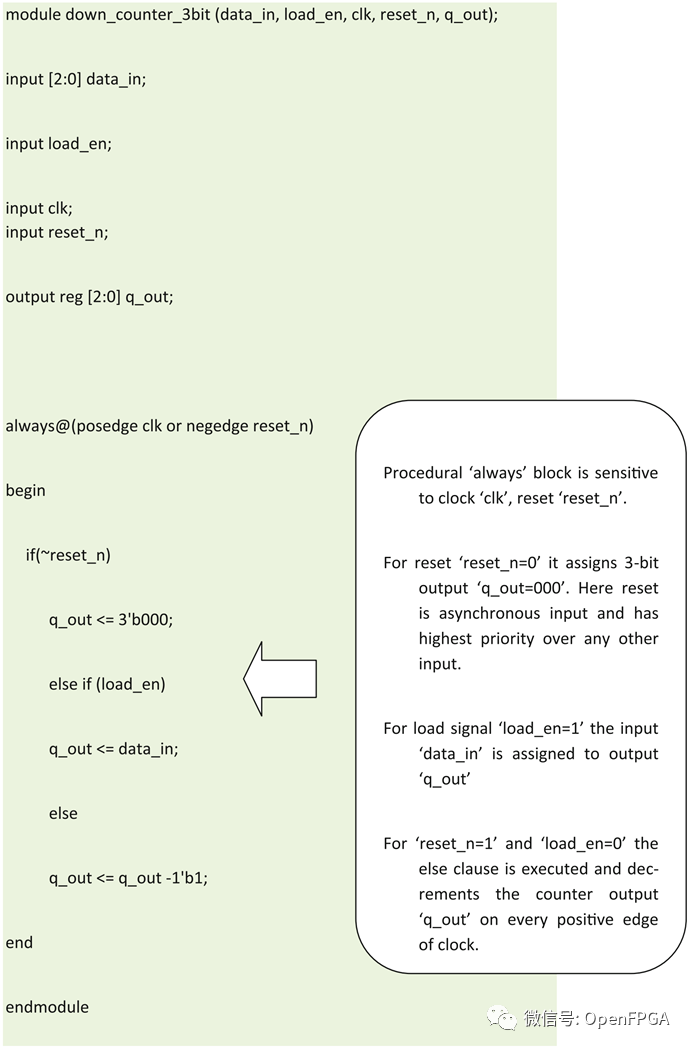

用Verilog描述了三位遞減計數(shù)器的產(chǎn)生和綜合設(shè)計。計數(shù)器從“111”計數(shù)到“000”,在時鐘的正邊緣觸發(fā),并在達到計數(shù)值“000”后在計數(shù)的下一個正邊緣環(huán)回到“111”。三位遞減計數(shù)器的時序如圖5.16所示。

示例5.9中描述的計數(shù)器是可預(yù)設(shè)計數(shù)器,它具有同步激活的高“l(fā)oad_en”輸入,用于采樣三位所需的可預(yù)設(shè)值。數(shù)據(jù)輸入為三位,表示為“data_in”。

圖5.16三位二進制遞減計數(shù)器的時序

示例5.8三位遞減計數(shù)器的Verilog RTL

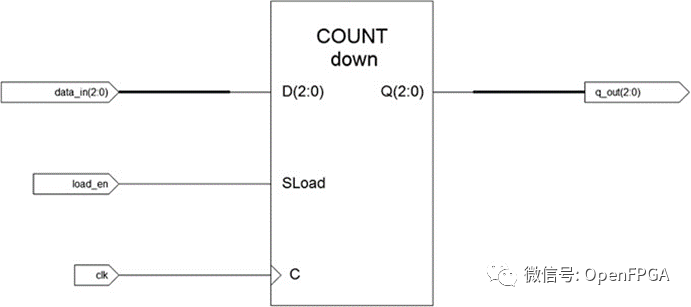

圖5.17綜合三位遞減計數(shù)器頂層圖

計數(shù)器具有低電平異步“reset_n”輸入,當(dāng)其處于低電平時,輸出“q_out”上的狀態(tài)為“000”。在正常操作期間,“reset_n”處于高電平狀態(tài)。

可綜合輸出如圖5.17所示,具有三位數(shù)據(jù)輸入線“data_in”、有源高電平“l(fā)oad_en”和有源低電平復(fù)位輸入“reset_n”。輸出由“q_out”和“clk”觸發(fā)的正邊緣時鐘指示。

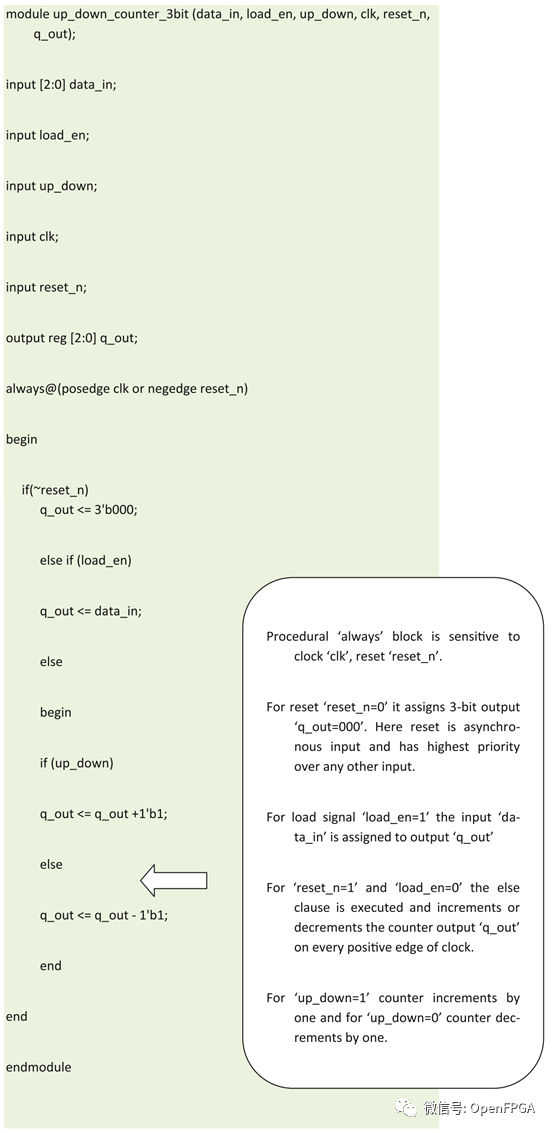

三位增、減計數(shù)器

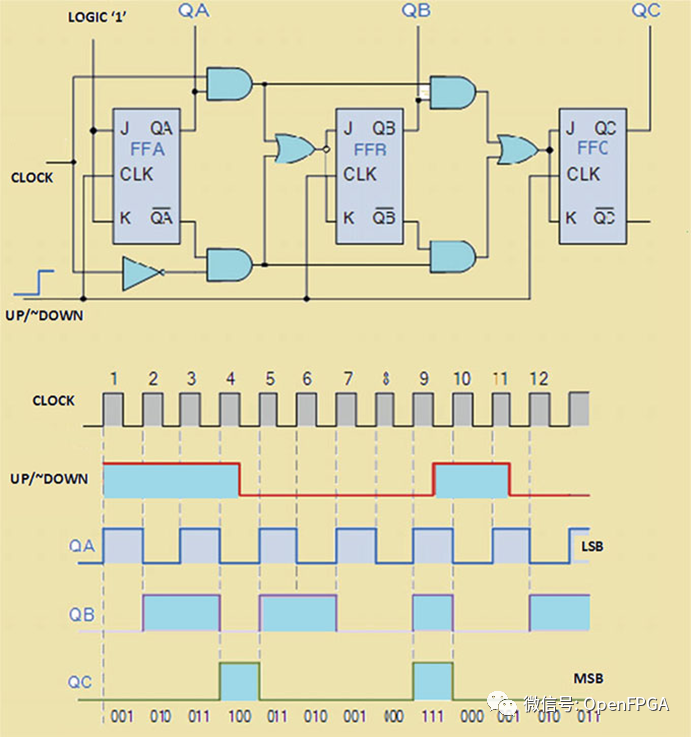

用Verilog描述了三位增、減計數(shù)器產(chǎn)生的可綜合時序設(shè)計。遞減計數(shù)器計數(shù)從“111”到“000”,在時鐘的正邊緣觸發(fā),并在達到計數(shù)值“000”后,在計數(shù)的下一個正邊緣環(huán)回到“111”。遞增計數(shù)器從“000”計數(shù)到“111”,在時鐘的正邊緣觸發(fā),并在達到計數(shù)值“000”后在計數(shù)的下一個正邊緣環(huán)回到“000”。

圖5.18給出了三位二進制增、減計數(shù)器的內(nèi)部結(jié)構(gòu)。對于UP/DOWN等于邏輯“1”,計數(shù)器充當(dāng)遞增計數(shù)器,對于UP/DOWN等于“0”,計數(shù)器充當(dāng)遞減計數(shù)器。

示例5.9中描述的計數(shù)器是可預(yù)設(shè)計數(shù)器,它具有同步激活的高“l(fā)oad_en”輸入,用于采樣三位所需的可預(yù)設(shè)值。數(shù)據(jù)輸入為三位,表示為“data_in”。遞增或遞減計數(shù)操作由輸入“up_down”選擇,“up_down=1”計數(shù)器用作向上/遞減計數(shù)器,“up_down=0”計數(shù)器用作向下/遞減計數(shù)器。

計數(shù)器具有有效的低電平異步“reset_n”輸入,當(dāng)其處于低電平時,輸出“q_out”上的狀態(tài)為“000”。在正常操作期間,“復(fù)位”處于高電平狀態(tài)(示例5.9)。

圖5.18三位遞增、遞減計數(shù)器

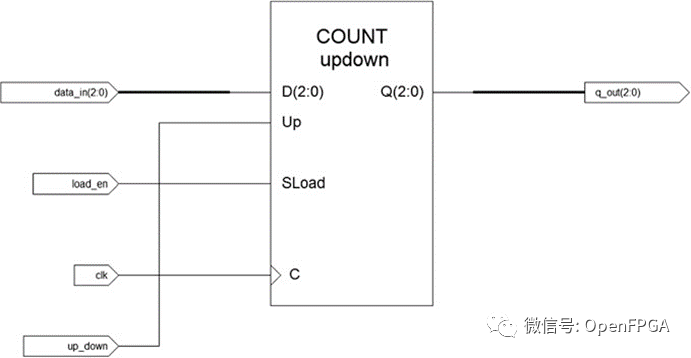

可綜合輸出如圖5.19所示,具有三位數(shù)據(jù)輸入線“data_in”、有源高電平“l(fā)oad_en”和有源低電平復(fù)位輸入“reset_n”。輸出由“q_out”和“clk”觸發(fā)的正邊緣時鐘指示,選擇行為“up_down”。

示例5.9三位遞增、遞減計數(shù)器的Verilog RTL

圖5.19三位遞增、遞減計數(shù)器頂層綜合模塊

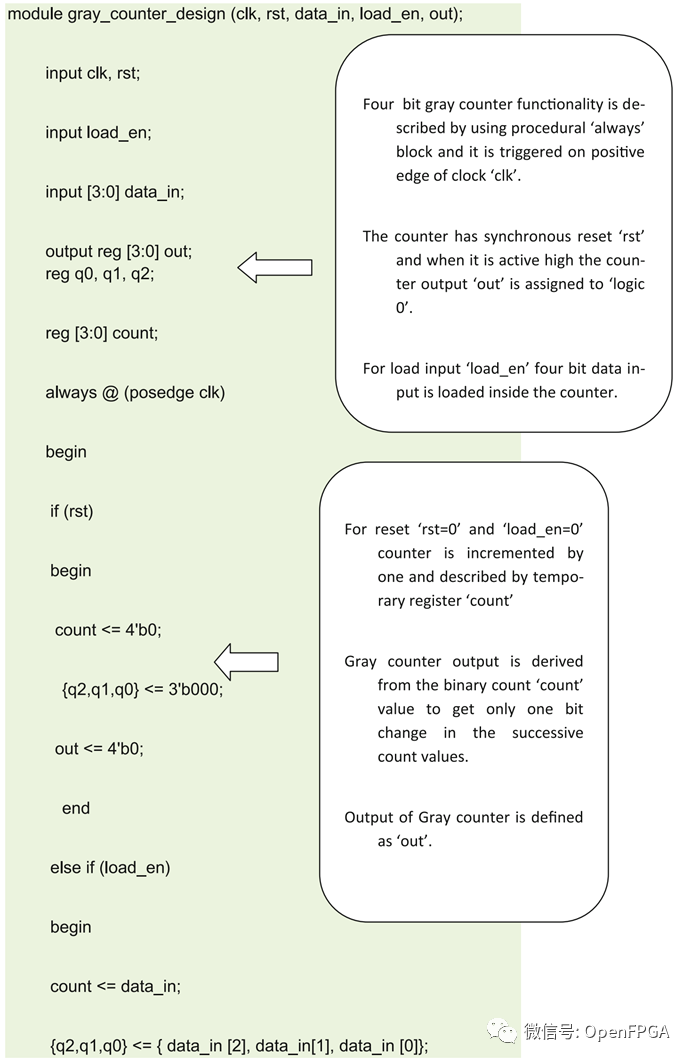

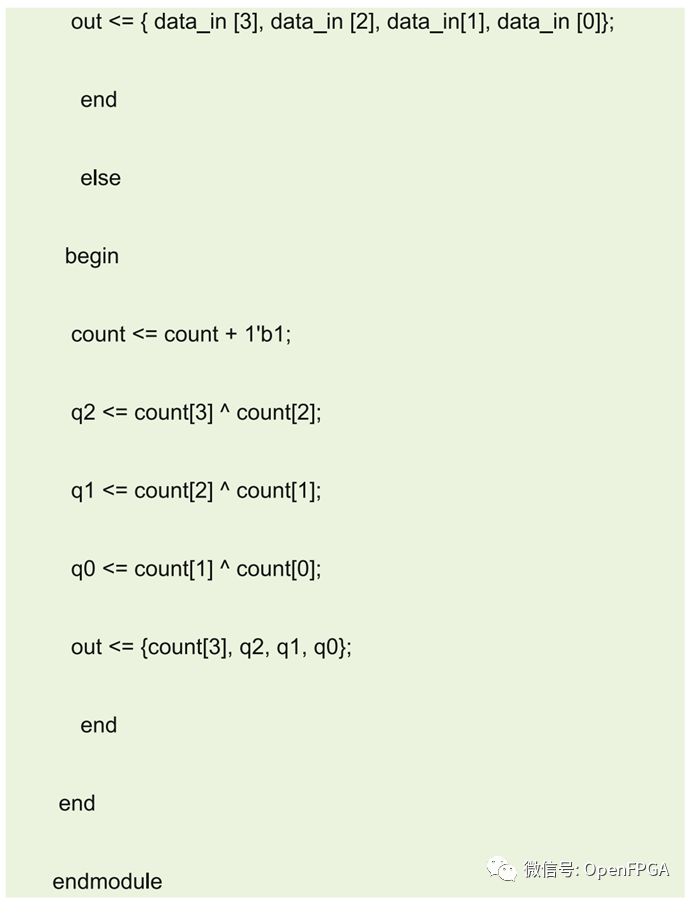

格雷碼計數(shù)器Gray Counters

格雷碼計數(shù)器用于多時鐘域設(shè)計中,因為時鐘邊沿上只有一位發(fā)生變化。同步器中也會使用格雷碼。

該示例中描述了格雷碼計數(shù)器,在該示例中,相對于計數(shù)器的先前輸出,活動時鐘邊緣上只有一位發(fā)生變化。在這種情況下,高電平復(fù)位輸入為“rst”。當(dāng)“rst=1”時,計數(shù)器“out”的輸出賦值給“0000”。

示例5.10中描述的計數(shù)器是可預(yù)設(shè)計數(shù)器,它具有同步激活的高“l(fā)oad_en”輸入,用于采樣四位所需的可預(yù)設(shè)值。數(shù)據(jù)輸入為四位,表示為“data_in”。

計數(shù)器具有激活的高電平異步復(fù)位“rst”輸入,當(dāng)它處于激活的高電平時,輸出行“out”上的狀態(tài)為“0000”。正常運行期間,“rst”處于低電平狀態(tài)。

示例5.10四位Gray計數(shù)器

格雷碼和二進制計數(shù)器

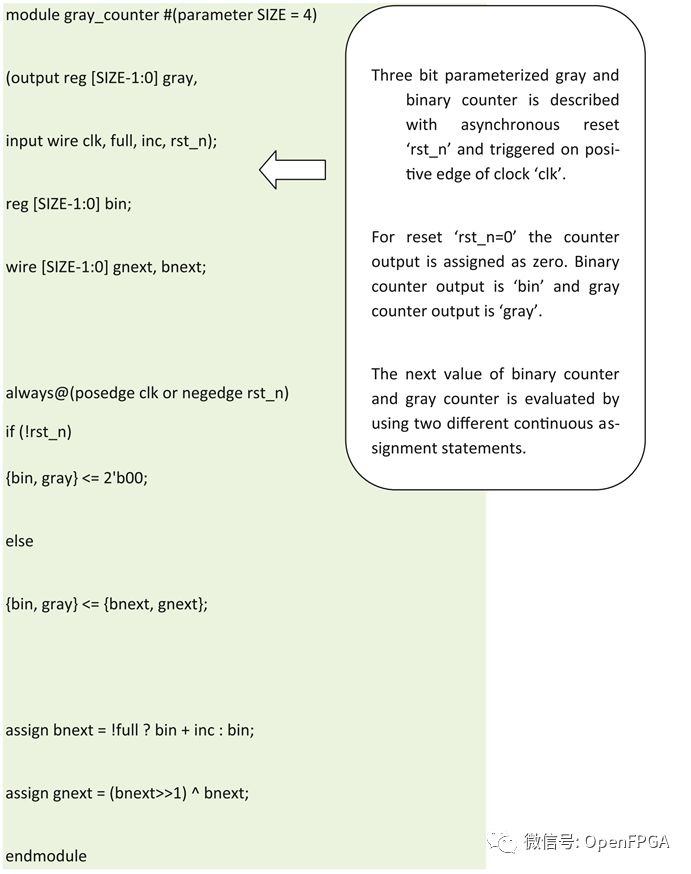

在大多數(shù)實際應(yīng)用中,需要使用二進制和格雷碼計數(shù)器。通過使用組合邏輯,可以從二進制計數(shù)器輸出生成格雷碼計數(shù)器。有關(guān)二進制到格雷碼和格雷碼到二進制代碼轉(zhuǎn)換器,請參閱前面文章。

示例中描述了參數(shù)化二進制和格雷碼計數(shù)器,并描述了Verilog RTL以生成四位二進制和格雷碼輸出。對于“rst_n=0”,二進制和格雷碼計數(shù)器輸出賦值為“0000”。四位格雷碼輸出表示為“gray”(示例5.11)。

四位二進制計數(shù)器的模擬結(jié)果如下面的時序圖5.20所示,并且對于時鐘計數(shù)器的每個正邊緣,輸出增量為1。

示例5.11參數(shù)化二進制和格雷碼計數(shù)器的Verilog RTL

圖5.20四位二進制計數(shù)器的時序

環(huán)形計數(shù)器Ring Counters

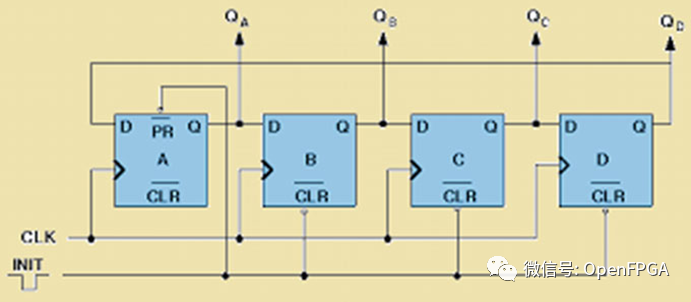

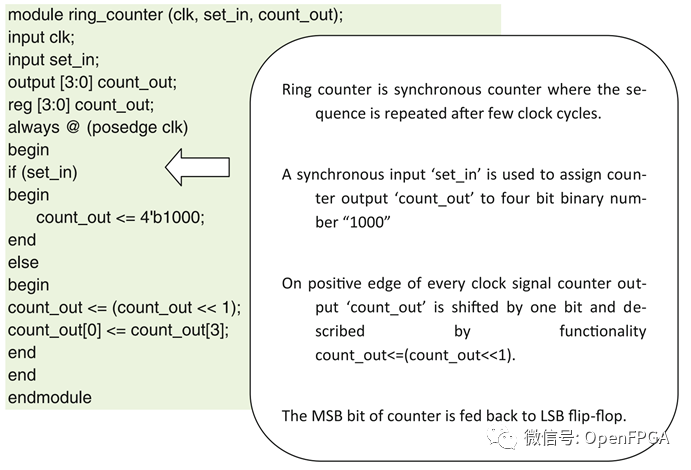

實際應(yīng)用中使用環(huán)形計數(shù)器來提供預(yù)定義的延遲。這些計數(shù)器本質(zhì)上是同步的,以引入一定量的預(yù)定義延遲,并用于實際應(yīng)用中,如交通燈控制器、定時器。圖5.21顯示了四位環(huán)形計數(shù)器使用D觸發(fā)器的內(nèi)部邏輯結(jié)構(gòu),如圖所示,MSB觸發(fā)器的輸出反饋到LSB觸發(fā)器輸入,計數(shù)器在時鐘信號的每個活動邊上移動數(shù)據(jù)。

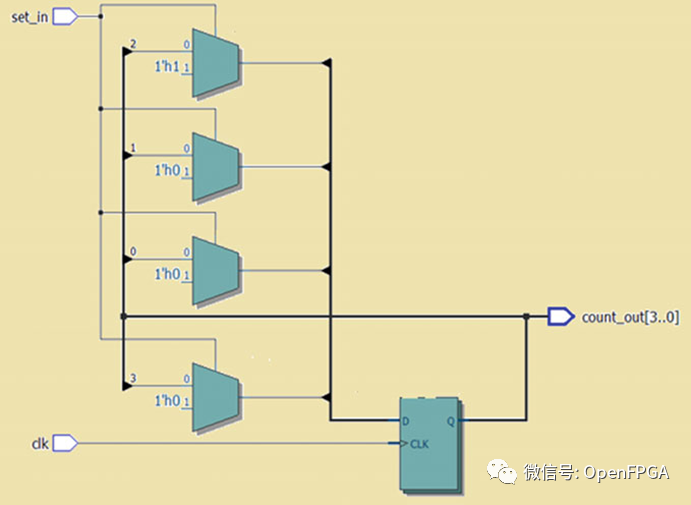

示例5.12中描述了四位環(huán)形計數(shù)器的Verilog RTL,計數(shù)器具有“set_in”輸入,以將輸入初始化值設(shè)置為“1000”,并在時鐘信號的正邊緣工作。

綜合邏輯如圖5.22所示。

圖5.21環(huán)形計數(shù)器內(nèi)部結(jié)構(gòu)

示例5.12四位環(huán)形計數(shù)器的Verilog RTL

圖5.22四位環(huán)形計數(shù)器的綜合邏輯

約翰遜計數(shù)器Johnson Counters

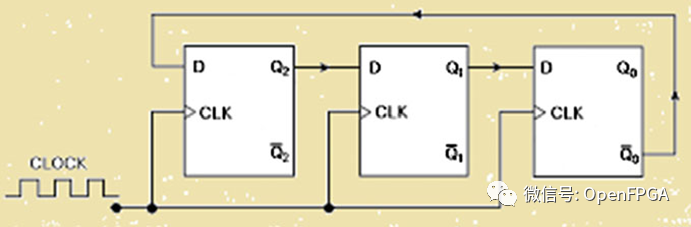

約翰遜計數(shù)器是一種特殊類型的同步計數(shù)器,采用移位寄存器設(shè)計。三位約翰遜計數(shù)器的內(nèi)部結(jié)構(gòu)如圖5.23所示。

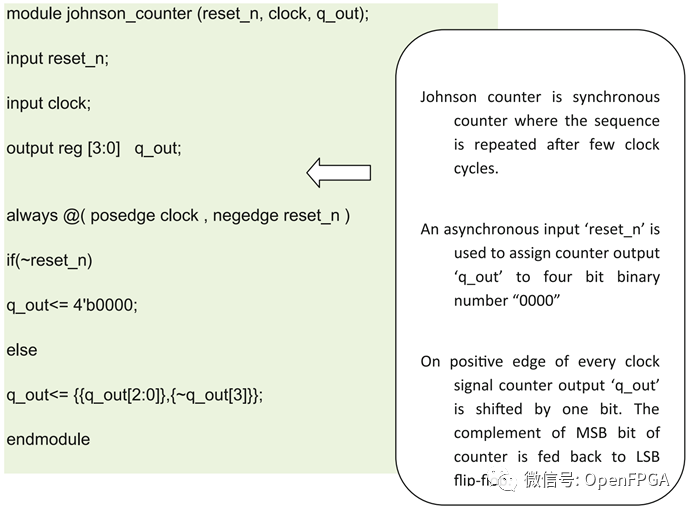

四位約翰遜計數(shù)器的Verilog RTL如例5.13所示。

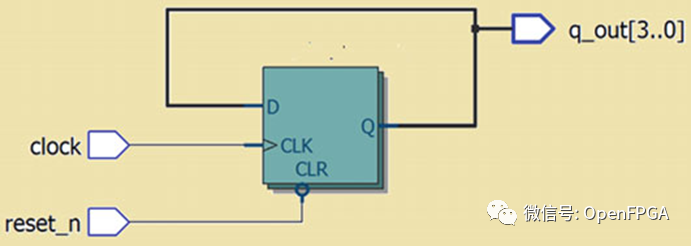

綜合邏輯如圖5.24所示。

圖5.23三位約翰遜計數(shù)器

示例5.13四位約翰遜計數(shù)器的Verilog RTL

圖5.24四位約翰遜計數(shù)器的綜合邏輯

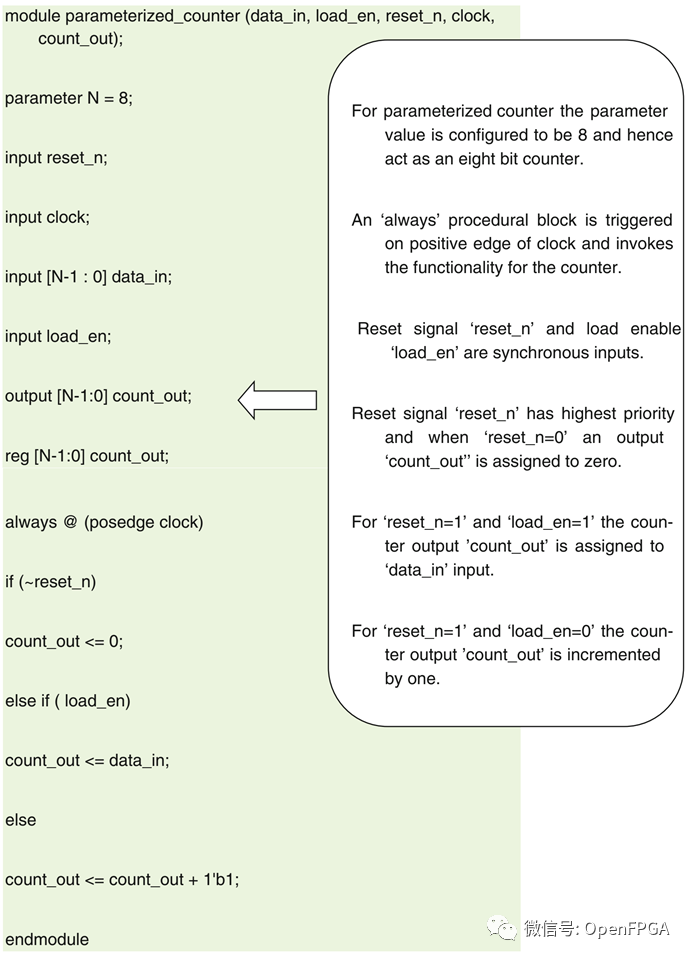

參數(shù)化計數(shù)器

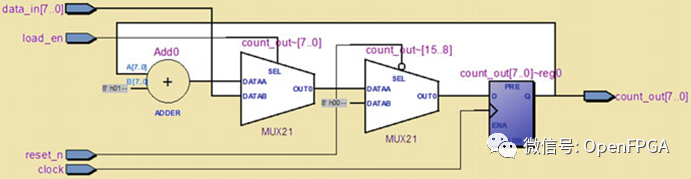

在實際應(yīng)用中,為了提高計數(shù)器的可讀性和可重用性,通過定義參數(shù)來設(shè)計計數(shù)器。參數(shù)整數(shù)值可用于定義計數(shù)器的位數(shù)。8位參數(shù)化計數(shù)器的Verilog RTL如圖5.25所示。

參數(shù)化計數(shù)器的可綜合頂層模塊如圖5.26所示。

圖5.25八位參數(shù)化計數(shù)器的Verilog RTL

圖5.26參數(shù)化計數(shù)器的綜合邏輯

審核編輯:郭婷

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

120952 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110267 -

計數(shù)器

+關(guān)注

關(guān)注

32文章

2261瀏覽量

94877

原文標(biāo)題:Verilog時序邏輯硬件建模設(shè)計(三)同步計數(shù)器

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

中規(guī)模集成時序邏輯設(shè)計

移位型計數(shù)器中反饋邏輯電路的設(shè)計

時序邏輯電路

基于MSI的N進制計數(shù)器設(shè)計方法

基于Multisim的計數(shù)器設(shè)計仿真

計數(shù)器及時序電路

采用中規(guī)模集成計數(shù)器進行任意進制計數(shù)器設(shè)計的解決方案

同步計數(shù)器和異步計數(shù)器是什么 同步計數(shù)器和異步計數(shù)器的主要區(qū)別?

時序邏輯電路設(shè)計之計數(shù)器

時序邏輯電路設(shè)計之異步計數(shù)器

Verilog時序邏輯中同步計數(shù)器的功能和應(yīng)用

Verilog時序邏輯中同步計數(shù)器的功能和應(yīng)用

評論