使用Verilog可以方便地實現復雜的設計。現在,設計復雜性增加,設計需要針對低功率、高速和最小面積進行優化~

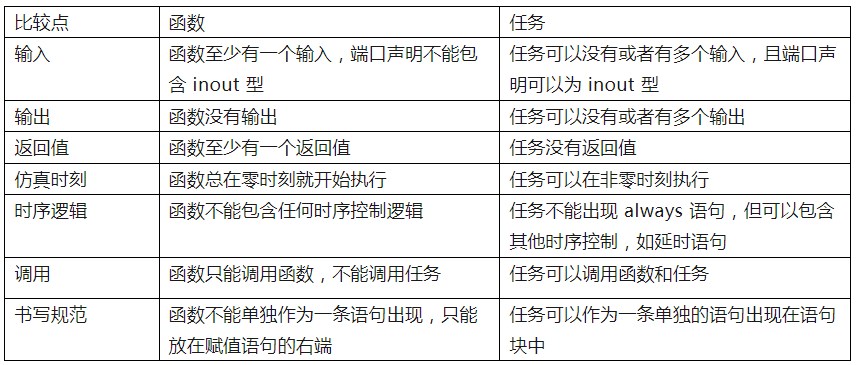

任務和函數在Verilog中用于描述常用的功能行為。與其在不同的地方復制相同的代碼,不如根據需求使用函數或任務,這是一種良好且常見的做法。為了便于代碼維護,最好使用子例程之類的函數或任務。

從給定字符串中計算1的個數

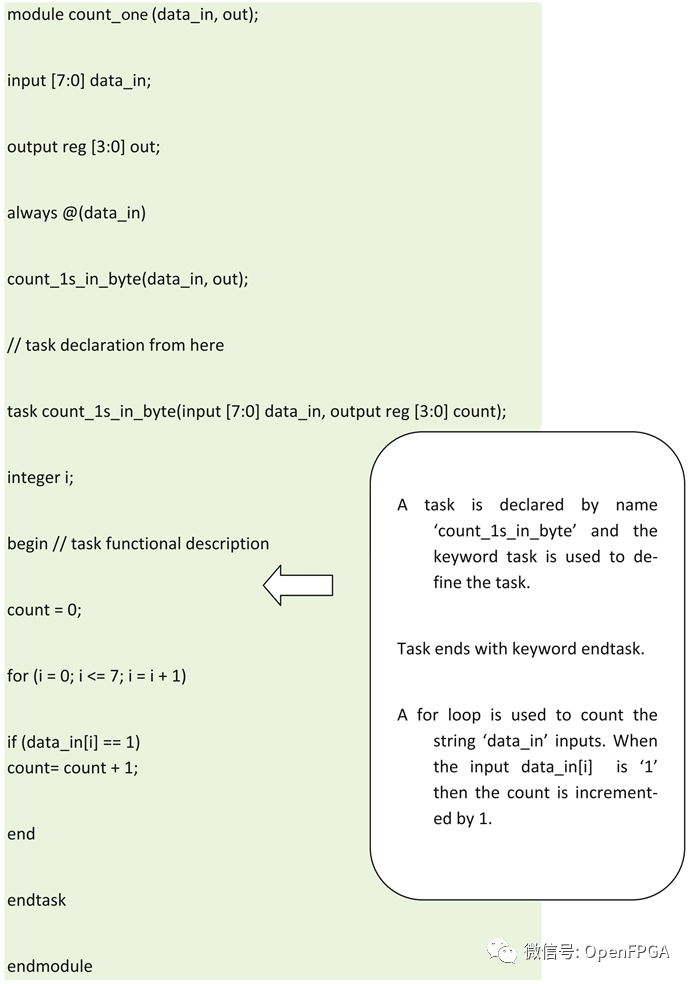

以下示例描述用于從給定字符串中計算1的個數任務。以下是使用任務時需要記住的要點:

任務可以由時間控制語句甚至延遲操作符組成。

任務可以有輸入和輸出聲明。

任務可以由函數調用組成,但函數不能由任務組成。

任務可以有輸出參數,在調用時不用于返回值。

任務可用于調用其他任務。

在編寫可綜合RTL時,不建議使用任務。

任務用于編寫行為或可仿真模型。

示例7.6是從給定字符串中計算1的個數的說明。在本例中,任務與參數“data_in”、“out”一起使用,任務的名稱為“count_1s_in_byte”。在大多數協議描述中,需要對輸入字符串執行一些操作。在此示例中,字符串為8位輸入“data_in”,輸出結果為4位“out”。不建議使用任務生成綜合邏輯。

示例7.6任務的Verilog RTL

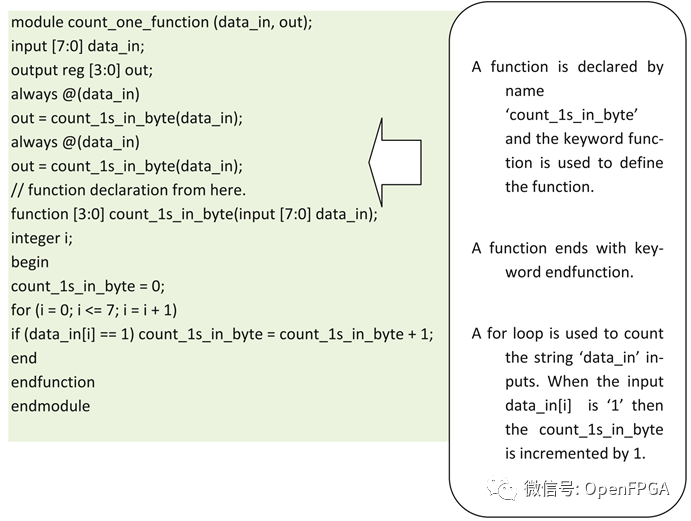

使用函數計數1的個數的模塊

以下示例描述用于從給定字符串中計算1的個數函數。以下是使用該功能時需要記住的要點:

函數不能由時間控制語句甚至延遲運算符組成。

函數至少有一個輸入參數聲明。

函數可以由函數調用組成,但函數不能由任務組成。

函數在零模擬時間內執行,并在調用時返回單個值。

在編寫可綜合 RTL時,不建議使用函數。

函數用于編寫行為或可仿真模型。

函數不應具有非阻塞賦值。

示例7.7是從給定字符串中計算1個數的說明。在本例中,函數與參數“data_in”一起使用。函數名為“count_1s_in_byte”。在大多數協議描述中,需要對輸入字符串執行一些操作。在此示例中,字符串為8位輸入“data_in”,輸出結果為4位“out”。不建議使用該函數生成綜合邏輯。

審核編輯:郭婷

-

Verilog

+關注

關注

28文章

1351瀏覽量

110267

原文標題:Verilog復雜邏輯設計指南-函數和任務

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于verilog中的生成塊和任務

深入分析uCOS的任務堆棧

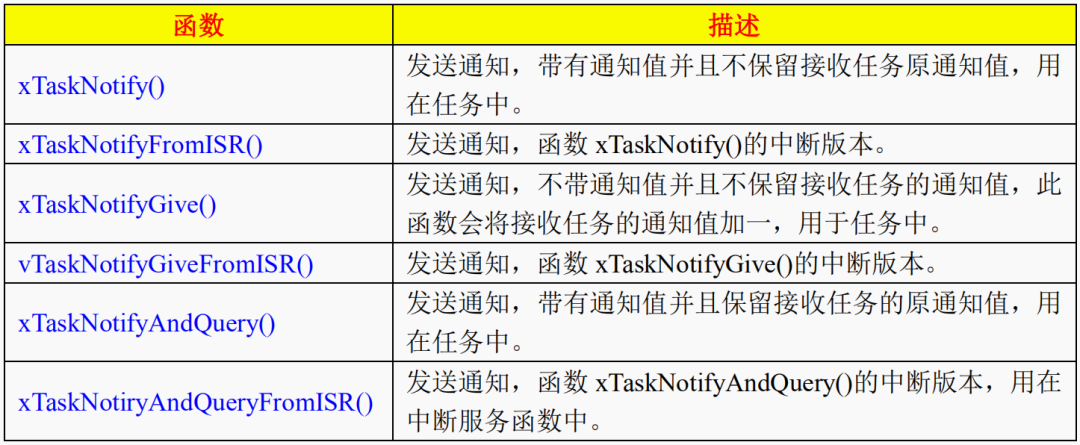

FreeRTOS任務應用函數介紹

Verilog HDL語言中任務與函數的比較

Verilog數字系統設計——任務和函數二(系統任務readmemb或readmemh)

Verilog數字系統設計——任務和函數一(斐波那契數列)

Verilog設計中函數和任務的作用分析

Verilog設計中函數和任務的作用分析

評論