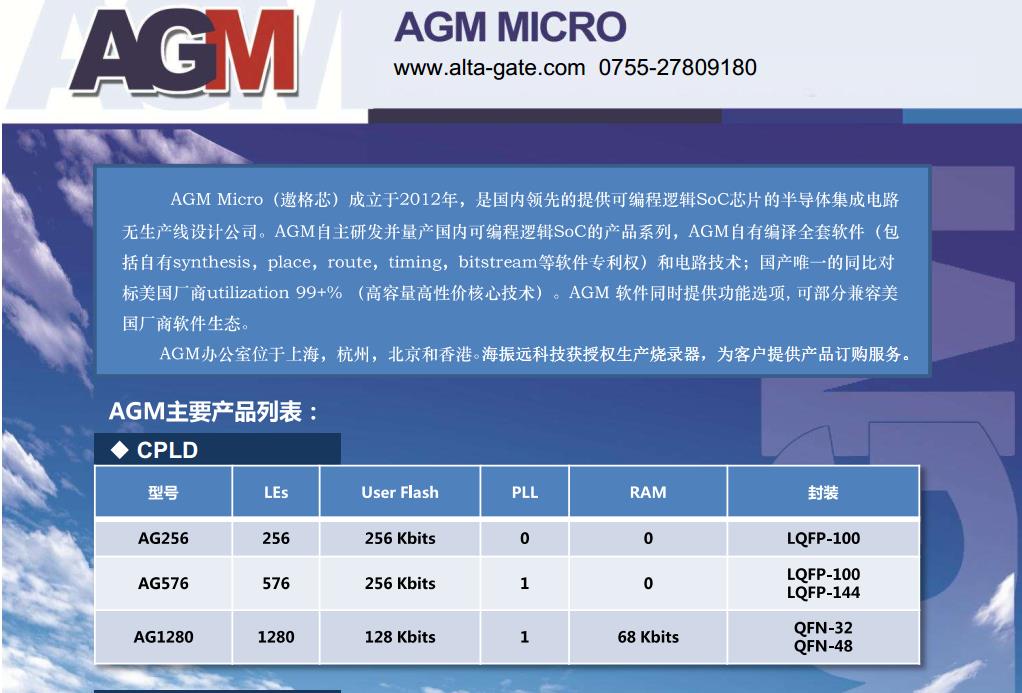

上海遨格芯微電子有限公司(AGM)成立于2012年,是國內領先的以可編程邏輯技術為基礎, 提供應用市場SoC芯片的半導體集成電路無生產線設計公司。由來自美國硅谷知名可編程邏輯 SoC 企業的團隊和國內資深工程團隊創辦。

AGM自主研發并量產國內可編程邏輯SoC的產品系列應用于工業,消費類,和人工智能等應用SoC市場,擁有OEM, 客戶,和合作方的認證,并在自有編譯全套軟件(包括自有synthesis, place, route, timing, bitstream 等軟件) 和電路擁有自主知識產權。并授權海振遠科技生產和推廣AGM FPGA開發板和脫機燒錄器,為客戶提供快速的本地化服務和支持。

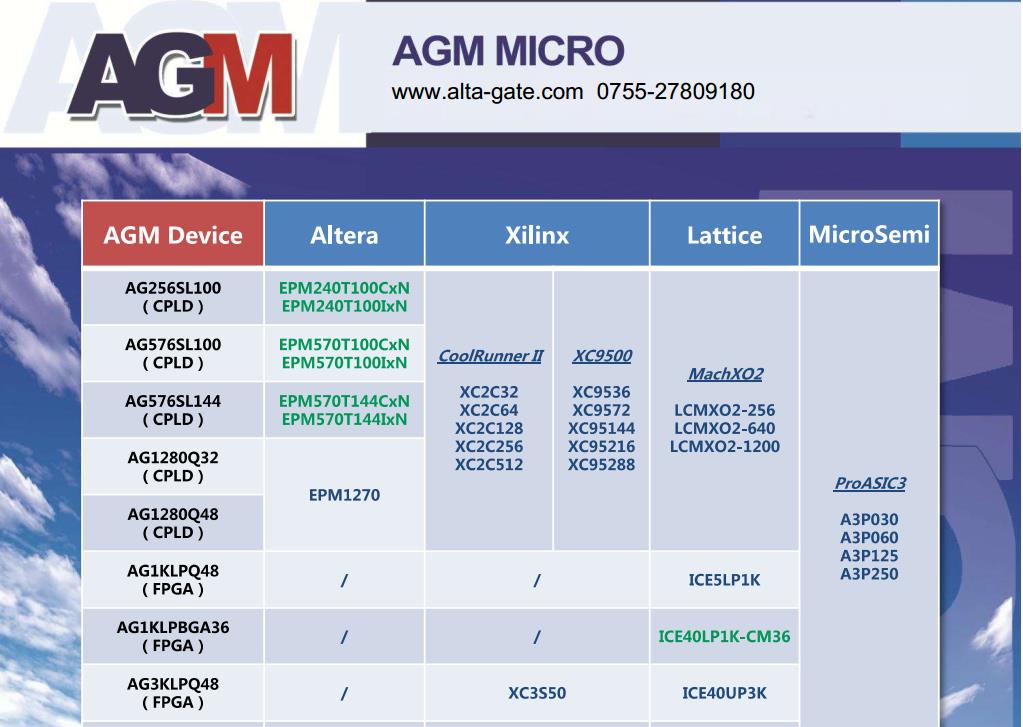

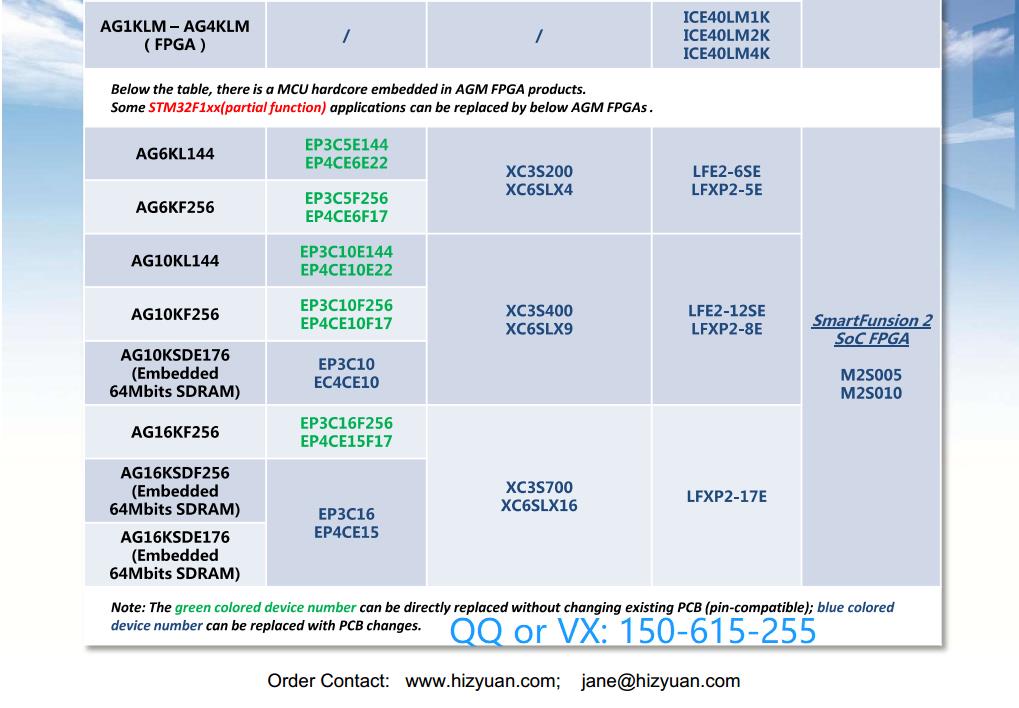

一、器件替代資源對照表

AGM FPGA可以pin to pin 兼容altera的型號(CPLD/FPGA),不用修改硬件,可以直接替換。以下是部分型號提貨對照。

AG256SL100 完全兼容替換 EPM240T100C

AG256SL100 完全兼容替換 EPM240T100I

AG576SL100 完全兼容替換 EPM570T100C

AG576SL100 完全兼容替換 EPM570T100I

AG576SL144 完全兼容替換 EPM570T144C

AG576SL144 完全兼容替換 EPM570T144I

AG6KL144 完全兼容替換 EP3C5E144

AG6KL144 完全兼容替換 EP4C6E22

AG6KF256 完全兼容替換 EP3C5F256

AG6KF256 完全兼容替換 E4CE6F17

AG10KL144 完全兼容替換 EP3C10E144

AG10KL144 完全兼容替換 EP4CE10E22

AG10KF256 完全兼容替換 EP3C10F256

AG10KF256 完全兼容替換 EP4CE10F17

AG16KF256 完全兼容替換 EP3C16F256

AG16KF256 完全兼容替換 EP4CE15F17

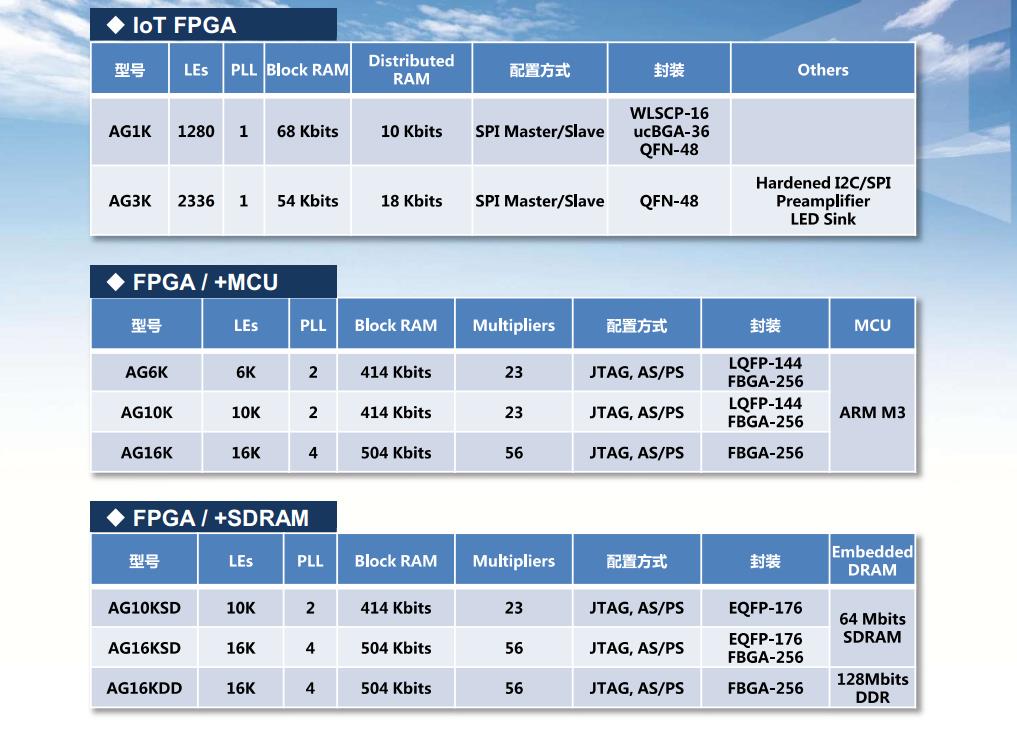

以下是器件的資源對照表:

二、AGM CPLD 應用指南

1、軟件流程選擇

Supra 共有 3 種開發 Mode: Native 選項(AGM 自有 EDA 綜合工具), Synplicity 選項(第三

方綜合工具,例如 Synplify, Mentor 等), Compatible 選項(兼容 Altera Quartus II 的綜合工

具)。

文檔中的 Supra 主要基于 Quartus II 綜合的設計流程,其它工具設計流程類似。

2、AG576 IO

AG576SL100 的可用 IO 與 AG256SL100 一致, 比 Altera EPM570T100 多 4 個 IO,分別為:

| Device | Pin_39 | Pin_88 | Pin_37 | Pin_90 |

| EPM570T100 Pin | VCCINT | VCCINT | GNDINT | GNDINT |

| AG576SL100 Pin | IO | IO | IO | IO |

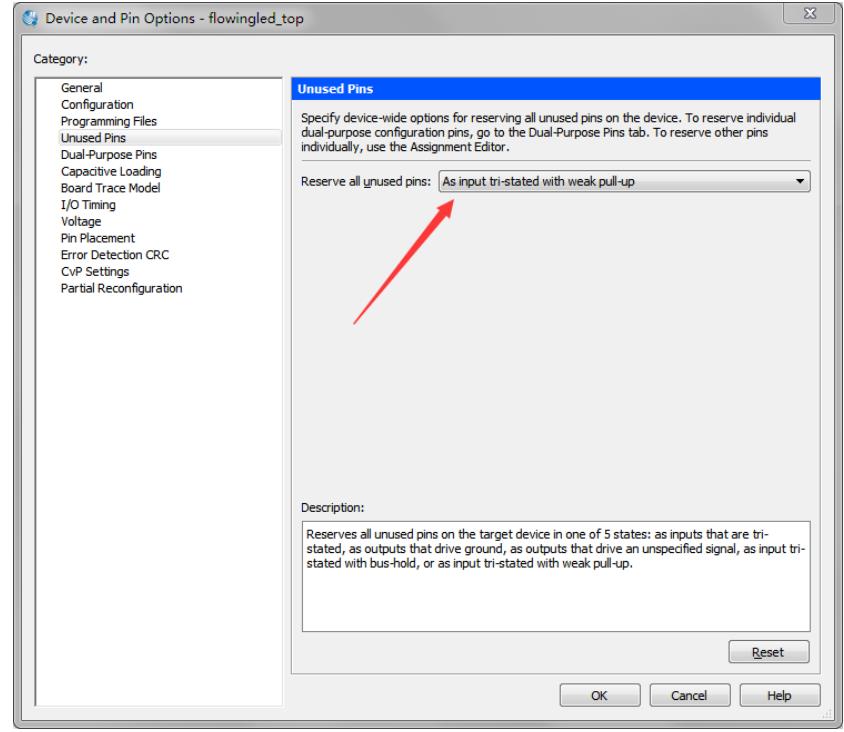

如果 PCB 兼容 EPM570,39/88 接 3.3V 供電的話,有可能會使芯片輸入 IO 電流較大。可以通

過設置,使 AG576 的未用 IO 為三態模式。請在 EPM570 的原設計中設置 Unused Pin 選項為

AS input tri-stated with weak pull-up。如下圖:

如果希望利用 AG576 多的 4 個 IO,可以在 asf 文件中加入對這 4 個 pin 的分配,如:set_location_assignment PIN_88 -to abc

安全位設置

AG256/576 安全位(SECURITY_BIT)可以使 CPLD 燒寫好后,無法讀取出內部程序,只能擦除或覆蓋,從而實現用戶設計的安全性。

審核編輯:符乾江

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605302 -

AGM

+關注

關注

0文章

86瀏覽量

17111

發布評論請先 登錄

相關推薦

Altera正式獨立運營:FPGA行業格局將迎來新變局

采用Xilinx FPGA的AFE79xx SPI啟動指南

【米爾-Xilinx XC7A100T FPGA開發板試用】+01.開箱(zmj)

FPGA芯片國產替代性價比凸顯,Altera漲價在即,Xilinx繼去年大幅漲價后,12月繼續大幅調漲價格,成熟產品尤甚

國產FPGA的發展前景是什么?

科普 | 一文了解FPGA

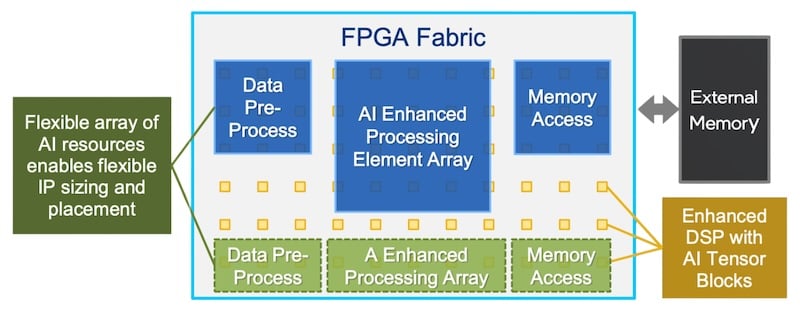

Altera將AI注入新的中端FPGA

英特爾旗下FPGA公司Altera正式亮相

Xilinx fpga芯片系列有哪些

中端FPGA成為主戰場,Altera獨立后的市場格局

昨天看到消息Altera從Intel獨立出來了,不知道大家常用的FPGA是什么?

MABA-007159-000000的PINTOPIN國產替代 CH-BMA-7159-MA PDF資料

FPGA產業的興起與發展

國產FPGA, 兼容替代ALTERA, XILINX資料詳解

國產FPGA, 兼容替代ALTERA, XILINX資料詳解

評論