關(guān)于Cache的其它內(nèi)容

上面我們所描述情況,在訪問cache前,已經(jīng)將虛擬地址轉(zhuǎn)換成了物理地址,其實,不一定,也可是是虛擬地址直接訪問cache,倒底是使用物理地址還是虛擬地址,這就是翻譯方式的選擇。

(1)虛緩存

一個簡單的方案就是緩存的標(biāo)簽和索引均使用虛擬地址。這種緩存稱為虛緩存(virtualcache)。這種緩存的優(yōu)點是僅在緩存失效時才需要進行頁面翻譯。由于緩存命中率很高,需要翻譯的次數(shù)也相對較少。

但是這種技術(shù)也存在嚴(yán)重的問題。

第一,引入虛擬地址的一個重要原因是在軟件(操作系統(tǒng))級進行頁面保護,以防止進程間相互侵犯地址空間。由于這種保護是通過頁表和翻譯旁視緩沖器(TLB)中的保護位(protectionbit)實現(xiàn)的,直接使用虛擬地址來訪問數(shù)據(jù)等于繞過了頁面保護。一個解決辦法是在緩存失效時查看TLB對應(yīng)表項的保護位以確定是否可以加載缺失的數(shù)據(jù)。

第二,由于不同進程使用相同的虛擬地址空間,在切換進程后會出現(xiàn)整個緩存都不再對應(yīng)新進程的有效數(shù)據(jù)。如果前后兩個進程使用了相同的地址區(qū)間,就可能會造成緩存命中,確訪問了錯誤的地址,導(dǎo)致程序錯誤。有兩個解決辦法:其一,進程切換后清空緩存。代價過高。其二,使用進程標(biāo)識符(PID)作為緩存標(biāo)簽的一部分,以區(qū)分不同進程的地址空間。

第三,別名問題(Alias)。由于操作系統(tǒng)可能允許頁面別名,即多個虛擬頁面映射至同一物理頁面,使用虛擬地址做標(biāo)簽將可能導(dǎo)致一份數(shù)據(jù)在緩存中出現(xiàn)多份拷貝的情形。這種情況下如果對其中一份拷貝作出修改,而其他拷貝沒有同步更新,則數(shù)據(jù)喪失整合性,導(dǎo)致程序錯誤。有兩個解決辦法:其一,硬件級反別名。當(dāng)緩存載入目標(biāo)數(shù)據(jù)時,確認(rèn)緩存內(nèi)沒有緩存塊的標(biāo)簽是此地址的別名。如果有則不載入,而直接返回別名緩存塊內(nèi)的數(shù)據(jù)。其二,頁面著色(PageColoring)。這種技術(shù)是由操作系統(tǒng)對頁面別名作出限制,使指向同一頁面的別名頁面具有相同的低端地址。這樣,只要緩存的索引范圍足夠小,就能保證在緩存中決不會出現(xiàn)來自不同別名頁面的數(shù)據(jù)。

第四,輸入輸出問題。由于輸入輸出系統(tǒng)通常只使用物理地址,虛緩存必須引入一種逆映射技術(shù)來實現(xiàn)虛擬地址到物理地址的轉(zhuǎn)換。

(2)實緩存

實緩存(physicalcache)完全使用物理地址做緩存塊的標(biāo)簽和索引,故地址翻譯必須在訪問緩存之前進行。這種傳統(tǒng)方法所以可行的一個重要原因是TLB的訪問周期非常短(因為本質(zhì)上TLB也是一個緩存),因而可以被納入流水線。

但是,由于地址翻譯發(fā)生在緩存訪問之前,會比虛緩存更加頻繁地造成TLB。(相比之下,虛緩存僅在本身失效的前提下才會訪問TLB,進而有可能引發(fā)TLB失效)實緩存在運行中存在這樣一種可能:首先觸發(fā)了一個TLB失效,然后從頁表中更換TLB表項(假定頁表中能找到)。然后再重新訪問TLB,翻譯地址,最后發(fā)現(xiàn)數(shù)據(jù)不在緩存中。

(3)虛索引、實標(biāo)簽緩存

一個折中方案是同時使用虛索引和實標(biāo)簽(virtuallyindexed, physically tagged)。這種緩存利用了頁面技術(shù)的一個特征,即虛擬地址和物理地址享有相同的頁內(nèi)偏移值(pageoffset)。這樣,可以使用頁內(nèi)偏移作為緩存索引,同時使用物理頁面號作為標(biāo)簽。這種混合方式的好處在于,其既能有效消除諸如別名引用等純虛緩存的固有問題,又可以通過對TLB和緩存的并行訪問來縮短流水線延遲。

這種技術(shù)的一個缺點是,在使用直接匹配緩存的前提下,緩存大小不能超過頁面大小,否則頁面偏移范圍就不足以覆蓋緩存索引范圍。這個弊端可以通過提高組相聯(lián)路數(shù)來改善。

(4)多級cache

介于處理器和內(nèi)存二者之間的緩存有兩個天然沖突的性能指標(biāo):速度和容量。如果只向處理器看齊而追求速度,則必然要靠減少容量來換取訪問時間;如果只向內(nèi)存看齊而追求容量,則必然以增加處理器的訪問時間為犧牲。這種矛盾促使人們考慮使用多級緩存。

在一個兩級緩存體系中,一級緩存靠近處理器一側(cè),二級緩存靠近內(nèi)存一側(cè)。當(dāng)一級緩存發(fā)生失效時,它向二級緩存發(fā)出請求。如果請求在二級緩存上命中,則數(shù)據(jù)交還給一級緩存;如失效,二級緩存進一步向內(nèi)存發(fā)出請求。對于三級緩存可依此類推。

通常,更接近內(nèi)存的緩存有著更大容量,但是速度也更慢。

值得注意的是,無論如何,低級緩存的局部命中率總是低于高級緩存。這是因為數(shù)據(jù)的時空局部性在一級緩存上基本上已經(jīng)利用殆盡。

對于各級cache,雖然功能類似,但不同級別的緩存在設(shè)計和實現(xiàn)上也有不同之處。

一般而言,在存儲體系結(jié)構(gòu)中低級存儲總是包含高級存儲的全部數(shù)據(jù),但對于多級緩存則未必。相反地,存在一種多級排他性(Multilevelexclusion)的設(shè)計。此種設(shè)計意指高級緩存中的內(nèi)容和低級緩存的內(nèi)容完全不相交。這樣,如果一個高級緩存請求失效,并在次級緩存中命中的話,次級緩存會將命中數(shù)據(jù)和高級緩存中的一項進行交換,以保證排他性。

多級排他性的好處是在存儲預(yù)算有限的前提下可以讓低級緩存更多地存儲數(shù)據(jù)。否則低級緩存的大量空間將不得不用于覆蓋高級緩存中的數(shù)據(jù),這無益于提高低級緩存的命中率。

當(dāng)然,也可以如內(nèi)存對緩存般,使用多級包容性(Multilevelinclusion)設(shè)計。這種設(shè)計的優(yōu)點是比較容易方便查看緩存和內(nèi)存間的數(shù)據(jù)一致性,因為僅檢查最低一級緩存即可。對于多級排他性緩存這種檢查必須在各級上分別進行。這種設(shè)計的一個主要缺點是,一旦低級緩存由于失效而被更新,就必須相應(yīng)更新在高級緩存上所有對應(yīng)的數(shù)據(jù)。因此,通常令各級緩存的緩存塊大小一致,從而減少低級對高級的不必要更新。

此外,各級緩存的寫策略也不相同。對于一個兩級緩存系統(tǒng),一級緩存可能會使用寫通來簡化實現(xiàn),而二級緩存使用寫回確保數(shù)據(jù)一致性。orpsoc正是這樣設(shè)計的。

(5)關(guān)于cache的優(yōu)化

優(yōu)化緩存可從三個方面入手:減少命中時間,降低失效率,減輕失效代價。此外,增加緩存訪問帶寬也能有效較低AMAT(平均內(nèi)存訪問時間,AverageMemory Access Time)。

理論上,完全使用虛擬地址可以獲得更快的緩存訪問速度,因為這樣僅在緩存失效時才會進行地址翻譯。但是,如前所述,這種純虛地址緩存由于繞開了操作系統(tǒng)對進程訪問地址的軟件控制,會存在不少問題。

為了能接近虛緩存的訪問速度,又能避開虛緩存帶來的種種問題,引入了所謂虛索引、實標(biāo)簽緩存(virtuallyindexed, physically tagged)。這種結(jié)構(gòu)的緩存可以令地址翻譯和緩存查詢并發(fā)進行,大大加快了緩存的訪問速度。

由于電路延遲很大程度上取決于存儲芯片的大小,所以可考慮使用較小容量的緩存以保證最短的訪問周期。這么做的另一個好處是,由于一級緩存足夠小,可以把二級緩存的全部或部分也集成到CPU芯片上,從而減少了二級緩存的命中時間。

AMD從K6到Opteron連續(xù)三代CPU的一級緩存容量都沒有任何增長(均為64KB)正是基于這個原因。

另一方面,考慮使用簡單的緩存,如直接匹配緩存,也可較組相聯(lián)緩存減少命中時間。

路預(yù)測:

所謂路預(yù)測(Wayprediction),是指在組相聯(lián)緩存中,跟蹤同一組內(nèi)不同緩存塊的使用情況,然后在訪問到來時,不經(jīng)比較直接返回預(yù)測的緩存塊。當(dāng)然,標(biāo)簽比較仍然會進行,并且如果發(fā)現(xiàn)比較結(jié)果不同于預(yù)測結(jié)果,就會重新送出正確的緩存塊。也就是說,錯誤預(yù)測會造成一個緩存塊長度的延遲。

模擬表明路預(yù)測的準(zhǔn)確率超過85%[6]。這種技術(shù)非常適合于投機執(zhí)行(SpeculativeExecution)處理器,因為這種處理器有完善的機制來保證在投機失敗之后取消已經(jīng)派發(fā)的指令。

追蹤緩存:

與一般的指令緩存存儲靜態(tài)連續(xù)地址不同,追蹤緩存(TraceCache)存儲的是基于執(zhí)行歷史的動態(tài)地址序列。這實際上是把分支預(yù)測的結(jié)果用在了緩存上。由于只存儲沿某一特定分支路徑才會遇到的指令,這種緩存可比傳統(tǒng)緩存更節(jié)省空間。

追蹤緩存的缺點是實現(xiàn)復(fù)雜,因為必須設(shè)法連續(xù)存儲的數(shù)據(jù)并不會按照2的冪次字長對齊。此外,對于不同執(zhí)行路徑要分開存儲。如果這些執(zhí)行路徑中存在相同地址的指令,這些指令就只好被分別存到兩個地方。這反而造成了低效的空間利用。

Intel的Pentium4處理器使用了這一復(fù)雜技術(shù)。值得一提的是,Pentium4追蹤緩存存儲的不是從內(nèi)存抓取的原始指令,而是已經(jīng)過解碼的微操作,從而進一步節(jié)省掉了指令解碼上要花的時間。

增加訪問帶寬。

緩存流水線化:

將一級緩存并入流水線是一般做法。這種做法可行性在于一級緩存的訪問時間通常都極短,可能只有一到數(shù)個CPU周期。此外,由于TLB也是一種高速緩存硬件,所以也可以納入流水線。

非阻塞緩存:

一般而言,當(dāng)緩存發(fā)生失效時,處理器必須停滯(stall),等待緩存將數(shù)據(jù)從次級存儲中讀取出來。

對于跨序執(zhí)行(Out-of-orderExecution)處理器,由于多條指令在不同處理單元中并發(fā)執(zhí)行,某一條指令引發(fā)的緩存失效應(yīng)該只造成其所在處理單元的停滯,而不影響其他處理單元和指令派發(fā)單元繼續(xù)流水。因此,有必要設(shè)計這樣一種緩存,使之能夠在處理緩存失效的同時,繼續(xù)接受來自處理器的訪問請求。這稱為非阻塞緩存(Non-blockingcache)。

降低失效率。

使用更大的數(shù)據(jù)塊:

使用大數(shù)據(jù)塊有助于利用空間局部性降低失效率,但其代價是更高的失效代價。這是因為,一旦失效,就必須把整個數(shù)據(jù)塊都重新填滿。

使用更大的緩存:

單純增大緩存的容量也是降低失效率的一個辦法。不過顯然這也增大了命中時間。

高組相聯(lián)緩存:

使用多路組相聯(lián)可以減少沖突失效。但其后果是緩存電路邏輯復(fù)雜化,故增大了命中時間。

編譯器優(yōu)化:

存在多種編譯器優(yōu)化技術(shù)來間接影響緩存的使用模式。

責(zé)任編輯:haq

-

容量

+關(guān)注

關(guān)注

0文章

117瀏覽量

21253 -

軟件

+關(guān)注

關(guān)注

69文章

5003瀏覽量

87924 -

Cache

+關(guān)注

關(guān)注

0文章

129瀏覽量

28381

原文標(biāo)題:甄建勇:五分鐘搞定Cache(下)

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是緩存(Cache)及其作用

Cache和內(nèi)存有什么區(qū)別

解析Arm Neoverse N2 PMU事件L2D_CACHE_WR

2k1000LA中關(guān)于IODMA請求的描述

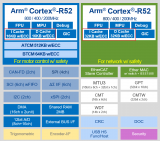

Cortex R52內(nèi)核Cache的具體操作(2)

Cortex R52內(nèi)核Cache的相關(guān)概念(1)

CortexR52內(nèi)核Cache的具體操作

關(guān)于Cache的其它內(nèi)容

關(guān)于Cache的其它內(nèi)容

評論