隨著智能駕駛和智能座艙時代到來以及AI技術的興起,汽車智能化成為了當前全球各個企業的目標和需求導向,自動駕駛和智能座艙在當前和未來的汽車開發和應用場景中備受關注,這對AI芯片需求量大大增加,也對當前AI芯片及芯片廠商提出更高挑戰。

在自動駕駛和智能座艙領域,目前英偉達、英特爾、德州儀器等不少芯片國際巨頭公司已布局良久。在此背景下,國產AI芯片公司如何突破國外技術封鎖?本文從國產芯片新星黑芝麻智能關于智能駕駛AI芯片的設計及制造流程來看如何實現彎道超車。

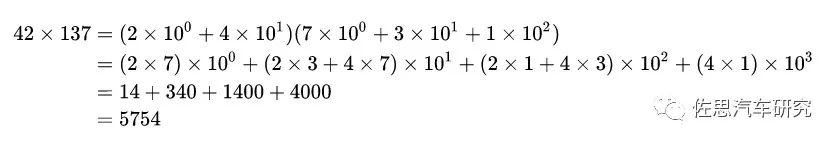

所謂AI芯片,神經網絡加速器是其必不可少的一部分,目前所有的神經網絡算法在硬件層面最消耗計算資源的就是乘和累加運算,即卷積,分解到硬件就是MAC(Multiply Accumulate)單元。通過這個下面公式可以說明MAC運算指令和 AI 算力之間的關系。

上面就是一個卷積,第二個等號右邊每個括號里的系數構成的序列 (14,34,14,4),實際上就是序列 (2,4) 和 (7,3,1) 的卷積。所謂AI算力就是每秒執行多少萬億次指令,這些指令通常就是MAC運算的指令。

AI芯片的核心就是MAC運算單元,流程就是從內存中讀取訓練好的模型的濾波權重值和輸入數據,兩者相乘,然后重復這個流程并將乘積累加,再寫入內存。

設計一款數字芯片,流程基本上是確定市場定位、確定性能與功能目標即設計規格參數、架構與算法設計、任務劃分、購買IP、RTL編碼與功能驗證即RTL仿真、綜合門級仿真、靜態時序分析與仿真。這是前端工序,后端是RTL轉門級網表文件、數據導入、布局規劃、單元布局、時鐘綜合樹、布線、物理驗證、版圖文件即GDSII交付晶圓代工廠。

也可以分為三級,第一級行為級(Behavior Level):通過行為級算法描述數字系統。也就是邏輯構思,人腦的思維流程。這一階段主要工具為C/C++/Matlab,熟悉這些工具的人很多,很好找。

第二級寄存器傳輸級(Register Transfer Level):在寄存器傳輸級,通過寄存器之間的數據傳輸進行電路功能設計,例如有限狀態機。工具是VHDL/Verilog/System Verilog,熟悉這些工具的人很少,這要求既要懂上層的邏輯結構,也要懂下層的電路實現。

第三級門級(Gate level):數字系統按門級(AND,OR,NOT,NAND等等…)描述。通常不會進行門級設計,門級網表一般是通過邏輯綜合的輸出。RTL可以用Verilog或VHDL描述。實際上還有更細分的系統級(System Level)或功能模塊級(Functional Model Level)。

芯片制造流程

了解上述芯片軟件設計之后,大家就會知道制作出一張芯片難點甚多,尤其在設計以及細節的把控上都是我國芯片被卡脖子的地方。對于芯片制造我們需要了解芯片的上下游,芯片的制造可以理解成點石成金的過程,只不過此處的石是硅石,其材料主要是硅。

其中最重要的是第1步二氧化硅到硅的過程,所以造芯片的第1步就是要把二氧化硅還原成硅錠,從目前所使用的工藝來看,硅錠圓形橫截面的直徑為200毫米。在保留硅錠的各種特性不變的情況下增加橫截面的面積是具有相當大難度的。

在經過提成,去拉法等獲得一根長長的硅棒,然后經過切割,切片越薄,用料越省,自然可以生產的處理器芯片就更多。切片還要鏡面精加工的處理來確保表面絕對光滑,之后檢查是否有扭曲或其它問題。這一步的質量檢驗尤為重要,它直接決定了成品芯片的質量。

研磨等制成像光盤一樣的硅片,在送往晶圓廠通過光刻和石刻雕刻出晶體管的物理結構。光刻是芯片制造過程中工藝非常重要且復雜的一個步驟,光刻蝕過程就是使用一定波長的光在感光層中刻出相應的刻痕,由此改變該處材料的化學特性。

這項技術對于所用光的波長要求極為嚴格,需要使用短波長的紫外線和大曲率的透鏡。每一步刻蝕都是一個復雜精細的過程。設計每一步過程所需要的數據量都可以用10GB單位來計量。

在殘留的感光層物質被去除之后,剩下的就是充滿的溝壑的二氧化硅層以及暴露出來的在該層下方的硅層。感光層同時還要被短波長光線透過掩模刻蝕。

再經過一部刻蝕,并通過離子注入和覆膜等手段賦予其電特性,摻入的物質原子進入硅原子之間的空隙,彼此之間發生原子力的作用,從而使得硅原料具有半導體的特性,在其上刻劃代表著各種邏輯功能的晶體管電路。形成一張芯片,最后將它們切割分離并進行封裝測試就完成了一個個芯片的制造。

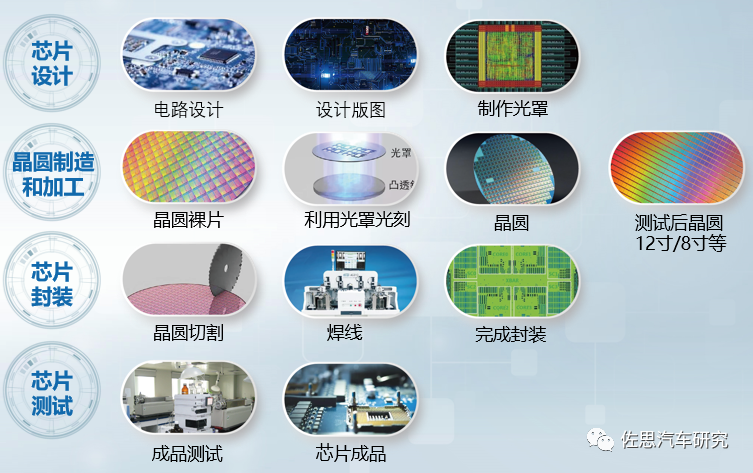

圖 3 黑芝麻智能駕駛芯片制造的基本過程

上圖是以黑芝麻智能駕駛芯片制造流程為例,在制造工藝流程方面簡單總結為:

晶圓制造與加工:

晶圓制造:融化,提純,拉晶獲得單晶硅硅棒,對硅棒進行切片,研磨等獲得晶圓。

晶圓加工:光刻改變晶圓材料的化學特性,上述設計的電路制作成一片片光罩,使用強光透過光罩后照在晶圓上,在曝光過程結束后加入顯影液,正光刻膠的感光區、負光刻膠的非感光區,會溶解于顯影液中。

這一步完成后,光刻膠層中的圖形就可以顯現出來,顯影工序使將在曝光過程中形成的隱性圖形成為光刻膠在與不在的顯性圖形。顯影中進行的是選擇性溶解的過程,最重要的是曝光區和未曝光區之間溶解率的比值(DR)。

下一步是刻蝕和離子注入,刻蝕對于器件的電學性能十分重要。如果刻蝕過程中出現失誤,將造成難以恢復的硅片報廢,因此必須進行嚴格的工藝流程控制。

半導體器件的每一層都會經歷多個刻蝕步驟,離子注入是一種將特定離子在電場里加速,然后嵌入到另一固體材料之中的技術手段。重復這些步驟,然后就出現了一個多層立體架構,這就是目前使用的芯片的最初狀態了。

芯片封裝:

芯片封裝是將Foundry廠生產的晶圓切割成一個個小的晶片,通過不同的封裝技術對晶片進行塑封封裝從而得到我們看到的芯片。

芯片測試:

芯片測試包括:良率測試,功能測試,性能測試,可靠性測試等。

芯片制造最近幾年的變化隨著半導體行業技術發展,工藝從微米進入納米時代,根據行業數據來看,業界最先進的工藝制程5nm已經在2020年量產,3nm的已經進入試產階段。

而且隨著CMOS工藝的演進,柵氧厚度也要不斷縮小。薄到一定厚度的柵氧就不再是理想的絕緣體,會出現明顯的泄漏。在40nm進入28nm的時候,業界開始普遍采用HKMG技術。技術路線分為Gate-first和Gate-last。

工藝進入到16nm/14nm的時候,晶體管結構從2D變為3D FinFET能夠帶來更好的leakage current控制和更好的性能,成為先進工藝節點必選的晶體管結構。

而目前最先進的量產工藝主要是7nm/5nm,更小的pitch讓EUV技術越來越成為主流TSMC從N7+開始采用EUV,最初的7nm工藝(N7/N7P)仍然采用DUV,三星則是在其第一代7nm工藝上就采用了EUV技術。

GAA(Gate All Around)的名稱來自晶體管結構,這個全新設計將柵極完全包裹在通道周圍,可實現更好的控制。三星相對TSMC來說,會更早采用GAA技術。TSMC則會從2nm開始采用GAA,這是未來的趨勢之一。

半導體工藝的不斷進步,會帶來PPA(Performance Power Area)的提升,進而提升芯片以及系統產品的關鍵指標和用戶體驗,這對算力要求超高的智能駕駛芯片來說,有著決定性的影響。

對于智能輔助駕駛和智能駕駛車輛來說,車規級芯片需要復雜SOC芯片兼具高算力,高集成度,高可靠性的要求,同時需要控制芯片體積和功耗,當然還要考慮芯片發熱情況。

編輯:jq

-

德州儀器

+關注

關注

123文章

1727瀏覽量

140896 -

Mac

+關注

關注

0文章

1109瀏覽量

51588 -

自動駕駛

+關注

關注

784文章

13915瀏覽量

166773 -

AI芯片

+關注

關注

17文章

1901瀏覽量

35143 -

智能座艙

+關注

關注

4文章

973瀏覽量

16391

原文標題:一款智能駕駛AI芯片的設計與制造流程

文章出處:【微信號:BlackSesameTech,微信公眾號:黑芝麻智能】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

smart與元戎啟行攜手,共研智能駕駛AI大模型

smart與元戎啟行達成戰略合作 布局智能駕駛AI大模型

AI數據服務在智能駕駛訓練中的應用實例

大話芯片制造之讀后感超純水制造

AI智能體是什么_AI智能體如何重塑企業業務流程

GDS文件在芯片制造流程中的應用

淺談芯片制造的完整流程

PCBA加工全流程解析:電子制造的關鍵環節

三星電子推出AI芯片一站式合約制造服務,加速智能時代步伐

解析智能駕駛AI芯片的設計與制造的流程

解析智能駕駛AI芯片的設計與制造的流程

評論