小技巧分享:

verilog下取對數其實可用$clog2這個系統函數,和自己找代碼里面寫入function是同樣的效果,但是方便的多。這是verilog 2005就開始支持的標準,所以vivado也是支持的,我試了2017.4及以后的版本都可以支持,放心用。

***友情提示:所有支持verilog2005標準的編譯器都可以用這個函數,所以使用之前確定編譯器是否支持這個標準,還有考慮好后期可移植性的影響

這個是可編譯的函數大家可以把她當做宏定義函數一樣看待。這操作好玩嗎?好玩就趕緊升級編譯器吧,新標準總是有很多的改進,如果想了解一些更有意思的東西歡迎關注我,我是最騷的FPGAer。

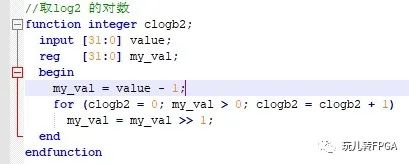

這里附上常用的自定義log2函數,供大家白嫖。圖片不清晰盡請擔待。

編輯:jq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605245 -

函數

+關注

關注

3文章

4345瀏覽量

62882 -

代碼

+關注

關注

30文章

4823瀏覽量

68904 -

編譯

+關注

關注

0文章

661瀏覽量

32978

原文標題:verilog2005的騷操作之對數函數

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TSC2005EVM和TSC2005EVM-PDK用戶指南

電子發燒友網站提供《TSC2005EVM和TSC2005EVM-PDK用戶指南.pdf》資料免費下載

發表于 12-19 15:45

?0次下載

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog測試平臺設計方法是Verilog FPGA開發中的重要環節,它用于驗證Verilog設計的正確性和性能。以下是一個詳細的Verilog測試平臺設計方法及

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog 與 VHDL 比較 1. 語法和風格 Verilog :Verilog 的語法更接近于 C 語言,對于有 C 語言背景的工程師來說,學習曲線較平緩。它支持結構化編程,代碼更直觀,易于

使用Phase Lab2024A計算示蹤擴散系數的操作步驟

計算示例為Fe-Mn二元系,選擇固定成分,繪制示蹤擴散系數隨溫度的變化曲線,Mn元素為主變元素,這里取值0.2(摩爾分數),Fe為剩余元素,計算結果將通過溫度的倒數1000/T為橫坐標,10為底的對數函數值為縱坐標進行曲線繪制。以下是操作的分解步驟和計算結果。 ①第一步

SUMIF函數與SUMIFS函數的區別

SUMIF函數和SUMIFS函數都是Excel中用于條件求和的函數,它們可以幫助用戶根據特定的條件對數據進行求和。盡管它們的基本功能相似,但在使用場景和功能上存在一些差異。以下是對這兩

SUMIF函數使用教程

SUMIF函數是Excel中非常實用的函數之一,能夠根據指定條件對數據進行篩選和求和操作。以下是對SUMIF函數使用方法的詳細教程: 一、基

回調函數(callback)是什么?回調函數的實現方法

回調函數是一種特殊的函數,它作為參數傳遞給另一個函數,并在被調用函數執行完畢后被調用。回調函數通常用于事件處理、異步編程和處理各種

發表于 03-12 11:46

?3113次閱讀

verilog調用模塊端口對應方式

Verilog中的模塊端口對應方式,并提供示例代碼和詳細解釋,以幫助讀者更好地理解和應用。 首先,我們來了解一下Verilog中的模塊和模塊端口。一個Verilog模塊被定義為包含一組聲明和語句的代碼塊,類似于C語言中的

verilog中for循環是串行執行還是并行執行

在Verilog中,for循環是并行執行的。Verilog是一種硬件描述語言,用于描述和設計數字電路和系統。在硬件系統中,各個電路模塊是同時運行的,并且可以并行執行多個操作。因此,在Veril

verilog task和function區別

verilog中的task和function都是用于實現模塊中的可重復的功能,并且可以接收參數和返回結果。但是它們在編寫和使用上有一些區別。下面將詳細介紹task和function的區別。 語法結構

verilog function函數的用法

Verilog 是一種硬件描述語言 (HDL),主要用于描述數字電子電路的行為和結構。在 Verilog 中,函數 (Function) 是一種用于執行特定任務并返回一個值的可重用代碼塊。函數

verilog中function和task的區別

在Verilog中,Function和Task是用于模塊化設計和重用代碼的兩種重要元素。它們允許開發人員將復雜的操作分解為更小的功能單元,并在需要時調用它們。雖然Function和Task在某些方面

verilog中函數和任務對比

在verilog中,函數和任務均用來描述共同的代碼段,并且在模式內任意位置被調用,提高代碼效率,讓代碼更加的直觀,提高代碼可讀性。但是在實際使用的過程中,函數和任務也存在諸多的不同,下面將對而這進行

剖析verilog2005的騷操作之對數函數

剖析verilog2005的騷操作之對數函數

評論