本篇主要針對Zynq UltraScale + MPSoC的DDR接口,從硬件設計的角度進行詳細介紹,最后展示一下小編之前自己設計的基于ZU+的外掛8顆DDR4的設計。

目前比較常用的DDR是DDR4和DDR3,其他系列相對使用較少一些,本文主要以DDR4進行介紹。

1、選型

根據ZU+系列芯片的數據手冊、TRM、pg150等文檔,DDR可以掛載在PS側,也可以掛載在PL側,也可同時掛載在PS側和PL側。

PL和PS均支持64位的DDR4(不帶ECC功能),PL部分如果要支持64位的DDR4,則至少需要提供三個bank的HP接口,只能選擇SFVC784或者更高的封裝。需要特別說明的是,使用內存顆粒和使用內存條的容量差異較大,需要根據實際需求進行選擇。

針對DDR3,其特性如下:

支持DDR3 (1.5V) and DDR3L (1.35V)

容量限制:Support densities up to 8 Gb for components, 32 GB for RDIMMs, 16 GB for SODIMMs, and 16 GB for UDIMMs. Other densities for memory device support is available through custom part selection.

針對DDR4,其特性如下:

容量限制:Support densities up to 32 Gb for components, 64 GB for LRDIMMs, 128 GB for RDIMMs, 16 GB for SODIMMs, and 16 GB for UDIMMs. Other densities for memory device support is available through custom part selection.

DDR接口粗略的介紹可以參見之前的文章《Zynq UltraScale+系列之“外圍接口概述”》,PS側的DDR控制器的詳細特性可參看《UG1085》的第17章,PL側的的相關特性可參考《PG150》、《WP454》等資料,此處不再贅述。

2、Performance

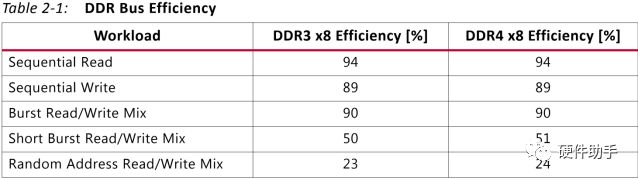

DDR總線的效率在不同的使用模式下差異很大,在實際評估速率時一定要搞清楚使用情況。

針對幾種常用的操作模式,《PG150》給出了具體的效率,詳見下表:

幾種常見的操作模式如下:

Sequential Read

Simple address increment pattern

100% reads

Sequential Write

Simple address increment pattern

100% writes (except for periodic reads generated by the controller for VT tracking)

Burst Read/Write Mix

Repeating pattern of 64 sequential reads and 64 sequential writes

50/50 read/write mix

Short Burst Read/Write Mix

Repeating pattern of four sequential reads and four sequential writes

Full DRAM page accessed in bursts of four before changing the row address for highpage hit rate

50/50 read/write mix

Random Address Read/Write Mix

Repeating pattern of two random reads and two random writes

Fully random address for a low page hit rate

50/50 read/write mix

3、原理圖設計

PS側的原理圖設計基本沒有任何問題,按照對應功能引腳連接即可,PL側的接口需要特別注意。

對于單個Memory接口,盡量集中使用幾個HPbank。如果使用三個bank,兩個bank用作數據接口,一個bank用作地址、控制、命令信號線接口,地址、控制、命令信號盡量使用同一個bank,不要跨bank使用;如果使用兩個bank,盡量保證數據相關引腳在一個bank,地址和控制信號在另一個bank。

地址、控制、命令信號不能和data共用byte group,只能使用data byte groups以外的byte groups。

CK差分時鐘對必須使用差分對,必須連接在控制byte group上,盡量按照Vivado軟件對時鐘引腳的約束來連接。如果有多個CK對,必須來自于同一個byte lane。

除了DQS和CK之外,其他信號都可以在byte group內隨意交換。

前期原理圖設計階段最好在vivado中進行PL側管腳預分配,別等到PCB出來后才開始在vivado中驗證,如果關鍵信號管腳定義有問題,不能交換,則無法彌補。

4、PCB Guidelines for DDR4 SDRAM (PL and PS)

DDR總線的布局布線需要遵循一些通用的規則,數據線只支持點到點連接,其他信號根據顆粒數量的不同可以有多種拓撲。

ZU+ DDR4 SDRAM支持兩種拓撲類型:fly-by和clamshell。Clamshell拓撲在板子空間比較緊張時有一定的優勢。在MIG中(PL側)是一種可選的拓撲,在PS側不支持clamshell拓撲。

如果使用5片x16的顆粒組成80位寬的接口時,5片DDR的布局采用fly-by topology,如果用9片x8的顆粒,則采用clamshell topology比較節約空間。

由于官方推薦的主線路阻抗較小(單端36/39Ω,差分76Ω),線寬比較寬,但扇出部分阻抗又比較大(單端50Ω,差分86Ω),會導致阻抗突變,因此實際使用中可以通過調整疊層來優化線寬,在滿足阻抗要求的同時減小阻抗突變。

4.1.4、Layout Guidelines

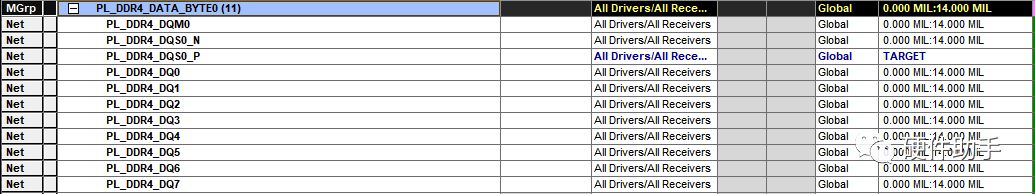

以下為DDR4的約束規則,表格中的參數均為最短信號線和最長信號線之間的tolerance參數,數據group一般都是以DQS為TARGET,DQ與DQS進行比較約束。地址、控制、命令group一般都是以CLK為TARGET,ACC(Address、Command、Control)與CLK進行比較約束。

針對上圖解釋為:例如,最快的ACC信號線傳輸時間是800ps,最慢的ACC信號線傳輸時間是840ps,時鐘信號線的傳輸時間應該為862ps±8ps,比ACC總線的中間傳輸時間(820ps)慢42ps.

CLK和DQS之間的約束比較寬松,最小的差異可以為-879,最大差異可以為+10600,主要是為了保證讀寫平衡功能從整個菊花鏈的第一片到最后一片顆粒都正常。

DDR控制器可以調整DQS信號線的內部延遲,由于CK信號線鏈路連接每一片DDR顆粒,導致CK容性負載更重,所以需要能夠調整DQS信號線的內部延遲,以滿足和CK之間的約束。

規范規定CK信號線和DQS信號線從FPGA到鏈路中的第一片DDR顆粒的偏差不小于-149ps,到鏈路中最遠端的DDR顆粒的偏差不大于1796ps。只要鏈鏈路中第一片DDR顆粒和最后一片DDR顆粒都滿足此條件,整個鏈路上所有的DDR顆粒的讀寫平衡功能都將正常。

例如,如果從FPGA到第一片DDR顆粒的DQS延遲為200ps,則從FPGA到第一片DDR顆粒的CK延遲應至少為51ps(200ps-149ps)。如果從FPGA到最后一片DDR顆粒的DQS延遲為700ps,則從FPGA到最后一片DDR顆粒的CK延遲應該小于2496ps(700ps+1796ps)。

下面是一些基本的規則,可以參考遵守:

使用內存條時,CK信號和DQS信號之間的余量會更小一些,因為約束的是FPGA到DIMM插槽處,而顆粒的走線是由DIMM決定的,因此余量預留小一些。

同組的DQ、DQS、DM走線必須在同一層。

DIMM數據線走線最好選擇靠近接插件的層,尤其是靠DIMM中間位置的數據組。

采用菊花鏈結構布線時,ACC信號線可以布在不同的層,但層數越少越好。不要將一個信號切換好幾層,主要走線盡量一層走完,這樣可以減小串擾,信號換層時,切換過孔附近50mil范圍內需要放置一個接地過孔。

FPGA和DDR器件驅動端的阻抗為40Ω,DCI和ODT也是40Ω。因此VTT端接電阻都選為39.2Ω。

當使用內部VREF時,PL側HP bank上的VREF引腳可以懸空,但不能用于普通IO。

如果系統時鐘連接到了DDR的HPbank,則LVDS時鐘信號需要外部端接至合適的電壓,因為該bank上有不同的邏輯電平(HSTL, SSTL, or POD)。

對于菊花鏈布局,人字形扇出(chevron-style routing)可以形成stitching vias;對于比較緊湊的布局,可以通過環抱式扇出形成ground stitch vias。

在器件內部或者周圍盡量多放置接地過孔,這樣可以更好的為信號提供返回路徑,尤其是在邊角的位置。

對于ACC信號線的端接電阻布局,應該每四個端接電阻中間穿插布局一個0.1uF的VTT去耦電容,這樣可以減小端接VTT的噪聲。為了便于布局,最好在原理圖中就按每四個電阻放置一個去耦電容。

對于DIMM,去耦電容放置得離DIMM越近越好,這樣除了能提供接地過孔外,也能給電源提供低阻抗回路。

以上就是針對ZU+系列MPSoC的DDR接口的詳細介紹,PCB設計相關可參考《UG583:UltraScale Architecture PCB Design User Guide》、官方開發板ZCU104、ZCU102、ZCU106等。

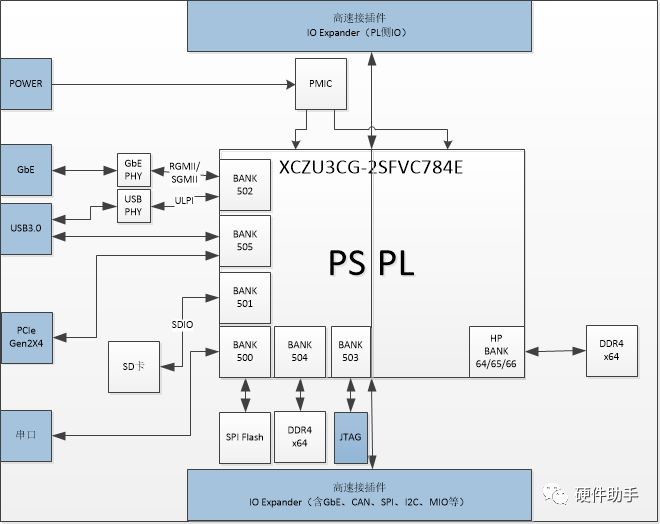

下面介紹一下小編自己設計的基于ZU+(XCZU3CG-SFVC784)的外掛8顆DDR4的設計,采用十層板,板厚1.6mm,最小線寬4mil。板子尺寸120*150mm,單12V電源輸入,支持串口、I2C、USB、GbE、TF卡、CAN、PCIe等常用接口,預留PS側和PL側IO接口。

硬件框圖如下圖所示:

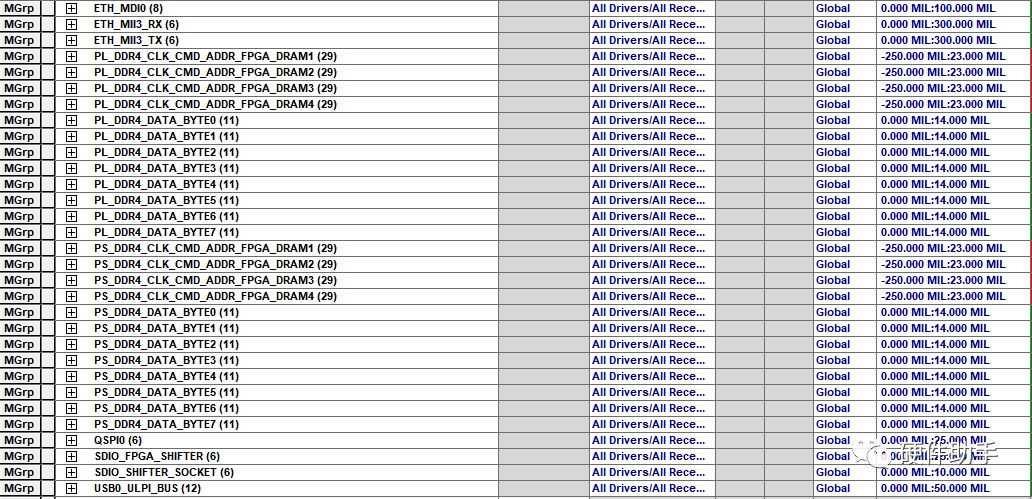

Allegro中的約束規則如下圖所示:

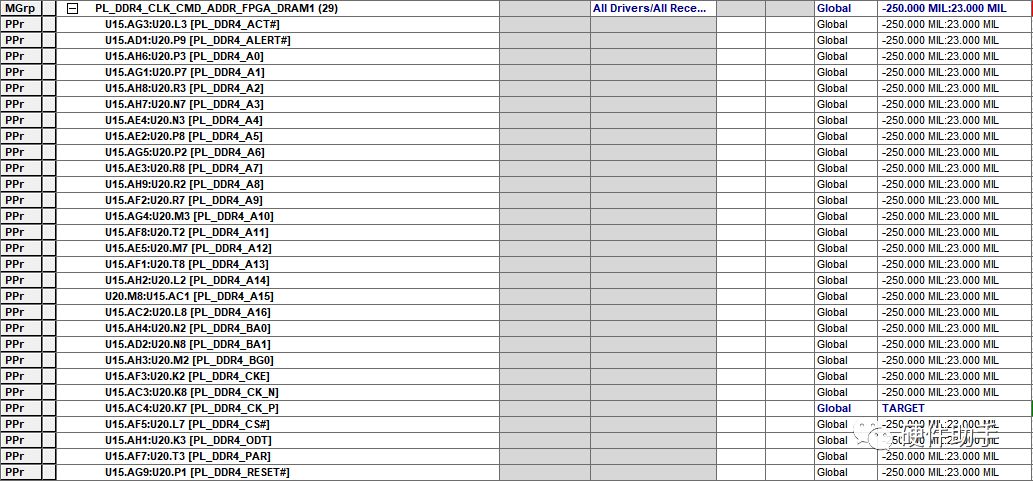

ACC信號線的約束規則如下圖所示:

DATA信號線的約束規則如下圖所示:

責任編輯:haq

-

接口

+關注

關注

33文章

8691瀏覽量

151702 -

DDR

+關注

關注

11文章

715瀏覽量

65453

原文標題:Zynq UltraScale +系列之“DDR4接口設計”

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ZYNQ基礎---AXI DMA使用

針對ZYNQ+ULTRASCALE的FPGA供電的一些疑問求解答

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

基于PYNQ和機器學習探索MPSOC筆記

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

12G-SDI高清視頻開發案例,讓4K視頻采集更便捷!基于Xilinx MPSoC高性能平臺

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

一個更適合工程師和研究僧的FPGA提升課程

產品原理圖:619-基于雙FMC接口 ZU19EG 的6U VPX采集存儲計算處理卡

XCZU15EG設計原理圖:523(ZCU102E的pin兼容替代卡) 基于 XCZU15EG的雙 FMC通用信號處理板

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設計PCB的步驟詳解

Zynq UltraScale + MPSoC的DDR接口

Zynq UltraScale + MPSoC的DDR接口

評論