發展歷史

可編程邏輯器件伴隨著半導體集成電路的發展而不斷發展,其發展可以劃分為以下4個階段:

1.第一階段

20世紀70年代,可編程器件只有簡單的可編程只讀存儲器(PROM)、紫外線可擦除只讀存儲器(EPROM)和電可擦除只讀存儲器(EEPROM)3種,由于結構的限制,它們只能完成簡單的數字邏輯功能。

2.第二階段

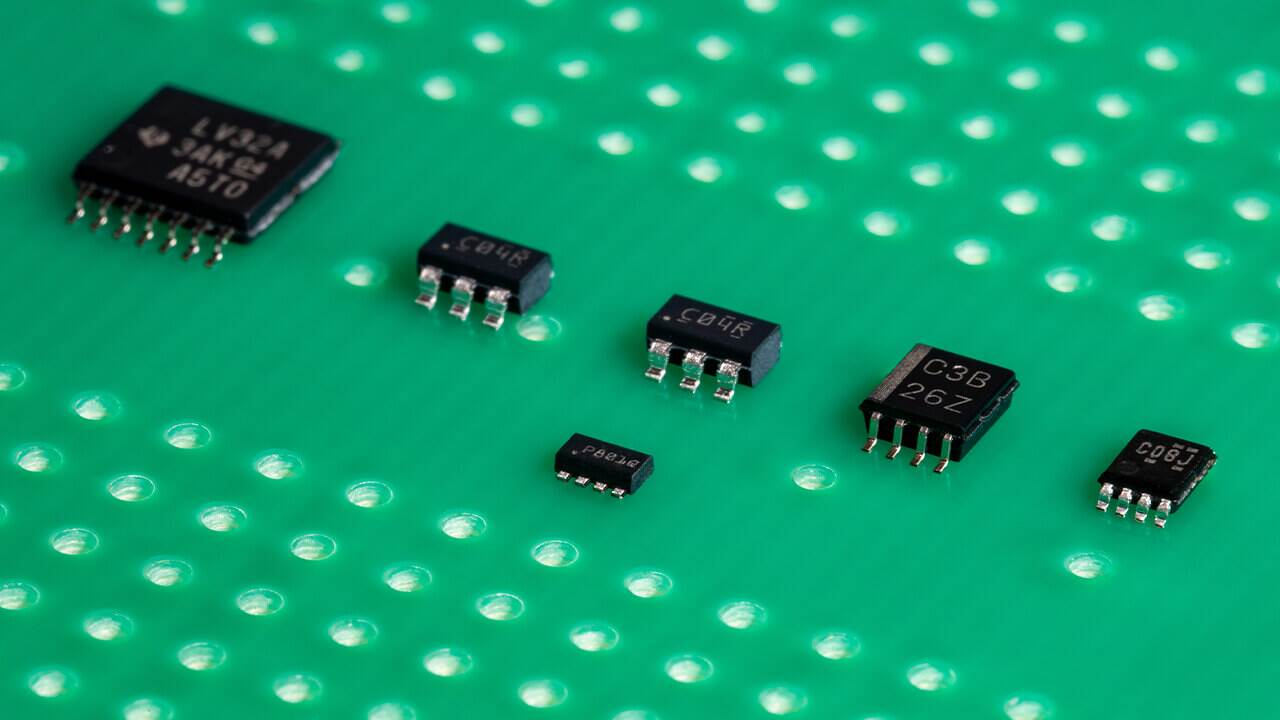

20世紀80年代,出現了結構上稍微復雜的可編程陣列邏輯(PAL)和通用陣列邏輯(GAL)器件,正式被稱為PLD,它們能夠完成各種邏輯運算功能。典型的PLD由“與”、“非”陣列組成,用“與或”表達式來實現任意組合邏輯,所以PLD能以乘積和形式完成大量的邏輯組合。PAL器件只能實現可編程,在編程以后無法修改;如需要修改,則需要更換新的PAL器件。但GAL器件不需要進行更換,只要在原器件上再次編程即可。

3.第三階段

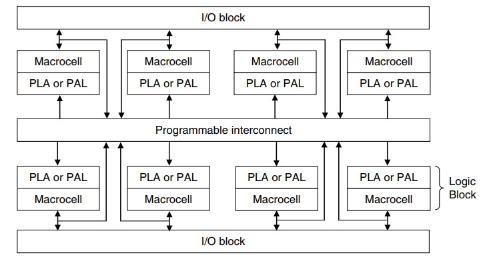

20世紀90年代,眾多可編程邏輯器件廠商推出了與標準門陣列類似的FPGA和類似于PAL結構的擴展性CPLD提高了邏輯運算的速度,具有體系結構和邏輯單元靈活、集成度高和適用著圍寬等特點,兼容了PLD和通用門陣列的優點,能夠實現超太規模的電路,編程方式也很靈活,成為產品原型設計和中小規模(一般小于10000)產品生產的首選。

4.第四階段

21世紀初,現場可編程門陣列和CPU相融合,并且集成到了單個的FPGA器件中。典型的,Xilinx推岀了兩種基于FPGA的嵌人式解決方案:

(1)FPGA器件內嵌了時鐘頻率高達500MHz的PowerPC硬核微處理器和1GHZ的ARM Cortex-A9雙核硬核嵌入式處理器。

(2)提供了低成本的嵌入式軟核處理器,如:MicroBlaze、PicoBlaze。

通過這些嵌人式解決方案,實現了軟件需求和硬件設計的完美結合,使FPGA的應用范圍從數字邏輯擴展到了嵌人式系統領域。

可編程邏輯器件工藝

1.熔絲連接工藝

最早允許對器件進行編程的技術是熔絲連接技術。在釆用這種技術的器件中,所有邏輯靠熔絲連接。熔絲器件只可編程一次,一旦編程,永久不能改變。

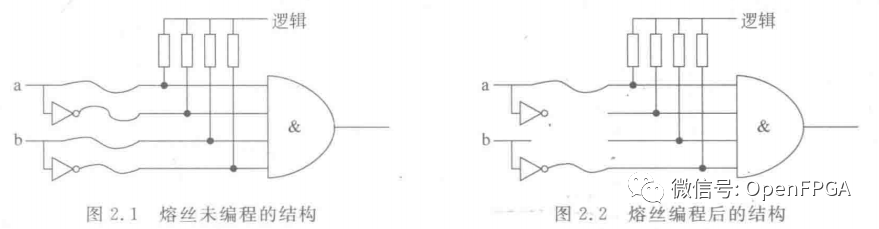

熔絲的編程原理如圖2.1所示。進行編程時,需要將熔絲燒斷;編程完成后,相應的熔絲被燒斷,如圖2.2所示。

2.反熔絲連接工藝

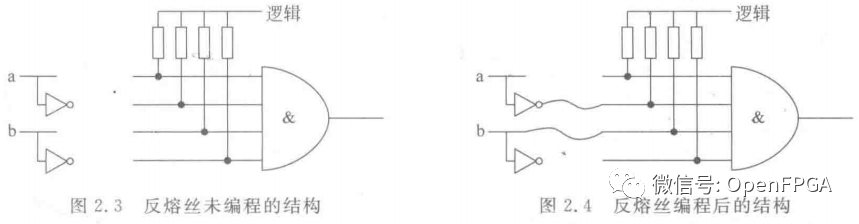

反熔絲技術和熔絲技術相反,在未編程時,熔絲沒有連接;編程后,熔絲將和邏輯單元連接。反熔絲開始是連接兩個金屬的微型非晶硅柱,未編程時,呈高阻狀態;編程結束后,形成連接。反熔絲器件只可編程一次,一旦編程,永久不能改變。

反熔絲的編程原理如圖2.3所示。進行編程時,需要將熔絲連接;編程完成后,相應的熔絲被連接,如圖2.4所示。

3.SRAM工藝

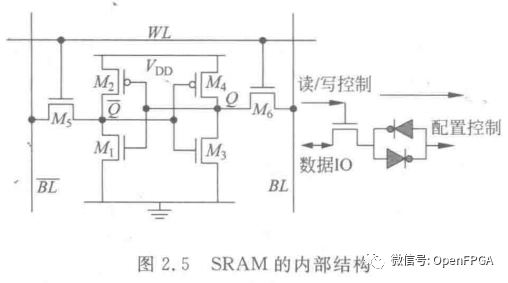

SRAM的結構如圖2.5所示。基于靜態存儲器SRAM的可編程器件,值被保存在SRAM中時,只要系統正常供電,信息就不會丟失,否則信息將丟失。SRAM存儲數據需要消耗大量的硅面積,且斷電后數據丟失,但是這種器件可以反復地編程和修改。

絕大多數的FPGA都采用這種工藝,這就是FPGA外部都需要有一個PROM芯片來保存設計代碼的原因。

4.掩膜工藝

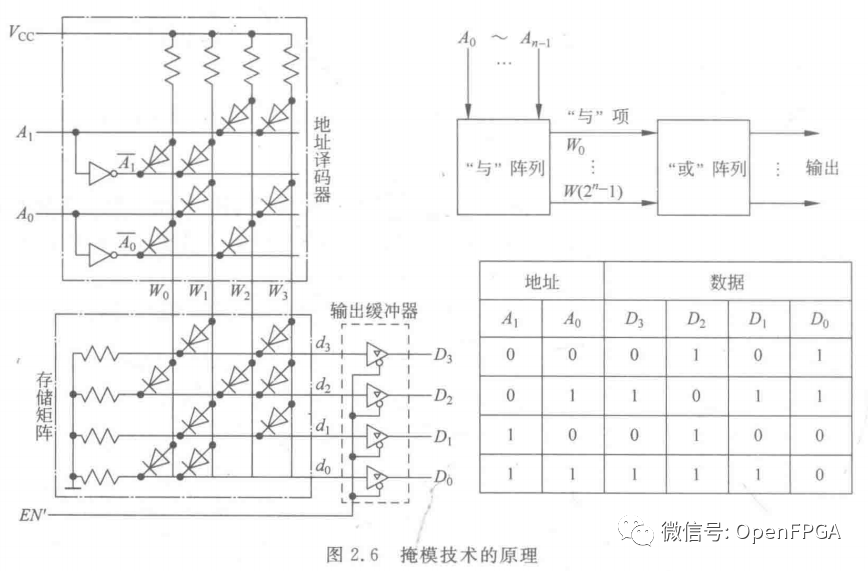

ROM是非易失性的器件,系統斷電后,將信息保留在存儲單元中。掩膜器件可以讀出信息,但是不能寫入信息。ROM單元保存了行粕列數據,形成一個陣列,每一列有負載電阻使其保持邏輯1,每個行列的交叉有一個關聯晶體管和一個掩膜連接,如圖2.6所示。

注:這種技術代價比較高,基本上很少使用。

下面對其工作原理進行推導,以幫助讀者理解上圖所實現的功能。

PROM工藝

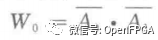

PROM是非易失性器件,系統斷電后,信息被保留在存儲單元中。PROM器件可以編程一次,以后只能讀數據而不能寫入新的數據。PROM單元保存了行和列數據,形成一個陣列,每一列有負載電阻使其保持邏輯1,每個行列的交叉有一個關聯晶體管和一個掩模連接,如下圖所示。

如果可以多次編程,就稱為EPROM和EEPROM技術。

6.FLASH工藝

釆用FLASH技術的芯片的擦除速度比采用PROM技術的芯片要快得多。FLASH技術可采用多種結構,與EPROM單元類似,具有一個浮置柵晶體管單元和EEPROM器件的薄氧化層特性。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605245 -

FlaSh

+關注

關注

10文章

1642瀏覽量

148455 -

EEPROM

+關注

關注

9文章

1033瀏覽量

81849 -

可編程邏輯

+關注

關注

7文章

517瀏覽量

44149 -

只讀存儲器

+關注

關注

1文章

41瀏覽量

10430

原文標題:【簡談】可編程邏輯器件發展歷史及工藝分類

文章出處:【微信號:gh_339470469b7d,微信公眾號:FPGA與數據通信】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

德州儀器 (TI) 全新可編程邏輯產品系列助力工程師在數分鐘內完成從概念到原型設計的整個過程

什么是現場可編程邏輯陣列?它有哪些特點和應用?

納維科技邀您參加“2024功率半導體器件與集成電路會議”

FPGA零基礎學習系列精選:半導體存儲器和可編程邏輯器件簡介

可編程片上系統是什么

半導體發展的四個時代

現場可編程門陣列簡介

現場可編程門陣列是什么

可編程邏輯陣列PLA內部邏輯結構示意

可編程邏輯器件隨著半導體集成電路的4個階段

可編程邏輯器件隨著半導體集成電路的4個階段

評論