Partial Reconfiguration(部分重配置)在現在的FPGA應用中越來越常見,我們這次的教程以Project模式為例來說明部分重配置的操作過程。

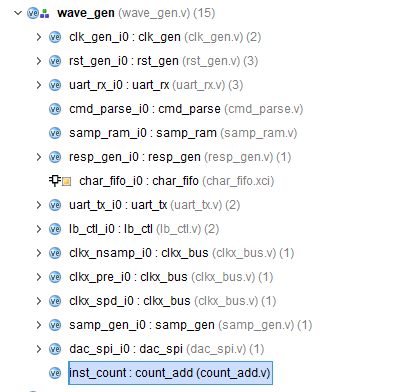

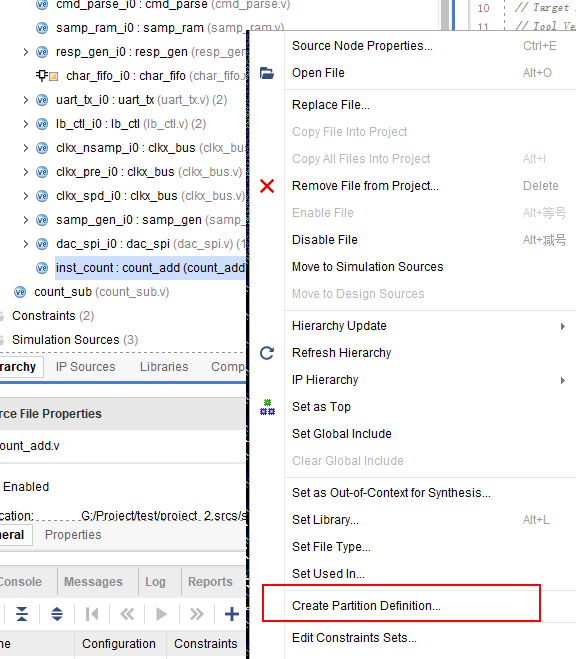

這里我們使用的Vivado版本是2017.2,使用的例程是Vivado自帶的wavegen工程,并在工程中增加一個計數器模塊,如下圖所示

在這里插入圖片描述

這個模塊的代碼也很簡單,就是加1計數

modulecount_add( inputclk, inputrst, outputreg[7:0]res ); always@(posedgeclk)begin if(rst) res<=?8'b0; ????else? ????????res?<=?res?+?1'b1; ?end??????? endmodule

我們要把這個模塊當做Reconfiguration Module,把它替換成另外一個module: count_sub,就是每個周期減1計數。

modulecount_sub( inputclk, inputrst, outputreg[7:0]res ); always@(posedgeclk)begin if(rst) res<=?8'b0; ????else? ????????res?<=?res?-?1'b1; ?end??????? endmodule

下面開始進行Partial Reconfiguration的配置

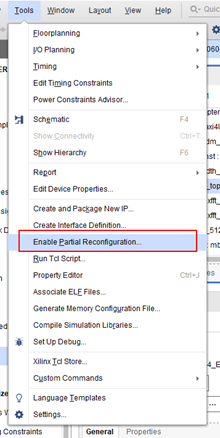

首先打開工程,并將其中一個Reconfiguration Module添加到工程中即可,這里我們選擇將count_add添加到工程中,選擇Tools->Enable Partial Reconfiguration

在這里插入圖片描述

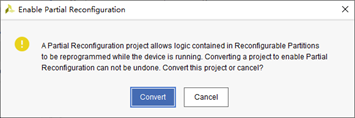

出現下面的對話框,點擊Convert。該對話框是指如果使能了Partial Reconfiguration模式,是不能返回到普通模式的。

在這里插入圖片描述

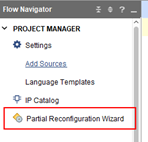

此時在Flow Navigator的PROJECT MANAGER下面就會出現Partial Reconfiguration Wizard的選項

在這里插入圖片描述

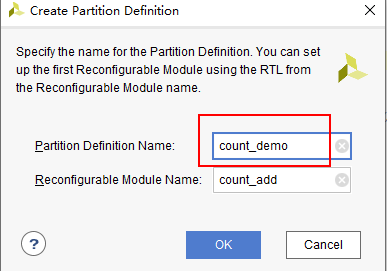

右鍵要reconfiguration的模塊,即inst_count,并選擇Create Partition Definition

在這里插入圖片描述

此時,彈出對話框提示我們輸入創建的Partition的名字,我們起名為count_demo,點擊OK

在這里插入圖片描述

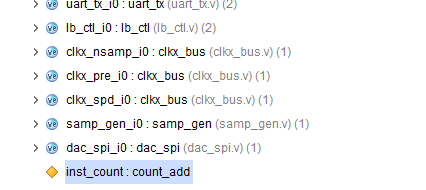

這時我們可以看到該模塊的圖標發生了變化,變成了黃色的棱形,如下圖所示

在這里插入圖片描述

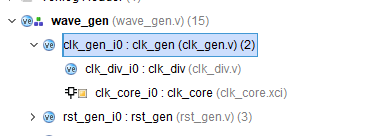

在這一步我們需要提醒一下,通常我們需要進行PR的模塊都是比較復雜的模塊,里面很可能會包含IP Core,那樣的話我們就不能直接這樣操作,比如我們要對該工程中的clk_gen_i0模塊進行PR,可以看到,這個模塊中包含了clk_core_i0這個IP

在這里插入圖片描述

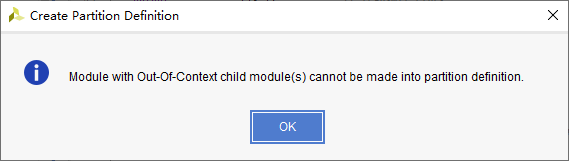

當我們在clk_gen_i0這個模塊上右鍵選擇Create Partition Definition時,會提示下面的對話框:

module with out-of-context child module cannot be made into partition definition

在這里插入圖片描述

這個意思是包含有ooc子模塊的模塊,是不能做成partiton的,Vivado中所有的IP Core都是ooc的模塊,因此我們需要把clk_gen_i0這個模塊導出成dcp后再使用,具體可以參考我的另一篇文章

Vivado中模塊封裝成edif和dcp

簡單來講,就是先將這個模塊設為top,綜合后導出dcp,使用的tcl腳本是

write_checkpoint-noxdef

有幾個需要RM(Reconfiguration Module)的模塊,就要綜合幾次,導出幾個dcp文件

我看網上也有的教程是直接對整個工程進行綜合,然后單獨導出RM模塊的dcp,使用下面的tcl

write_checkpoint-cell

這兩種導出dcp的方式是有區別的,把整個工程進行綜合,每個子模塊的接口很有可能會有所改變,可能是名字改了,也可能是增加或減少了一些接口。如果我們的幾個RM只是接口相同,功能不同的話,這樣帶有不同RM模塊的工程綜合的結果可能不一樣。因此推薦將RM模塊設為top,綜合后導出dcp。

另一點需要注意的是,如果使用了dcp文件,我們也添加一個wrapper.v到工程中,因此dcp文件是不能直接進行Create Partition Definition操作的。

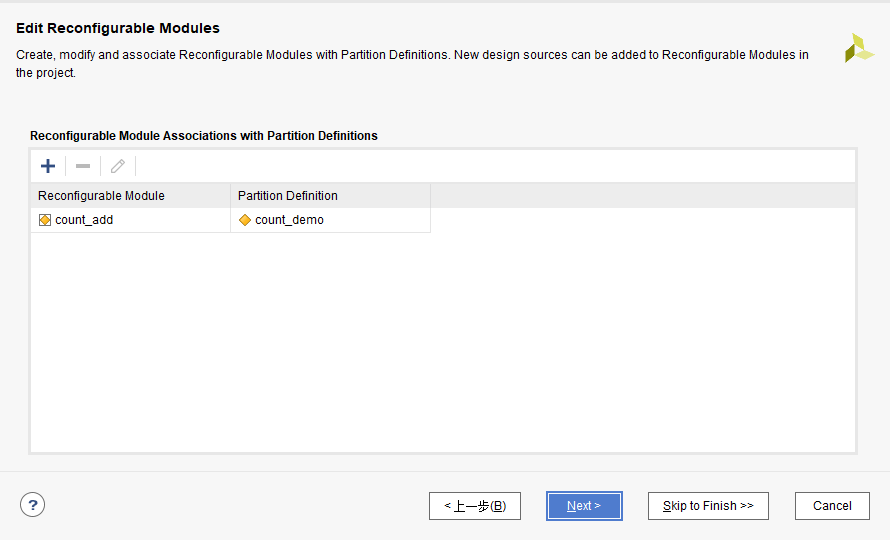

選擇左側導航欄的Partial Reconfiguration Wizard,開始添加RM

在這里插入圖片描述

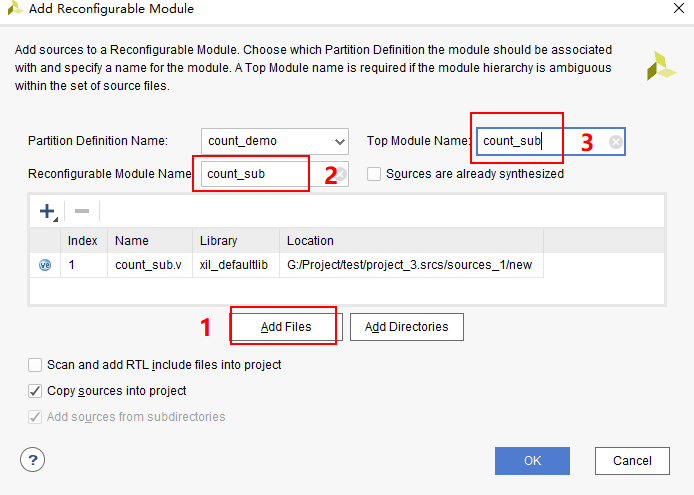

這里,點擊+號按鈕,出現下面對話框,首先點擊Add Files,選擇count_sub.v;然后輸入Reconfiguration Module Name,由于我們只有一個模塊,因此top的name可以不填;如下圖,Next

在這里插入圖片描述

在這一步如果我們使用dcp文件和wrapper文件的話,需要把它們都添加進來

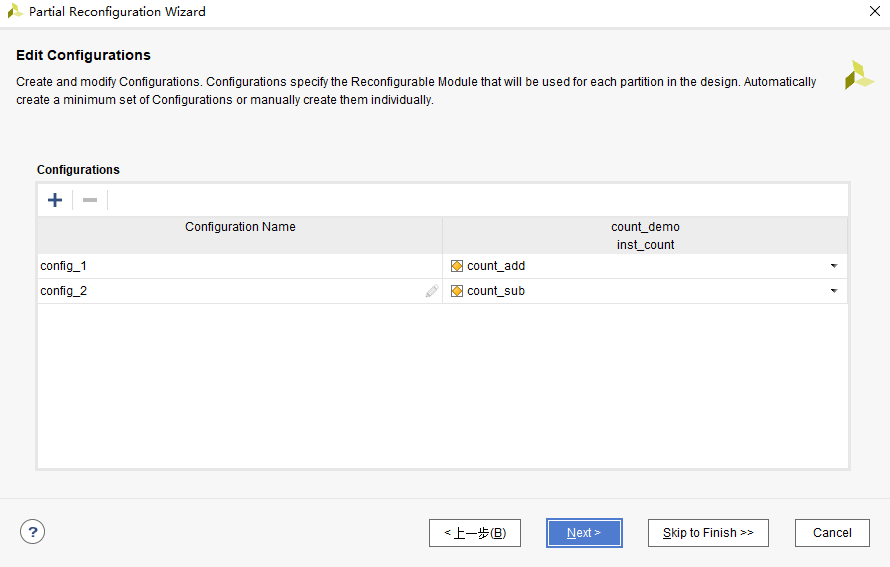

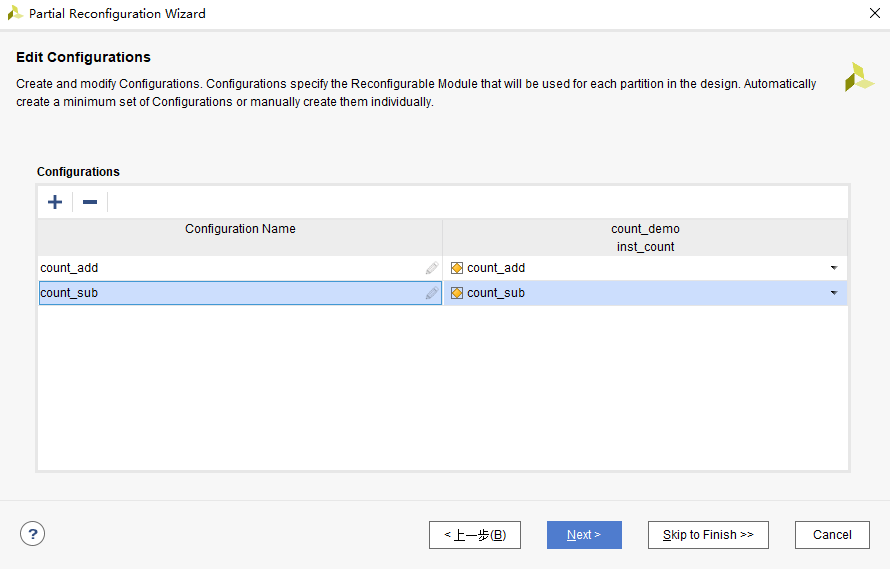

編輯配置,點擊automatically create configurations,如果在這個界面沒看到這個auto…按鈕,就先返回到上一步,再next到這個界面,總會出現的;點擊后出現下面的界面:

在這里插入圖片描述

我們修改配置的名字如下,next

在這里插入圖片描述

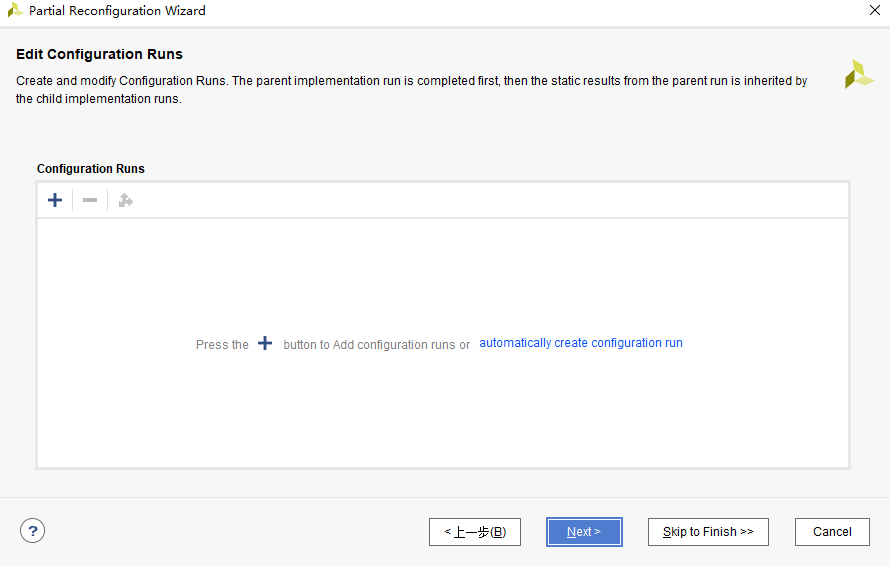

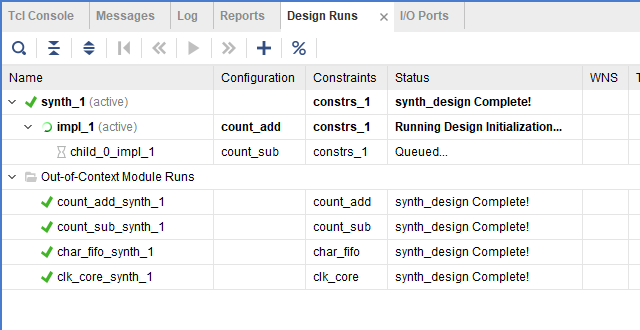

配置runs,也是先點擊automatically create configuration run

在這里插入圖片描述

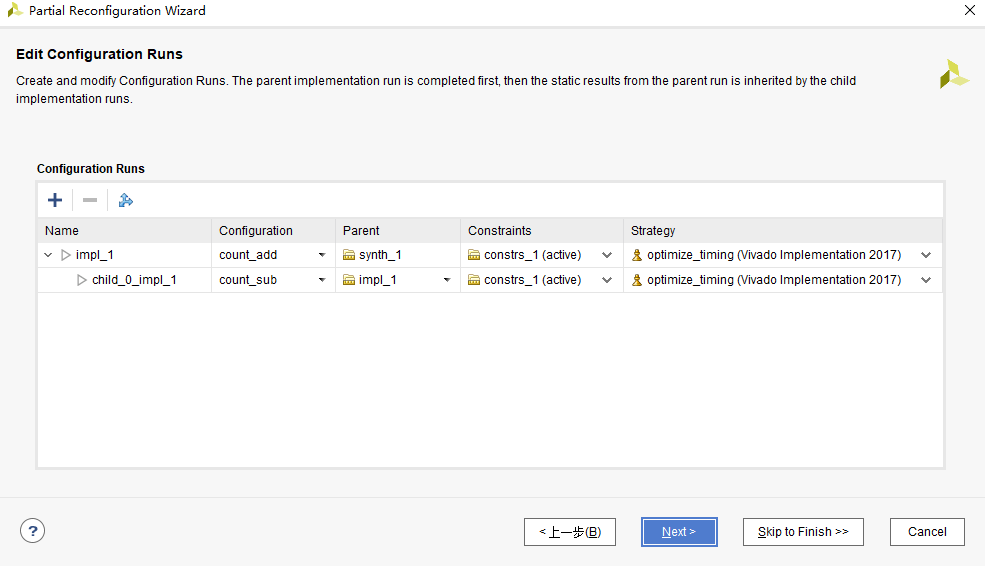

在這里插入圖片描述

這個圖意思是工程中有兩個implention runs,第一個叫impl_1,這個里面跑的是包含有count_add模塊的程序;第一個叫child_0_impl_1,這個里面跑的是包含count_sub模塊的程序。Next到Finish。

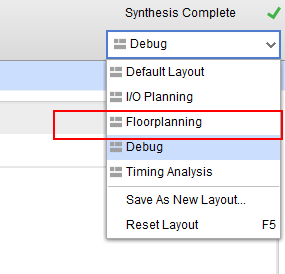

開始綜合,完成后點擊Open Synthesized Design,并在Vivado右上角,切換到Floorplanning視圖

在這里插入圖片描述

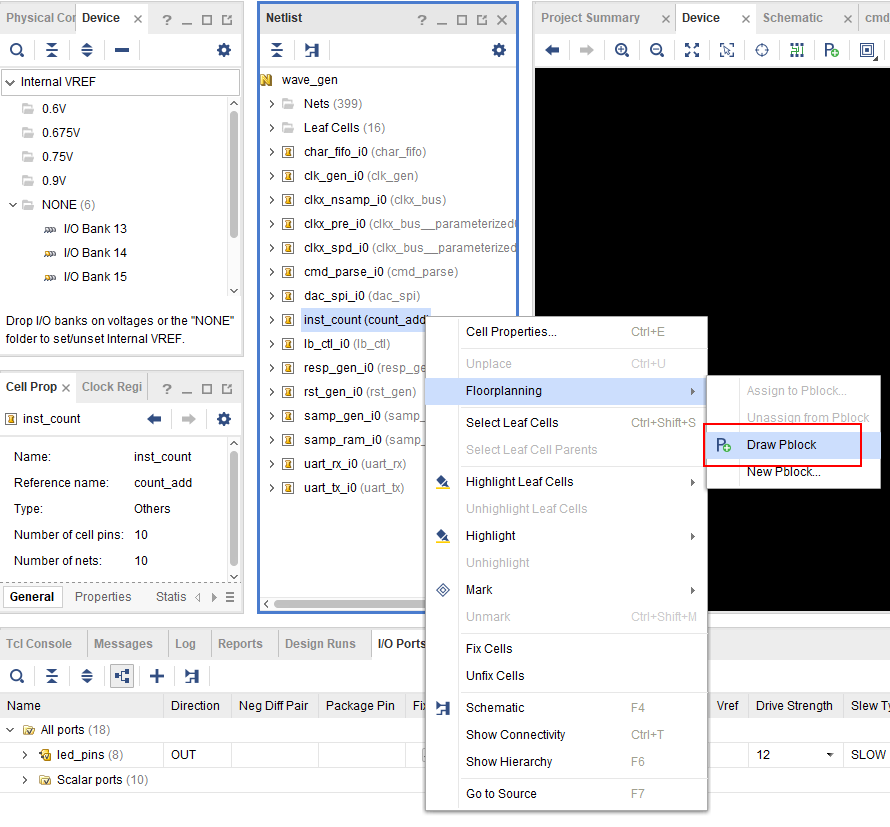

郵件inst_count并點擊Draw Pblock

在這里插入圖片描述

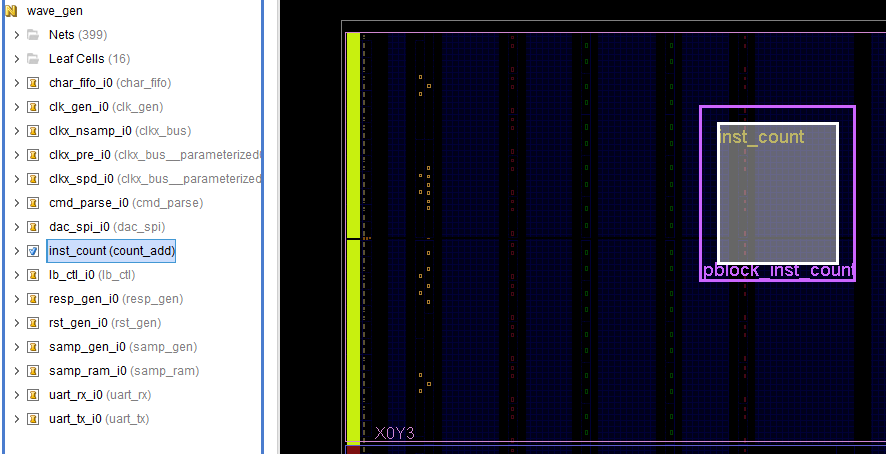

選擇一個區域作為Pblock

在這里插入圖片描述

繪制Pblock是有講究的,其中最簡單的兩個規則就是:

Pblock區域中包含的資源能可以覆蓋我們模塊需要的資源

不能與其他的Pblock沖突

當然,還有很多其他的規則,這里就不一一介紹了,如果Pblock沒畫好,很可能導致后面的DRC和Implementation不過。

關于該更多Pblock的說明,可以參考UG909手冊UG909

選中框之后,改一下框的屬性,將RESET_AFTER_RECONFIG的勾選中,意思是重新配置后,會復位這個Pblock里面的內容;再將SNAPPING_MODE改為Routing(或者設為On),意思是如果我們的邊界選的不太好,Vivado會自動處理,選off的話,就是完全按照我們指定的邊界。

在這里插入圖片描述

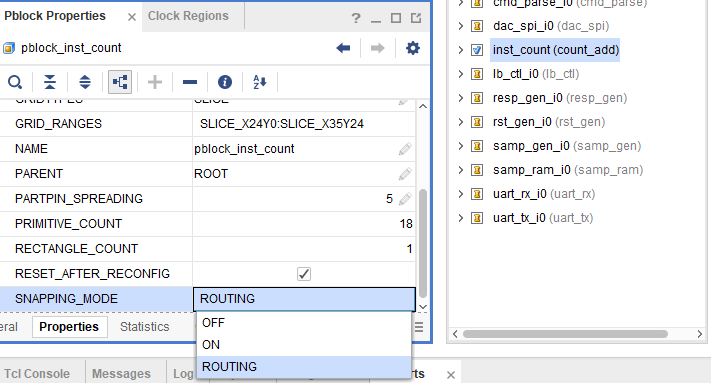

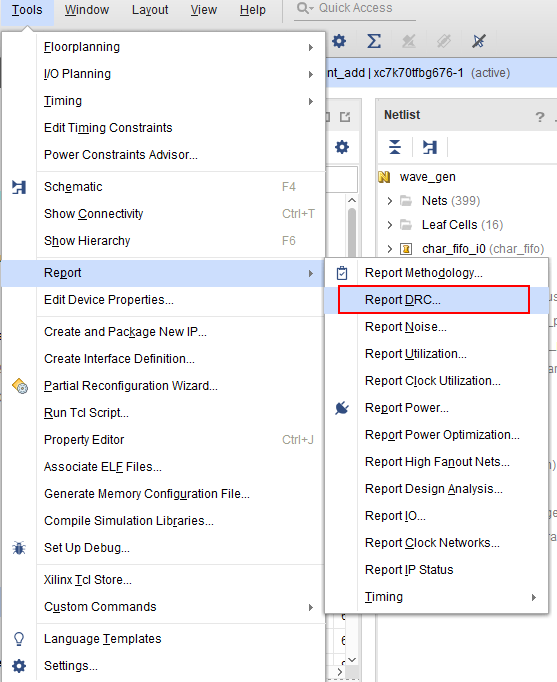

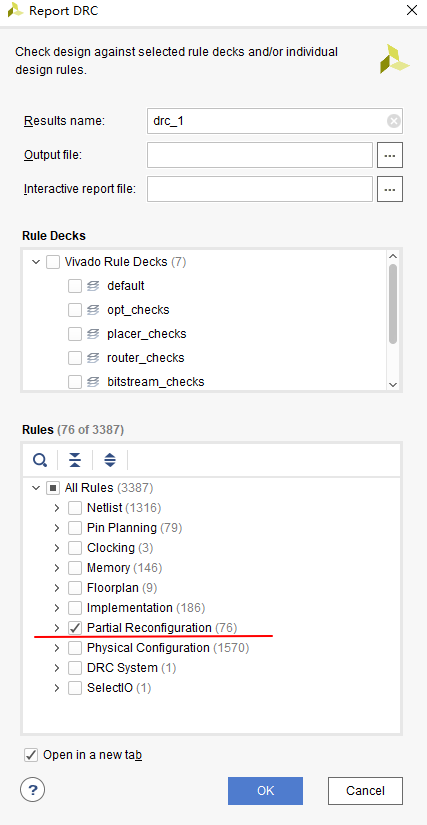

點擊Tools->Report->Report DRC

在這里插入圖片描述

只選擇PR即可

在這里插入圖片描述

如果提示No Violations Found,則說明上面的操作過程沒有問題。

Run Implementation,可以看到有兩個runs需要進行

補充小知識:Vivado中jobs和threads的區別?選擇多個jobs能加快實現速度么?

在這里插入圖片描述

Generate Bitstream,OK

在這一步進行前,Vivado會自動執行pr_verify,并生成

對于7系列的FPGA,會在impl_1文件夾下生成兩個bit文件:

wave_gen.bit和inst_count_count_add_partial.bit,第一個bit文件是整個工程且包含count_add模塊的bit文件,第二個bit文件是當我們需要進行Partial Reconfiguration的時候需要下載的bit文件;在child_0_impl_1文件夾下會生成一個bit文件inst_count_count_sub_partial.bit,是當我們需要進行Partial Reconfiguration的時候需要下載的bit文件。

對于UltraScale系列的FPGA,會在生成*_partial.bit的同時多出來一個*_partial_clear.bit,意思是在進行Partial Reconfiguration的時候,先下載*_partial_clear.bit把那一部分的內容先清空,再下載*_partial.bit進行配置。

使用Project模式的好處就是比較簡單,敲的指令也比較少,如果是Non-Project模式,在這中間還需要很多操作,雖然麻煩,但對我們理解它的工作模塊很有幫助,有興趣的同學可以再用Non-Project模式下操作一遍。

文章出處:【微信公眾號:OpenFPGA】

責任編輯:gt

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605129 -

計數器

+關注

關注

32文章

2259瀏覽量

94870

原文標題:Xilinx FPGA Partial Reconfiguration 部分重配置 詳細教程

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過DSP6455的MCBSP配置TLV320AIC20,如果想使用LINEI和LINEO,還需要哪些別的配置嗎?

帶你分析電池分選機的操作技巧

極化整流器的作用和工作過程

可調電源電路穩壓工作過程是什么

FPGA在圖像處理領域的優勢有哪些?

FPGA的配置模式有哪些?具體配置過程是怎樣的?

什么是物流agv叉車?操作簡單嗎?使用時需要注意什么?

如何用加載分散法將軟件中部分變量從內部RAM轉移到外部RAM?

FPGA開發過程中配置全局時鐘需要注意哪些問題

什么是電源模塊低溫操作檢測?該如何測試?

光纖傳輸信息時的工作過程

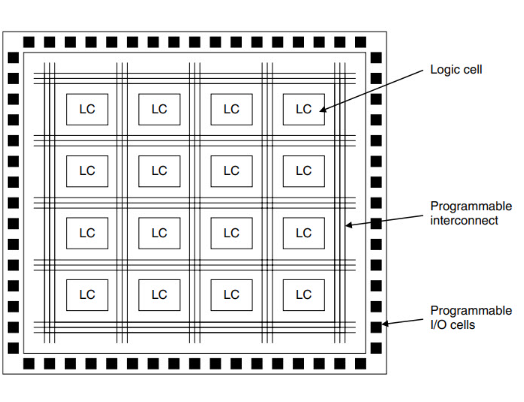

FPGA的內部結構工作過程

FPGA應用中部分重配置的操作過程

FPGA應用中部分重配置的操作過程

評論