目前從全球范圍來說,也就只有臺積電和三星這兩家能做到5納米工藝以下了。6月29日晚間,據外媒報道,三星宣布其基于柵極環繞型 (Gate-all-around,GAA) 晶體管架構的3nm工藝技術已經正式流片(Tape Out)。一直以來,三星與臺積電一直在先進工藝上競爭,據介紹,與5nm制造工藝相比,三星的3nm GAA技術的邏輯面積效率提高了35%以上,功耗降低了50%,性能提高了約30%,而且GAA架構性能也優于臺積電的3nm FinFET架構。

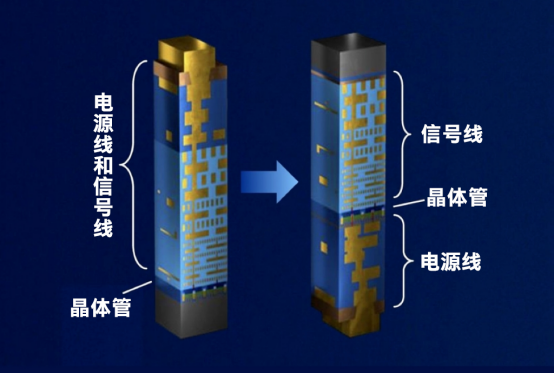

相較傳統 FinFET 溝道僅 3 面被柵極包覆,GAA 若以納米線溝道設計為例,溝道整個外輪廓都被柵極完全包裹,代表柵極對溝道的控制性更好。

與Synopsys合作完成流片

要完成GAA架構,需要一套不同于臺積電和英特爾使用的 FinFET 晶體管結構的設計和認證工具,因此三星與新思科技(Synopsys)合作,采用了Fusion Design Platform的物理設計套件(PDK)。三星早在2019年5月就公布了3nm GAA工藝的物理設計套件標準,并 2020 年通過工藝技術認證,這次雙方聯合驗證了該工藝的設計、生產流程。

流片也是由Synopsys 和三星代工廠合作完成的,旨在加速為 GAA 流程提供高度優化的參考方法。參考設計流程包括一個集成的、支持golden-signoff的 RTL 到 GDSII 設計流程以及golden-signoff產品。設計流程還包括對復雜布局方法和布局規劃規則、新布線規則和增加的可變性的支持。

該流程基于單個數據模型并使用通用優化架構,而不是組合點工具,針對的是希望將 3nm GAA 工藝用于高性能計算 (HPC)、5G、移動和高級人工智能 (AI) 應用中的芯片的客戶。三星代工設計技術團隊副總裁 Sangyun Kim 表示:“三星代工是推動下一階段行業創新的核心,我們不斷進行基于工藝技術的發展,以滿足專業和廣泛市場應用不斷增長的需求。

三星電子最新的、先進的 3nm GAA 工藝受益于我們與 Synopsys 的合作,Fusion Design Platform 的快速完成也令3nm 工藝的承諾可以達成,這一切都證明了關鍵聯盟的重要性和優點。”三星、Synopsys并沒有透露這次驗證的3nm GAA芯片的詳情,只是表示,GAA 架構改進了靜電特性,從而提高了性能并降低了功耗,可滿足某些柵極寬度的需求。

這主要表現在同等尺寸結構下,GAA 的溝道控制能力強化,尺寸進一步微縮更有可能性。與完善的電壓閾值調諧一起使用,這提供了更多方法來優化功率、性能或面積 (PPA) 的設計。Synopsys 數字設計部總經理 Shankar Krishnamoorthy 表示:“GAA 晶體管結構標志著工藝技術進步的一個關鍵轉折點,這對于保持下一波超大規模創新所需的策略至關重要。”

“我們與三星代工廠的戰略合作支持共同交付一流的技術和解決方案,確保這些擴展趨勢的延續以及這些為更廣泛的半導體行業提供的相關機會。”Synopsys 的Fusion 設計平臺包括用于數字設計的 Fusion Compiler、IC Compiler II 布局布線和 Design Compiler RTL 綜合、PrimeTime 時序簽核、StarRC 提取簽核、IC Validator 物理簽核和 SiliconSmart 庫表征。

3nm GAA工藝流片意味著該工藝量產又近了一步,不過最終的進度依然不好說,三星最早說在2021年就能量產,后來推遲到2022年,但是從現在的情況來看,明年臺積電3nm工藝量產時,三星的3nm恐怕還沒準備好,依然要晚一些。

三星臺積電,切入GAA的時間點不同

3 納米 GAA 工藝技術有兩種架構,就是 3GAAE 和 3GAAP。這是兩款以納米片的結構設計,鰭中有多個橫向帶狀線。這種納米片設計已被研究機構 IMEC 當作 FinFET 架構后續產品進行大量研究,并由 IBM 與三星和格芯(Globalfoundries)合作發展。三星指出,此技術具高度可制造性,因利用約 90% FinFET 制造技術與設備,只需少量修改的光罩即可。另出色的柵極可控性,比三星原本 FinFET 技術高 31%,且納米片信道寬度可直接圖像化改變,設計更有靈活性。

對臺積電而言,GAAFET(Gate-all-around FETs)仍是未來發展路線。N3 技術節點,尤其可能是 N2 節點使用 GAA 架構。目前正進行先進材料和晶體管結構的先導研究模式,另先進 CMOS 研究,臺積電 3 納米和 2 納米 CMOS 節點順利進行中。

臺積電還加強先導性研發工作,重點放在 2 納米以外節點,以及 3D 晶體管、新內存、low-R interconnect 等領域,有望為許多技術平臺奠定生產基礎。臺積電正在擴大 Fab 12 的研發能力,目前 Fab 12 正在研究開發 N3、N2 甚至更高階工藝節點。

作者:Luffy Liu 來源:電子工程專輯

編輯:jq

-

IC

+關注

關注

36文章

5978瀏覽量

176023 -

三星電子

+關注

關注

34文章

15873瀏覽量

181187 -

臺積電

+關注

關注

44文章

5685瀏覽量

166850 -

柵極

+關注

關注

1文章

174瀏覽量

21017 -

5nm

+關注

關注

1文章

342瀏覽量

26109

原文標題:聚焦 | 三星3nm GAA芯片流片成功,性能優于臺積電的3nm FinFET?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星電子:18FDS將成為物聯網和MCU領域的重要工藝

三星宣布其基于柵極環繞型晶體管架構的3nm工藝技術已經正式流片

三星宣布其基于柵極環繞型晶體管架構的3nm工藝技術已經正式流片

評論