基于FPGA的DDS設計方案1 DDS技術簡介隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。

直接數字頻率合成技術(DDS) 是把一系列數據量形式的信號通過D/A轉換器轉換成模擬量形式的信號合成技術。DDS具有很多優點,比如:頻率轉換快、頻率分辨率高、相位連續、低功耗、低成本與控制方便。

DDS技術滿足了人們對于速度穩定性的需求,但是在一些控制較為復雜的系統中,DDS專用芯片不能很好的貼合要求。利用現場可編程門陣列(FPGA)實現DDS具有很大的靈活性,基本能滿足現在通信系統的使用要求。

2 DDS結構原理2.1 基本結構 DDS基本結構框圖主要由參考頻率源、相位累加器、ROM查找表、DAC轉換器、低通濾波器等構成。

相位累加器以一定的步長做累加, 而波形函數存儲在ROM查找表中, 將相位累加器輸出的相位值作為地址,尋找存儲在ROM查找表中的波形函數的幅度值,從而完成相位到幅值的轉換。其中,參考頻率源一般是一個晶體振蕩器,要求具有高穩定性,用于DDS中各部件之間的同步。

2.2 基本原理

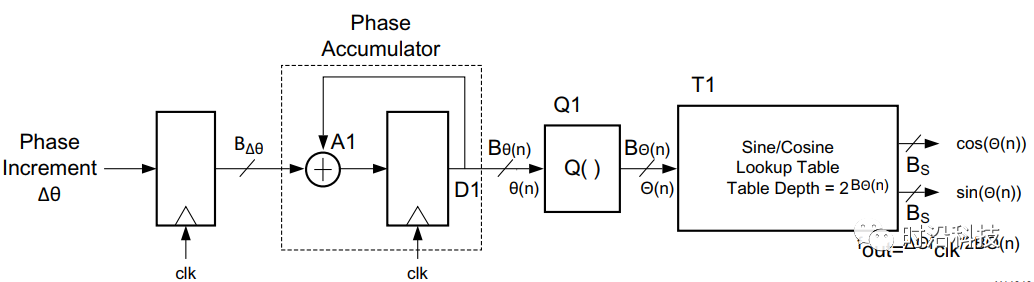

DDS Core結構圖

上圖為DDS Core結構圖,?θ是相位增量(對應圖1中的頻率控制字K),B?θ 為相位累加器的位數,clk是參考時鐘(對應圖1中的參考頻率源),A1、D1構成積分器(相位累加器),θ(n)是相位累加器輸出的相位,Q1為量化器,用于將相位累加器位數與查找表地址之間的匹配,?(n)為查找表輸入地址,B?(n) 為查找表輸入地址位數,T1為查找表。

下面介紹DDS設計過程中常用到的公式,主要是輸出頻率公式及其變形。

輸出頻率

相位增量

頻率分辨率

相位累加器位數

3 基于FPGA的 DDS實現For example:

設計一個參考時鐘為100MHz,頻率分辨率要求能夠達到0.03Hz,輸出sin信號頻率為5.00000005MHz、查找表地址12位;

理論分析:

已知頻率分辨率?f與參考時鐘f_clk,帶入相位累加器位數公式計算

B?θ = 31.634318

由于位數為整數,取整數32,所以實際的頻率分辨率為

?f = 0.023283064365386962890625Hz

將其帶入相位增量公式計算,取整數

?θ = 21474836694.7483648≈21474836

相位累加器輸出32位,而查找表輸入地址為12位,取相位累加器高12位作為查找表輸入地址

3.1 利用RTL實現DDS使用matlab產生sin?(θ)數據,θ?[0,π],點數為2^12=4096,并保存在FPGA的memory中。

wid = 12;

len = 2^wid;

amp = 10000;

t=0:2*pi/len:2*pi - 2*pi/len;

y = round(sin(t)*amp);

plot(y);

相位累加器就是一個積分器,很容易用FPGA實現。最終FPGA仿真結果如下,clk為參考時鐘,phase為相位累加器輸出,addr為查找表地址,cos_i、sin_q為信號輸出。

3.2 利用Xlinx DDS IP實現上述已經對DDS理論進行了詳細概述,利用Xlinx DDS IP實現上述例子相對容易的多,只需要填入對應的參數信息。

需要注意的是,輸入相位端口S_AXIS_PHASE與輸出信號端口M_AXIS_DATA的格式,通過設計界面的Information查看,CHAN_0_POFF為初始相位,沒有特殊要求一般設置為0,CHAN_0_PINC為相位增量?θ。

4 DDS用途DDS用途非常廣泛,后續會利用Xlinx DDS IP設計一些有趣的信號,例如線性調頻信號、非重復掃描系統等。

編輯:jq

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605238 -

DDS

+關注

關注

21文章

636瀏覽量

152850 -

累加器

+關注

關注

0文章

50瀏覽量

9475 -

xlinx

+關注

關注

0文章

5瀏覽量

4503

原文標題:基于FPGA的DDS設計方案

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用FPGA加上DAC902做DDS時候,出現DAC902的時鐘串擾進我輸出的波形中的問題怎么解決?

DDS通信中間件——DCPS規范(下)

LM4890采用差分設計方案,為什么沒有聲音?怎么解決?

Xilinx DDS IP核的使用和參數配置

DDS通信中間件——DCPS規范(上)

基于FPGA的CCD工業相機系統設計

電磁頻譜管理系統設計方案

基于FPGA的SPI Flash控制器的設計方案

基于FPGA的FIR數字濾波器設計方案

探究關于FPGA的DDS設計方案

探究關于FPGA的DDS設計方案

評論