光纖通道(FC)是一個高性能的雙向點對點串行數據通道。光纖通道的標準是由T11標準委員會(美國國家信息技術標準化委員會下屬的技術委員會)制定的,它是一個為適應日益增長的高性能信息傳輸要求而設計的計算機通訊協議。FC集中了IO通道和網絡的優點,它既支持IO通道所要求的帶寬與可靠性,又支持網絡技術的靈活性與連接能力,使得在同一物理接口上運行當今流行的通道標準和網絡協議成為可能。目前,FC已被作為未來航空電子統一網絡的一種主要聯網標準。本文討論了一種采用片上系統(SOC)技術來設計FC協議芯片的方案,分析了SOC設計方法的特點及其與傳統的嵌入式系統設計方法的不同點,為今后在航電系統的設計中推廣使用SOC技術奠定了基礎。

FC工作原理簡介

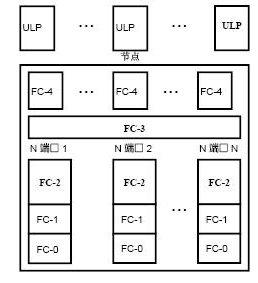

光纖通道所支持的物理介質包括光纖、雙絞線、同軸電纜等,本文統稱其為光纖。物理上,FC可被看成是稱為N端口的多個通信點的連接,這些N端口可以通過交換網進行連接,且通過集線器構成仲裁環路,也可以通過點對點的鏈路進行連接。如圖1所示,FC協議可以分成一系列的功能層次,各功能層次簡述如下。

圖1 FC的層次結構圖

FC-0層

FC-0定義了接口和介質的物理特性,規定了收發器和各種物理媒介的光電參數。按照實現器件的不同,FC可具有不同的數據傳輸率:133Mbit/s,266Mbit/s,530Mbit/s,1.0625Gbit/s等。

FC-1層

FC-1定義了編解碼和傳輸協議,它采用直流平衡8b/10b碼。一個8位字節編碼為10位進行傳輸,然后在接收端再進行解碼。一部分具有特殊特性的沒有使用的編碼點被用來組成特殊字符,以形成信令和幀描述的有序集。

FC-2層

FC-2層是信號傳輸協議層。它規定了數據傳輸的規則,提供了數據塊從一個端口傳輸到下一個端口的傳輸機制,定義了可由FC-4使用的功能和設備,FC-4可以只采用其中的一個子集。這一層描述了如下概念:

(1)節點和N端口及相應的標識符;

(2)通訊模型;

(3)拓撲結構;

(4)服務類;

(5)通用交換網模型;

(6)FC-2的構造塊及體系結構;

(7)幀格式;

(8)序列;

(9)交換。

FC-3層

FC-3層為一些高級特性提供了所需要的通用服務,例如:

(1)分類:并行使用若干個N端口來增加帶寬,以便通過多重連接傳輸一個單一信息。

(2)查詢組:使數量多于一個的端口能響應相同的別名地址。這一服務通過減少接觸到忙N端口的機會來提高效率。

(3)多播:將一個傳輸發送到多個目標端口,包括發送到一個交換網上的所有N端口(廣播),或只發送到交換網上某些N端口。

FC-4層

FC-4層是FC協議的最高層,它規定了上層協議到FC協議的映射。當前映射的協議有:小型計算機系統接口(SCSI)、智能外設接口3(IPI-3)、高性能并行接口(HIPPI)、INTERNET協議(IP)、IEEE802.2、單字節命令碼集映射(SBCCS)。另外,FC-AE還描述了一個基于1553B的上層協議映射。

FC-PH的物理模型

FC通路在物理上至少由2個節點組成。每個節點可以由多個N端口組成,每個N端口提供FC-0、FC-1、FC-2的功能。FC-3是可選的,它為多個N端口和FC-4提供通用服務。FC節點的組成如圖2所示。

圖2FC節點的組成

每個端口由一對光纖組成,一個用于輸入,一個用于輸出。這一對按相反方向傳輸的光纖和收發器組成FC鏈路,完成數據傳輸。

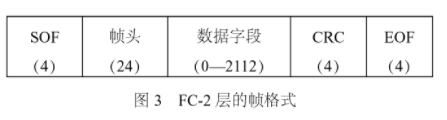

FC-2層的幀格式

FC-2層的幀格式如圖3所示。

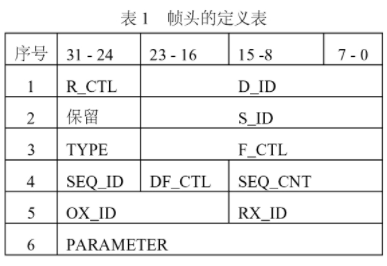

幀起始定界符SOF是一個有序集,4個8b字符,根據不同幀的類型有不同的碼字;幀頭,24個8b字符,詳見表1;數據字段,0–2112個8b字符;CRC,4個8b字符,它對幀頭部分和數據字段部分進行校驗,其編碼多項式是X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X+1;幀結束定界符EOF是一個有序集,4個8b字符,根據不同幀的類型有不同的碼字。

FC協議芯片的設計概述

功能概述

FC芯片的功能是實現圖1中的FC-PH,即FC-2、FC-1、FC-0層的協議;每個FC芯片支持2個N端口,可構成如圖2所示的FC節點;支持的數據傳輸率為1.0625Gbits/s。

基于SoC的設計考慮

基于SoC的芯片設計和嵌入式模塊板的設計有相似之處,但不能把SoC設計簡單地理解為對嵌入式模塊板的小型化,它們的主要區別如下:

(1)嵌入式模塊板的設計是使用現有的CPU芯片和外設芯片來實現的,而SoC設計是由CPU內核與各種功能模塊內核實現的。

(2)由上文可知,嵌入式模塊板的設計是在已經設定的規則框架中進行的,這些規則就是各種芯片的使用手冊,而SoC設計可以根據設計需求,自行設計規則,再設計各種功能模塊內核,以滿足功能要求并使得資源利用最優化。

(3)嵌入式模塊板的設計,由于受到CPU芯片引腳的限制,外設芯片大多掛在CPU的一條外部總線上,難免會有總線爭用,而SoC設計原則上芯片內部可以并行工作的總線個數沒有限制,應充分利用這個特性,合理確定體系結構,避免總線爭用。

(4)嵌入式模塊板的設計,其軟硬件的設計都有固定的模式,而SOC設計先要根據設計需求,確定軟硬件的交會點,確定軟硬件協同的規則,才能達到資源利用最優化的目的。

首先,要確定軟硬件的交會點。軟硬件的交會點放在FC-2層的“序列”上。因為“序列”負責整塊數據的收或發,當數據塊的長度超過圖3所示的數據長度時,要分為若干個相關的數據幀來傳輸。數據幀的相關性表現在如表1所示的幀頭中,只有序列計數字段SEQ_CNT發生改變。因此,軟件將負責提供幀頭的部分信息和數據,由硬件負責數據成幀和以后的工作。其次,在設計芯片的體系結構時,要充分使用芯片內部的并行工作的總線。最后,為便于本芯片的測試,對上層接口ULP,先考慮使用PCI總線,以便實現基于PCI接口的FC網卡。根據今后實際使用需求,ULP將按需設計。

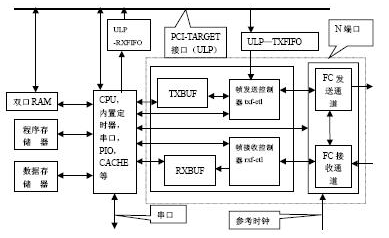

芯片的結構

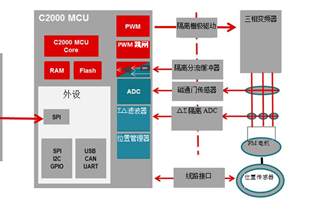

根據3.2節的討論,FC協議芯片的結構框圖如圖4所示。FC協議芯片對上層的接口(ULP)采用PCI接口,由芯片內置的PCI-TARGET內核實現。

圖4 FC協議芯片的結構框圖

圖4中虛線方框部分構成了FC的N端口,整個芯片中有2個N端口。每個FC-N端口由“FC收發通道”和“FC幀收發控制器”2層構成。“FC收發通道”與光電接口模塊配合可實現FC-0層、FC-1層和FC-2層中數據幀收發的功能。該層為上層接口提供用于數據幀收發的片內FIFO通道。“FC幀收發控制器”實現FC-2層的數據幀打包、開包和檢錯。另外,通過芯片內嵌的軟件模塊實現FC-2層的序列和交換協議;同時提供ULP接口。下文對FC通道、幀收發控制器、CPU內核及ULP 接口作分別討論。

FC收發通道模塊的設計

功能概述

該模塊主要完成FC-2層幀的收發,包括:完成SERDES(串-并互相轉換模塊)與光電接口的連接、完成FC-1層的8b/10b編解碼、FC-2層幀級的CRC校驗和FC有序集碼的譯碼;同時利用內置存儲器構成FIFO與FC芯片后端模塊進行數據交換的緩沖區。

組成結構

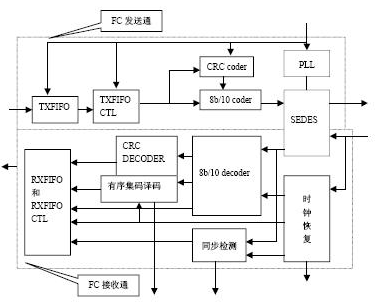

該模塊分為“FC發送通道”和“FC接收通道”,如圖5所示。在收發通道之間提供多種自環測試的通路(未在圖中標出)。

“FC發送通道”主要由以下單元組成:

(1)并-串轉化單元;

(2)發送時鐘鎖相環;

(3)8b/10b編碼單元;

(4)CRC校驗生成單元;

(5)TX-FIFO發送控制單元;

(6)TX-FIFO數據輸入緩沖單元;

(7)自環控制單元。

“FC接收通道”主要由以下單元組成:

(1)串-并轉化單元;

(2)接收時鐘鎖相環;

(3)時鐘恢復單元;

(4)同步檢測單元;

(5)有序集譯碼單元;

(6)8b/10b解碼單元;

(7)CRC校驗單元;

(8)RX-FIFO發送控制單元;

(9)RX-FIFO數據輸出緩沖單元;

(10)自環控制單元。

圖5FC通道結構框圖

數據收發緩沖區的定義

數據緩沖區TX-FIFO、RX-FIFO的定義如表2所示:途中發送緩沖區是33位,低32位是發送的數據,第32位用于表示當前碼字是否為有序集碼。接收緩沖區是36位,低32位是接收到的數據,高位部分保存FC-2幀的CRC校驗結果、8b/10b碼的譯碼校驗等信息。

5.1 功能概述

FC芯片中有兩路“FC幀收發模塊及其數據緩沖器”,它們實現FC-2層協議中的幀打包、開包。它是整個系統的軟硬件交會點,是整個系統的核心,其關鍵在于制定相關的設計規則。

5.2 數據緩沖區的使用規則

根據多路總線并行工作的原則,設置四塊獨立的數據緩沖區,采用雙口RAM,用于在CPU和幀收發器之間交換數據。收發數據緩沖區的使用規則如下:

(1)發送緩沖區TXBUF。根據圖3所示的FC-2幀格式,該緩沖區用于存放幀頭和有效數據。前24個字節是固定存放幀頭的幀頭區,后面是有效數據區。發送時,模塊TXF-CTL從幀頭區取幀頭信息發送,根據寄存器中發送起始地址(TXOFFSET)和發送個數(TXCOUNT)的值從TXBUF中連續取數據發送。這里,只設置1個幀頭區,是考慮到在“序列”中幀頭具有相關性,同時1個幀頭區不存在多個區域的切換,簡化了硬件實現。

(2)接收緩沖區RXBUF。該緩沖區采用循環隊列的方式,由模塊RXF-CTL順序寫入數據,數據的存儲順序如圖3所示的FC-2幀格式。在完成1幀數據接收后,模塊RXF-CTL要在寄存器中表明當前幀在RXBUF中的接收起始地址(RXOFFSET)和接收到的個數(RXCOUNT)。CPU讀取寄存器RXCOUNT后,該寄存器自動清零。上述使用規則是整個系統進行SoC設計的要點。

工作過程

數據的發送過程發送:

(1)CMD_RESET。模塊TXF-CTL復位,進入空閑態。

(2)CMD_TEST:由CPU直接控制數據的發送,模塊TXF-CTL進入空閑態。

(3)CMD_START_TX1:在空閑態并且CMD_TEST和CMD_START_TX2都無效時,進入按幀發送數據的狀態,模塊TXF-CTL發出SENDING信號。模塊TXF-CTL先向FC發送通道的TX-FIFO發送有序集碼lDLE(K28.5D21.4D21.5D21.5);根據SOF碼型寄存器發送相應的SOF;然后從TXBUF的幀頭區取數據依次發送;以后,如果數據從TXBUF取,則根據寄存器發送起始地址(TXOFFSET)和發送個數(TXCOUNT)從TXBUF中取出對應的數據發送;發送完有效數據后,再根據EOF碼型寄存器發送相應的EOF;最后再發一個有序集碼IDLE(K28.5D21.4D21.5D21.5)。一幀數據發完后,將SENDING信號清零,CMD_START_TX1清零,發中斷信號INTTXi,然后回到空閑態。發送過程只有CMD_RESET可以中斷。

(4)如果數據來在ULP-FIFO,則讀發送個數(TXCOUNT),從ULP-FIFO中取數發送,若發送個數(TXCOUNT)大于FC-2幀規定的長度,則按2112字節的長度分多幀發送,每幀完畢,自動修改幀頭中的幀記數值,并且自動選擇相應的SOF和EOF定界符;若發送的過程中ULP-FIFO空,則自動結束這一幀的發送,并啟動超時定時器,等待ULP-FIFO中的數據。當發送個數(TXCOUNT)規定的數據發完后,或者超時,則將SENDING信號清零,CMD_START_TX1清零,發中斷信號INTTXi,然后回到空閑態。發送過程只有CMD_RESET可以中斷。

(5)CMD_START_TX2:在空閑態當CMD_START_TX2有效時,模塊TXF-CTL按有序

集碼寄存器和有序集碼參數寄存器的定義發送有序集碼。

數據的接收過程

數據的接收有兩種方式:由CPU直接控制;由RXF-CTL按FC-2幀格式接收數據。CPU可通過FC-2幀收發控制器的寄存器向模塊RXF-CTL發命令來控制數據發送:

(1)CMD_RESET。模塊TXF-CTL復位,進入空閑態。

(2)CMD_TEST:由CPU直接控制數據的接收。

(3)CMD_START_RXi:在空閑態并且CMD_TEST無效時,進入按幀接收數據的狀態。模塊RXF-CTL從FCSET-A的RX-FIFO中收到有序集碼SOF后,發出RECEIVE信號,表示已經開始1幀數據的接收。模塊RXF-CTL將收到的數據依次寫入循環緩沖區RXBUF。再收到任一個有序集碼后,1幀數據接收結束,將RECEIVE信號清零。更新寄存器接收起始地址(RXOFFSET)和接收到的個數(RXCOUNT)。如果接收到的CRC碼無效或者最后一個有序集碼不是EOF,則將接收有錯(RXERR)置‘1’,否則發出INTRXi中斷信號,表示收到1幀正確的數據。繼續下一幀的數據的接收。在1幀數據接收的過程中,只有CMD_RESET可以中斷;如果尚未開始接收1幀數據,則CMD_TEST可使其回到空閑態。CPU讀寄存器RXOFFSET、RXERR和RXCOUNT可知道接收到的數據存放的地址和個數以及數據幀是否有效。

另外CMD_START_Rxi還用來控制FC接收通道中的RX-FIFO控制器。CMD_START_Rx1控制FC接收通道按FC-2幀接收數據存入RX-FIFO;CMD_START_Rx2控制FC接收通道接收所有數據(除了連續的IDLE有序集碼之外)存入RXFIFO。

內置CPU的配置及ULP的設計

內置CPU通過嵌入的軟件完成FC-2層的序列和交換的協議,同時實現ULP與上層的通訊。

CPU外設的配置

CPU配置的外設和總線接口定義如下:

(1)兩個RS232串行口。

(3)兩個FC-2層通訊用的定時器:FCTIMER1,FC-TIMER2。

(4)接收兩路FC-2幀收發控制器中斷的PIO:INTFRAME-PIO。兩個接受來自RX-FIFO的有序集譯碼的PIO:ORDERSET-PIO1,ORDERSETPIO2。兩個內總線接口,用于操作兩路FC-2幀收發控制器。可根據操作功能需要,對FC-2幀收發控制器的各寄存器進行定義。

(5)四個獨立的連接收發數據緩沖區的內總線接口。

(6)三條獨立的存儲器總線接口:雙口RAM、程序存儲器和數據存儲器。

(7)與ULP交換數據的ULP-RXFIFO接口。

(8)與ULP握手的ULP-PIO接口。

ULP的數據通道

如圖4所示,FC芯片對ULP提供了兩種數據通道:雙口RAM和FIFO。雙口RAM通道:可根據ULP的需要劃分成若干分區,ULP可通過PCI接口對它存取數據。FC芯片的內置CPU從雙口RAM中讀數據,放到TXBUF中,然后啟動“幀發送模塊”打包發送;接收數據時,CPU從RXBUF中讀取數據,存到雙口RAM的相應的數據分區中,通知ULP來取數據。這種數據通道對需要確認,出錯要重傳的消息比較有效。

FIFO通道:ULP將數據通過PCI接口寫到ULP-TXFIFO中,CPU設定“幀發送模塊”從ULP-TXFIFO中取數據,“幀發送模塊”在數據打包時,從ULP-TXFIFO中取數據;接收數據時,CPU從RXBUF中讀取數據,存到ULP-RXFIFO。這種數據通道對視頻數據等實時性要求高的消息比較有效。

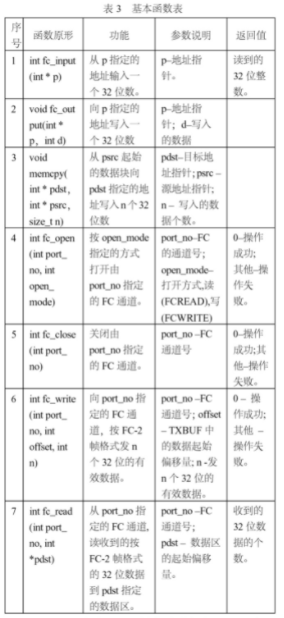

FC芯片嵌入軟件的基本操作函數

FC芯片的嵌入軟件要完成FC-2層的交換、序列、幀收發、差錯控制、流量控制等功能。它們需要調用的基本操作函數如表3所列。這些基本操作函數是與硬件平臺相關的函數,在平臺上所作的其他函數將與硬件平臺無關。這樣,有利于軟硬件協同開發,互相隔離錯誤。這是SOC設計的又一個重要原則。

結論

目前,高端的FPGA中已內嵌了適應高速傳輸的收發器、鎖相環和大量的存儲器,本文討論的FC協議芯片可以在這類FPGA上實現原型樣機。光纖通道以其傳輸速度高、兼容性好等特點在未來的航空電子統一網絡中將得到廣泛的應用,本文討論的FC協議芯片將為這一應用奠定物質基礎。本文以FC協議芯片的設計為例,介紹了基于SoC設計的思考重點和SoC設計的基本原則,它將有助于在航電系統的設計中推廣使用SoC技術。

責任編輯:gt

-

芯片

+關注

關注

456文章

51154瀏覽量

426268 -

光纖

+關注

關注

19文章

3950瀏覽量

73481 -

soc

+關注

關注

38文章

4199瀏覽量

218806

發布評論請先 登錄

相關推薦

采用片上系統技術實現FC協議芯片的方案設計

采用片上系統技術實現FC協議芯片的方案設計

評論