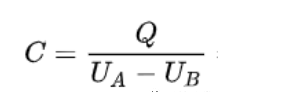

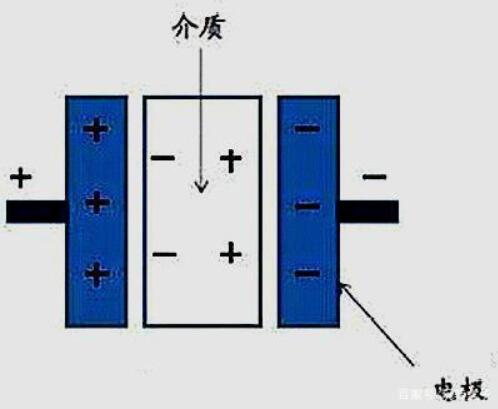

1 電容的定義我們最早接觸電容是在中學(xué)物理中關(guān)于電路的部分。電容器的定義為:兩個(gè)相互靠近的導(dǎo)體,中間夾一層不導(dǎo)電的絕緣物質(zhì),這就構(gòu)成了電容器。當(dāng)電容器的兩個(gè)極板之間加上電壓時(shí),電容器就會(huì)儲(chǔ)存電荷。電容器的電容量在數(shù)值上等于一個(gè)導(dǎo)電極板上的電荷量與兩個(gè)極板之間的電壓之比。電容器的電容量的基本單位是法拉(F)。在電路圖中通常用字母C表示電容元件。

從這個(gè)定義來(lái)說(shuō),電容值的大小:

那么電容就是是指在給定電位差下自由電荷的儲(chǔ)藏量,表征容納儲(chǔ)存電荷的能力。一般來(lái)說(shuō),電荷在電場(chǎng)中會(huì)受力而移動(dòng),當(dāng)導(dǎo)體之間有了介質(zhì),則阻礙了電荷移動(dòng)而使得電荷累積在導(dǎo)體上,造成電荷的累積儲(chǔ)存,儲(chǔ)存的電荷量則稱為電容。

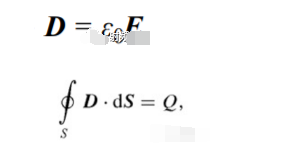

根據(jù)麥克斯韋方程中高斯電場(chǎng)定律,通過(guò)任意封閉空間的電通量等于該空間中的總電量。

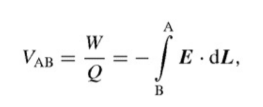

電壓就是兩個(gè)平板的電勢(shì)差,就是沿著電場(chǎng)線方向把電荷Q從A點(diǎn)移動(dòng)到B點(diǎn)產(chǎn)生的能量損失,即:

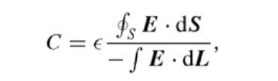

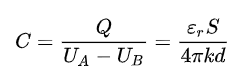

因此電容的表達(dá)式也就可以表述為:

通過(guò)上式可以看出電容與電荷量或者電勢(shì)無(wú)關(guān),只與電場(chǎng)強(qiáng)度有關(guān)。從物理意義上來(lái)說(shuō),電容就是在電學(xué)系統(tǒng)中儲(chǔ)存電能或者等效電通量的能力。

我們接著回到電容的最初定義,C=Q/(V1-V2)。

上式是基于電場(chǎng)強(qiáng)度不變的均勻電場(chǎng)推導(dǎo)出來(lái)的電容公式。其中,UA-UB為兩平行板間的電勢(shì)差,εr為相對(duì)介電常數(shù),k為靜電力常量,S為兩板正對(duì)面積,d為兩板間距離。這個(gè)可以得出一個(gè)比較有意義的結(jié)論:電容正比于電容器面積和介電常數(shù)e,反比于電容器的距離d。也就是說(shuō),面積越大,介電常數(shù)越高,電容越大,距離越遠(yuǎn),電容越小。

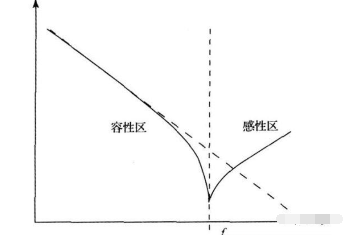

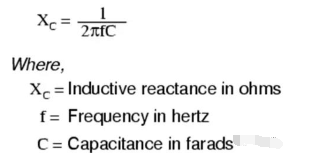

任何靜電場(chǎng)都是由許多個(gè)電容組成,有靜電場(chǎng)就有電容,電容是用靜電場(chǎng)描述的。一般認(rèn)為:孤立導(dǎo)體與無(wú)窮遠(yuǎn)處構(gòu)成電容,導(dǎo)體接地等效于接到無(wú)窮遠(yuǎn)處,并與大地連接成整體。但是在射頻電路中,這個(gè)電容的容抗值就不是恒定的,如同我們?cè)凇对斀馍漕l電路中的電阻,電容和電感》介紹的一樣,電容首先呈容抗特性然后在諧振點(diǎn)出容抗和感抗平衡,之后呈現(xiàn)感抗特性。

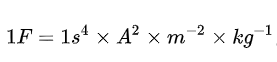

NO.2 電容的單位電容的單位:法拉(Farad),簡(jiǎn)稱法F,這個(gè)就是為了紀(jì)念偉大的法拉第先生。但是法拉是個(gè)很大的單位,究竟有多大呢?根據(jù)國(guó)際單位制的定義:1法拉等于秒的四次方安培的平方每千克每平方米。

當(dāng)1法拉的電容器上的電壓以1伏特每秒(1 V/s)的速度變化時(shí),就會(huì)產(chǎn)生1安培的電流。1法拉的電容上如果帶有1庫(kù)倫(1C)的電荷就會(huì)產(chǎn)生1伏特的勢(shì)能差。

當(dāng)電容應(yīng)用在射頻電路中時(shí),這個(gè)法拉就更大了,實(shí)際應(yīng)用中幾乎沒(méi)有直接用法拉這么大單位計(jì)量的電容器。

所以常用的電容單位通常有毫法(mF)、微法(μF)、納法(nF)和皮法(pF)等,他們之間的換算關(guān)系如下:

1法拉(F)

= 10^3毫法(mF)

=10^6微法(μF)

=10^9納法(nF)

=10^12皮法(pF)

NO.3 集成電容

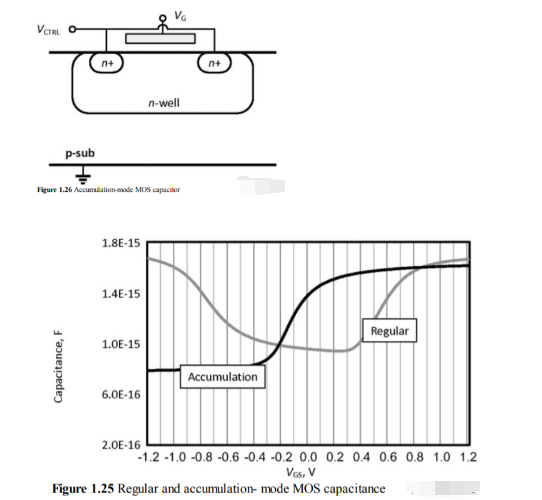

電容的種類很多,根據(jù)電容器的制作工藝可分為:CBB電容(聚乙烯),滌綸電容、瓷片電容、云母電容、獨(dú)石電容、電解電容、鉭電容等。書中詳細(xì)介紹了一種利用MOS晶體管的柵電容來(lái)實(shí)現(xiàn)的一種高密度的電容,但其電容值非線性,如下圖所示,截取了書中所示的一個(gè)40nm常規(guī)NMOS管電容與柵極電壓的仿真曲線。根據(jù)柵極電壓不同,NMOS晶體管可以工作在積累區(qū)(Vgs《0),耗盡區(qū)(0《Vgs《Vth)或者反型區(qū)(Vgs》Vth)。

文中介紹是在積累區(qū)或者反型區(qū),NMOS的電容值達(dá)到最大,近似等于Cox。但是這兩個(gè)區(qū),電容值最大。但是在反型區(qū),器件的偏置電壓應(yīng)該大于闕值電壓,這對(duì)于低電源電壓的場(chǎng)合不太適用,因此就有了下圖所示的積累型MOS電容,其電容特性曲線如下圖所示。

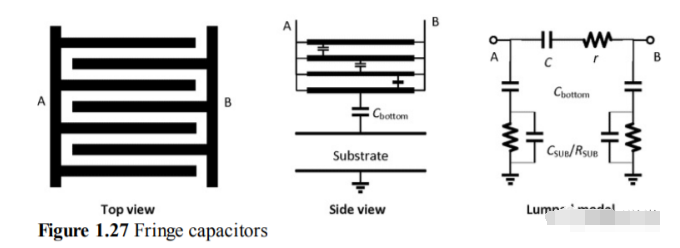

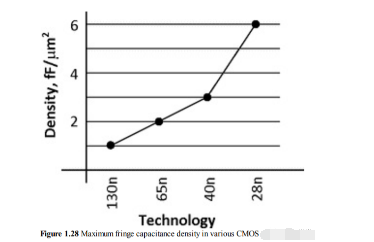

那么還有一種電容形式在CMOS工藝中較為常見(jiàn),即梳狀電容,因?yàn)樵贑MOS工藝中,金屬線可以靠的很近,獲得很強(qiáng)的邊緣電場(chǎng)。

CMOS相關(guān)工藝制作的梳狀電容在書中有比較詳細(xì)的介紹。在工藝所允許的最小空間內(nèi)走最小寬度的金屬線,構(gòu)成梳狀結(jié)構(gòu),連接在每一端的多層金屬放在各自的頂層,進(jìn)一步增加密度。

進(jìn)一步,利用MOS的柵極電容和梳狀電容相連,進(jìn)一步提高電場(chǎng)密度,增加電容值。

今天就學(xué)到這里,下次我們接著學(xué)射頻元件之電感部分。

責(zé)任編輯人:CC

-

電容

+關(guān)注

關(guān)注

100文章

6090瀏覽量

150796 -

集成電容

+關(guān)注

關(guān)注

0文章

5瀏覽量

7571

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

薄膜電容單位參數(shù)介紹

電容器的單位如何換算

電容的單位轉(zhuǎn)換以及計(jì)算公式的詳細(xì)介紹

電容器原理和計(jì)算公式及電容單位換算的介紹

電容的單位轉(zhuǎn)換及計(jì)算公式?的詳細(xì)介紹

電容單位用基本單位表示 電容器單位是用什么字母表示

電容單位換算1mf等于多少uf 電容單位轉(zhuǎn)換器的作用

電容的單位有哪些? 分別是?

電容的單位換算有哪些 電容的單位換算公式

電容容值如何表示?換算單位方法是什么?

什么是電容,電容的單位介紹

什么是電容,電容的單位介紹

評(píng)論